## FAQ for USB, ATA (Interface ICs) S1R72V series

|        | Q                                                                                | А                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Applicable to: *1 |     |     |     |     | '1 _ |     |

|--------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----|-----|-----|-----|------|-----|

|        |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V03               | V05 | V17 | V27 | V18 | C05  | H74 |

| CPU IF | /DMA                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |     |     |     |     |      |     |

| Q1-01  | •                                                                                | Some registers and bits are for FIFO access. Transfer data by the PIO interface using these bits and registers. Or, use DMA.                                                                                                                                                                                                                                                                                                                                   | 0                 | 0   | 0   | 0   | 0   | 0    | 0   |

| Q1-02  | Is the interrupt pin allowed to be wired OR with another LSI pin?                | The interrupt output can be set to Hi-Z/Low by mode setting. However, the Hi-Z is output using the Tri-state buffer; thus pull-up by the voltage exceeding the CVDD is not allowed.                                                                                                                                                                                                                                                                            | 0                 | 0   | 0   | 0   | 0   | 0    | 0   |

| Q1-03  | It is not possible to write to the CPU_Config register or<br>ClkSelect register. | Check the setting of ModeProtect register. ModeProtect register setting<br>enables or disables writing to the CPU_Config and ClkSelect register<br>values.                                                                                                                                                                                                                                                                                                     | 0                 | 0   | 0   | 0   | 0   | 0    | 0   |

| Q1-04  | Is the DMA data transfer to CPU possible without using the DACK pin?             | Yes, possible. For example, set:<br>DMA_Mode=1<br>DACK_Level=0: Pull up DACK pin (to inactive level).<br>CS_Mode=0<br>These settings allow DMA data transfer by setting the DMA source and<br>destination addresses to DMA0/1_Rd/WrData registers.                                                                                                                                                                                                             | 0                 | 0   | 0   | 0   | 0   | 0    | 0   |

| Q1-05  | Is the CPU controllable by 16-bit access only?                                   | <see a1-05=""></see>                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                 | 0   | 0   | 0   | 0   | 0    | 0   |

| Q1-06  | Please explain how to set the IC endians.                                        | Refer to the Appendix of the specification documents.<br>Detailed description is also given in the CPU Connection Guide.                                                                                                                                                                                                                                                                                                                                       | 0                 | 0   | 0   | 0   | 0   | 0    | 0   |

| Q1-07  | What is the CPU Cut Mode?                                                        | The CPU Cut Mode reduces the current consumption caused by<br>external factors while the LSI is in Sleep state. For example, the CPU<br>Cut Mode reduces current consumption by the CPU interface signals in<br>the Sleep state, inhibiting external signal inputs to the LSI's input pins.<br>Since this mode is intended to reduce the current consumption of input<br>pins, output pins such as the interrupt signal pin operate regardless of<br>the mode. | -                 | -   | 0   | 0   | 0   | -    | -   |

| Q1-08  | loop.                                                                            | Set the loop count to 5 times or more (7 times of more for V27).<br>RdRemainValid=1 is confirmed at least once by reading<br>FIFO_RdRemainH five times. Exercise caution as RdRemainVlid=1<br>is not always confirmed by the fifth read.                                                                                                                                                                                                                       | 0                 | 0   | 0   | 0   | 0   | 0    | 0   |

Yes, it is possible. However, exercise caution for the following two points when developing control softw

1. Register access

It is 16-bit access; thus when writing Address 0, data is simultaneously written to Address 1 as we

e.g. When writing data to register (Adrs N), data is also written to (Adrs N+1).

Adrs N Adrs N+1

2. Access to FIFO data (Ignore the following description if the IC has FIFO\_ByteWr registe

Take the following steps when writing odd-number byte data to FIF

(1) Do not let FIFO data be transferred (e.g. Disable USB data transfer by setting ForceNAK bit, et

(2) Add 1-byte dummy data at the top of odd-number byte/n[byte] data to write, and make it (n+1) even-number d

(3) Write (n+1) byte even-number data to FIFO using the FIFO\_Wr registe

(4) Read the 1-byte dummy data at the top using the FIFO\_ByteRd registe

e.g. If 5-byte odd-number data (AA~EE) need to be stored in

| DD       | EE       | Add dummy data at the top, and write 6-byte data, (Dummy, AA)(BB, CC)(DD, EE).                                                                                                  |

|----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BB       | CC       | (The left figure illustrates the FIFO status when step (3) mentioned above is performed)                                                                                        |

| Dummy    | AA       |                                                                                                                                                                                 |

|          |          |                                                                                                                                                                                 |

|          | ţ        |                                                                                                                                                                                 |

| DD       | EE       | Odd-number data is created in FIFO by reading out dummy data using FIFO_ByteRd reg                                                                                              |

| DD<br>BB | EE<br>CC | Odd-number data is created in FIFO by reading out dummy data using FIFO_ByteRd reg<br>(The left figure illustrates the FIFO status when step (4) mentioned above is performed.) |

reading out dummy data using FIFO\_ByteRd register. s when step (4) mentioned above is performed.)

To write data to FIFO by DMA, set the DMA\_Count register to odd number and perform DMA transf

e.g. If 5-byte odd-number data (AA~EE) need to be stored in FIFO

| EE | None |

|----|------|

| CC | DD   |

| AA | BB   |

Set DMA count to "5" and transfer (AA, BB) (CC, DD) (EE, xx) by DMA, then odd-number data is created within FIFO. The 6th byte "xx" data is not written to FIFO.

| IDE | IF |  |

|-----|----|--|

| Q2-01                                                                                                    | Is PIO data transfer over IDE interface possible without accessing registers?                  | There are two ways to access the IDE device:<br>- Use FIFO<br>- Access registers<br>For data transfer, FIFO is usable regardless of the IDE transfer modes,<br>PIO, DMA, or Ultra. To use FIFO, set the transfer counts and IDE_Go.       | 0 | 0 | - | - | - | 0 | 0 |

|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|---|

| Q2-02                                                                                                    | Are V03, V05, C05, and H74 connectable with 5V IDE interface drive?                            | V03 and H74 interface voltages are 3.3V, and thus not controllable by 5V drive.<br>Note: Some 3.3V interface drives have some 5V signals. They need to be converted to 3.3V.                                                              | 0 | 0 | - | - | - | 0 | 0 |

| Q2-03                                                                                                    | Is it possible to use with another IC by setting the IDE interface to Hi-Z?                    | Yes, possible. Output is disabled by setting IDE_Config_1, ActiveIDE bits to "0." Disable all the registers to control the PU and PD of IDE                                                                                               | 0 | 0 | - | - | - | 0 | 0 |

| Q2-04                                                                                                    | Please explain how to set pins when not using the IDE interface.                               | Set the logic levels of input and bi-directional pins using either one of<br>the following methods:<br>- Pull-up or pull-down on the board<br>- Use internal pull-up or pull-down resistors (Validate them by using<br>control registers) | 0 | 0 | - | - | - | 0 | 0 |

| Q2-05                                                                                                    | Is the CF card connectable with the IDE interface?                                             | Yes, it is connectable in True IDE Mode of CF card.                                                                                                                                                                                       | 0 | 0 | - | - | - | 0 | 0 |

| Q2-06                                                                                                    | Is it possible to transfer data between CPU and IDE independently while transferring USB data? | Yes, possible.                                                                                                                                                                                                                            | 0 | 0 | - | - | - | 0 | 0 |

| Q2-07                                                                                                    | Is it possible to transfer data between USB and IDE directly<br>via the internal FIFO?         | Direct data transfer is possible using the LSI internal FIFO. However, some operating systems do not allow such direct data transfer. <see a2-07=""></see>                                                                                | 0 | 0 | - | - | - | 0 | - |

| <a2-07< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></a2-07<> |                                                                                                |                                                                                                                                                                                                                                           |   |   |   |   |   |   |   |

|                                                                                                          |                                                                                                |                                                                                                                                                                                                                                           |   |   |   |   |   |   |   |

# USB Data Transfer

| 02R D                                                                                                        | ata Transfer                                                                                              |                                                                                                                                                                                                                                                                                                                                        |        |   |   |   |   |   |   |

|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---|---|---|---|---|---|

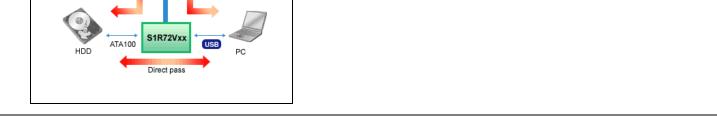

| Q3-01                                                                                                        | Is it possible to transfer data between USB and IDE directly<br>via the internal FIFO?                    | Direct data transfer is possible using the LSI internal FIFO.<br>To do this, however, the operating system must allow direct data<br>transfer between the USB and IDE devices. If this is not the case, you<br>need to prepare software that controls direct data transfer instead of the<br>operating system.<br><see a3-01=""></see> | ,<br>O | 0 | - | - | - | 0 | - |

| <a3-01< td=""><td>&gt;</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></a3-01<> | >                                                                                                         |                                                                                                                                                                                                                                                                                                                                        |        |   |   |   |   |   |   |

|                                                                                                              | HDD + ATA100 S1R72Vxx + USB PC + Direct pass                                                              |                                                                                                                                                                                                                                                                                                                                        |        |   |   |   |   |   |   |

|                                                                                                              |                                                                                                           |                                                                                                                                                                                                                                                                                                                                        |        |   |   |   |   |   | - |

| Q3-02                                                                                                        | USB?                                                                                                      | Yes, possible. Do not directly transfer IDE data to USB, but save the<br>processed data in the system memory first, and then transfer them to<br>USB.                                                                                                                                                                                  | 0      | 0 | - | - | - | 0 |   |

| Q3-03                                                                                                        | Is it possible to rewrite the system firmware on the ROM (flash memory) using USB?                        | Yes, possible by software developed by the customer.<br>A typical way to rewrite the flash using USB is to copy the system<br>program code to RAM first, and then run the program on RAM.                                                                                                                                              | 0      | 0 | 0 | 0 | 0 | 0 | - |

| Q3-04                                                                                                        | When using USB to send data, is it necessary to write data to FIFO every time one data packet is sent?    | No, not necessary. It is possible to write data to FIFO if it has available space, regardless of the packet data transfer.                                                                                                                                                                                                             | 0      | 0 | 0 | 0 | 0 | 0 | - |

| Q3-05                                                                                                        | Is it necessary to read data from FIFO every time one data packet is received when receiving data by USB? | No, not necessary. It is possible to read data if valid data exists in FIFO, regardless of the packet data reception.                                                                                                                                                                                                                  | 0      | 0 | 0 | 0 | 0 | 0 | - |

| Q3-06                                                                                                        | Is high-bandwidth isochronous data transfer supported?                                                    | No, high-bandwidth is not supported.                                                                                                                                                                                                                                                                                                   | О      | О | О | О | 0 | 0 | 1 |

| Q3-07                                                                                                        | Is OTG supported?                                                                                         | No, OTG is not supported.                                                                                                                                                                                                                                                                                                              | 0      | 0 | 0 | 0 | 0 | 0 | - |

| Q3-08                                                                                                        | Under what conditions do USB devices not respond to transactions?                                         | USB devices do not respond to transactions in the following cases:<br>- The device functions are not properly set.<br>- Destination address is not valid.<br>- Destination endpoint is not valid.<br>- Packet from the host has an error.                                                                                              | 0      | 0 | 0 | 0 | 0 | 0 | - |

## **USB Bus Line/Status**

| OSB B | us Line/Status                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |   |   |   |   |   |   |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|---|

| Q4-01 | Please explain how to handle unused USB port pins.                                                                                                                                                                                    | Leave DP, DM, R1, and VBUS pins all open. If with host functions, also leave VBUSEN and VBUSFLG pins open.                                                                                                                                                                                                                                                                                                                       | 0 | 0 | 0 | 0 | 0 | 0 | - |

| Q4-02 | When switching the device and host functions, the VBUS_Changed status is sometimes set even though no changes occur to VBUS pin. What caused this problem?                                                                            | If the port shared by host and device is switched as follows while the VBUS pin is kept high, the VBUS_Changed status is set:<br>Device => Host function (Change HostxDEVICE from "0" to "1")<br>Host => Device function (Change HostxDEVICE from "1" to "0")<br>This does not occur when VBUS pin is Low.<br>< <u>See A4-02&gt;</u>                                                                                             | - | 0 | 0 | 0 | 0 | 0 | - |

| Q4-03 | Is the VBUS_Changed status set, if the VBUS pin changes<br>its state from L to H or vice versa when the IC is used as a<br>host?                                                                                                      | It depends on the operation mode (1-port/2-port modes) of each IC.<br>Please refer to the table below.<br><see a4-03=""></see>                                                                                                                                                                                                                                                                                                   | - | 0 | 0 | 0 | 0 | 0 | - |

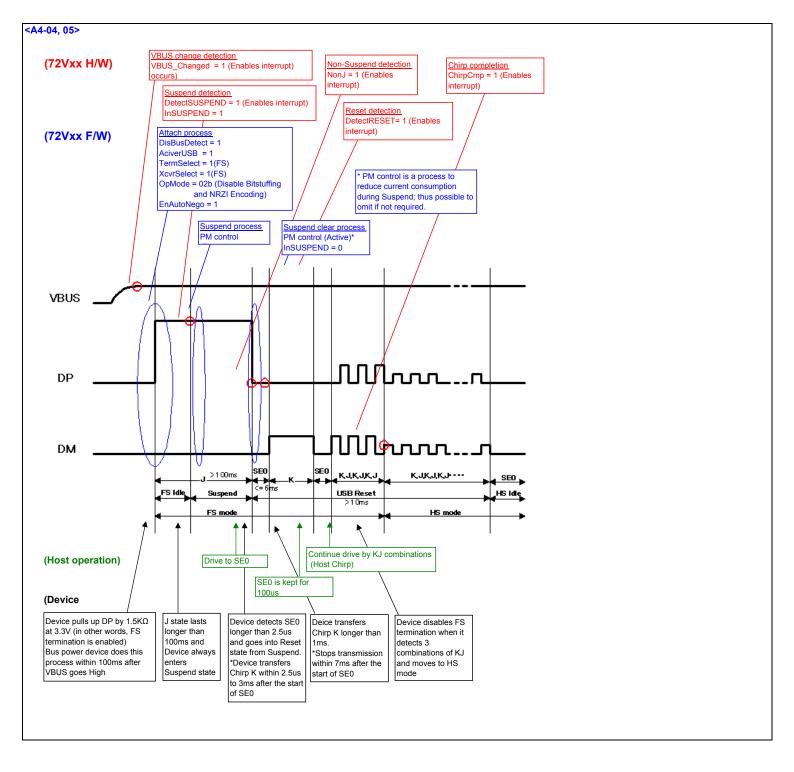

| Q4-04 | The USB Device is not properly recognized by the USB<br>Host.<br>In the Device Manager, "Unknown device" or only "Mass<br>Storage Class" not reflecting the descriptor is shown for the<br>USB controller. What caused this problem?. | When connected with a PC, the USB Device takes the following steps<br>to be recognized by the PC:<br>1. VBUS detection<br>2. DP pull-up<br>3. Chirp response to USB reset<br>4. Responds to standard requests (control transfer)<br>If "Unknown device" is shown, problems are likely to exist in process 3                                                                                                                      |   |   |   |   |   |   |   |

|       |                                                                                                                                                                                                                                       | or 4.<br>A packet is not transferred from the USB Host for a certain period of<br>time immediately after the DP is pulled up, and thus the LSI detects the<br>Suspend state first, and then gets ready for the USB reset later. If<br>power management is implemented during Suspend, such as OSC<br>halt, care must be taken to check if the OSC properly restarted its<br>operation immediately after the USB reset detection. | 0 | 0 | 0 | 0 | 0 | 0 | - |

|       |                                                                                                                                                                                                                                       | In case of the Mass Storage Class Device, it takes the following<br>additional steps:<br>5. Responds to Mass Storage Class request (Control transfer)<br>6. Receives and processes CBW (Command by bulk transfer)<br>7. Transfers CSW (status by bulk transfer)                                                                                                                                                                  |   |   |   |   |   |   |   |

|       |                                                                                                                                                                                                                                       | If the Host PC recognizes the USB Device only as "Mass Storage Class," problems are likely to exist in step 5, 6, or 7. <see 05="" a4-04,=""></see>                                                                                                                                                                                                                                                                              |   |   |   |   |   |   |   |

| Q4-05 | When connected with PC (Host), the device is recognized<br>as FS device, not HS device. What caused this problem?                                                                                                                     | <ol> <li>Check if USB driver is installed on the USB Host<br/>EHCI driver needs to be installed on the PC (USB Host).</li> <li>In the case of Windows 2000, right click "My Computer," choose<br/>"Hardware tab," display "Device Manager," and expand the USB<br/>controller. If "Standard Enhanced PCI to USB Host Controller" is<br/>shown, the EHCI driver is installed.</li> </ol>                                          |   |   |   |   |   |   |   |

|       |                                                                                                                                                                                                                                       | (2) Check if the USB Device outputs Device Chirp<br>USB Device needs to output Device Chirp (K state) within the specified<br>period of time after receiving USB RESET from USB Host. If this time<br>limit is not met, Host will not recognize the connected equipment as HS<br>Device. The specified time limits are as follows:                                                                                               |   |   |   |   |   |   |   |

|       |                                                                                                                                                                                                                                       | When the USB Device receives USB RESET during non-SUSPEND state (during HS operation):<br>3.1[msec] to 6[msec]                                                                                                                                                                                                                                                                                                                   | 0 | 0 | 0 | 0 | 0 | 0 | - |

|       |                                                                                                                                                                                                                                       | When the USB Device receives USB RESET during SUSPEND state:<br>2.5[usec] to 6[msec]                                                                                                                                                                                                                                                                                                                                             |   |   |   |   |   |   |   |

|       |                                                                                                                                                                                                                                       | For the time limits during FS operation and other detailed information, please refer to EL-27 and -28 in "USB-IF USB2.0 Electrical Test Specification Ver.1.03" (This document is downloadable from http://www.usb.org/developers/docs/.) <see 05="" a4-04,=""></see>                                                                                                                                                            |   |   |   |   |   |   |   |

| Q4-06 | Which processes of USB Device firmware need to meet timing constraints?                                                                                                                                                               | 1. Process when USB reset occurs during USB Suspend<br>USB_Control.InSUSPEND bit needs to be cleared within 6ms. If not<br>cleared within this time limit, the USB device is not recognized as HS<br>but FS.                                                                                                                                                                                                                     |   |   |   |   |   |   |   |

|       |                                                                                                                                                                                                                                       | 2. Process of Attach after detecting VBUS<br>DP needs to be pulled up within 100ms after VBUS goes "High" only<br>when using the USB Device as bus power.                                                                                                                                                                                                                                                                        |   |   |   |   |   |   |   |

|       |                                                                                                                                                                                                                                       | 3. Response time of control transfer<br>Time limit to return data with data stage IN = 500[msec]<br>Time limit to receive data with data stage OUT = 5[sec]<br>Time limit to start status stage = 50[msec]                                                                                                                                                                                                                       | 0 | 0 | 0 | 0 | 0 | 0 | - |

|       |                                                                                                                                                                                                                                       | 4. Time limit to move to test mode<br>Test mode needs to be started within 3[msec] after the completion of<br>status stage.                                                                                                                                                                                                                                                                                                      |   |   |   |   |   |   |   |

|       |                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |   |   |   |   |   |   |

| Q4-07 | Do short-circuited DP and DM affect the LSI functions<br>when VBUS power supply is used for battery charge?                                                                                                            | No, short circuit is no problem. However, USB communications are not allowed.                                                                                                                                                                                                                                                                                                                                                                                                           | 0 | 0 | 0 | 0 | 0 | 0 | - |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|---|

| Q4-08 | Is it all right to connect a PC to the Device port while the<br>LSI is powered off?<br>Or is it all right to connect a USB Device to the Host port?<br>Also, do DP and DM pins go Hi-Z when the LSI is powered<br>off? | DP and DM pins do not go Hi-Z. But there should be no problem:<br>In Device Mode:<br>DP and DM pins on the Host side are specified Low (SE0); thus no<br>problem.<br>VBUS pin has a pull-down resister within the LSI and the resister<br>consumes current, but does not damage or degrades the pin.<br>In Host Mode:<br>DP and DM pins are pulled down by LSI's own host termination. This<br>retains unless the VBUS is supplied to Device side; thus no problem.                     | 0 | 0 | 0 | 0 | 0 | 0 | - |

| Q4-09 | If the Host has two USB ports, is it possible to use them simultaneously?                                                                                                                                              | V18 allows two equipment to be physically connected to both ports as USB devices and allows simultaneous data transfer.<br>C05 also allows two equipment to be physically connected to both ports as USB devices, but does not allow simultaneous data transfer.<br>V05, when used in 2-port mode, allows only one equipment to be used as a USB device.<br>C05 and V05, when used in 1-port mode, do not allow two equipment to be connected simultaneously.<br>< <b>See A4-09&gt;</b> |   | 0 | - | - | 0 | 0 | _ |

# <A4-02>

| IC  | Port used by both Host and<br>Device | Mode           | VBUS_Changed status |  |  |

|-----|--------------------------------------|----------------|---------------------|--|--|

| VOF | Dent D                               | 2-port mode    | Not set             |  |  |

| V05 | Port B                               | 1-port mode Se |                     |  |  |

| V17 | Single port                          | -              | Set                 |  |  |

| V27 | Single port                          | -              | Set                 |  |  |

| V18 | Port O                               | -              | Set                 |  |  |

| COF | Port B                               | 2-port mode    | Not set             |  |  |

| C05 | FULLB                                | 1-port mode    | Set                 |  |  |

<A4-03>

| IC  | Mode             | VBUS_Changed Status |

|-----|------------------|---------------------|

| VOE | 2-port mode      | Set                 |

| V05 | 1-port mode      | Not set             |

| V17 | -                | Not set             |

| V27 | -                | Not set             |

| V18 | Host/Host (*1)   | Not set             |

|     | Device/Host (*1) | Set                 |

|     | 2-port mode      | Set                 |

| C05 | 1-port mode      | Not set             |

(\*1) Indicates function state (Port0/Port1)

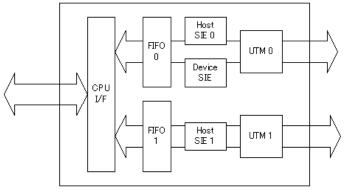

## <A4-09>

V18:

Each port has FIFO and is capable to transfer data independently.

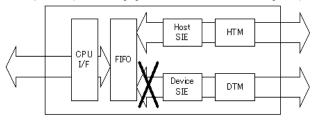

#### C05:

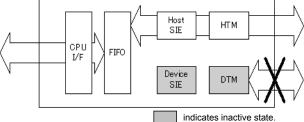

Host and Device FIFOs are mutually exclusive. Simultaneous data transfer from multiple ports is not possible. (The following figure illustrates the Host transferring data.)

### V05:

Host and Device cannot be simultaneously active (supplied clock). However, an asynchronous interrupt like VBUS\_Changed is usable. (The following figure illustrates the Host in active state.)

indicates inactive state.

| Q4-10 | Is it possible to set DP and DM pins to Hi-Z?                                        | Yes, it is possible to set the DP and DM pins to Hi-Z by the following<br>register setting:<br>XcvrControl.OpMode* = 01b (Non-Driving)<br>Use this setting when not connected by a cable unless otherwise<br>specified. Even when a cable is used, use this setting to deliberately<br>detach the equipment. However, because the DP and DM pins are in<br>the Hi-Z state, bus activity detection function is invalid except VBUS.<br>*D_XcvrControl, and H_XcvrControl names are used for other LSIs. | 0 | 0 | 0 | 0 | 0 | 0 | - |

|-------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|---|

| Q4-11 | Does the power supply to VBUS pin always need to be 5V?                              | No, does not need to be 5V, as long as it is higher than the H-level trigger voltage described in the DC input characteristics section of the specifications.                                                                                                                                                                                                                                                                                                                                          | 0 | 0 | 0 | 0 | 0 | 0 | - |

| Q4-12 | If a common mode choke coil is inserted in DP and DM lines, what effect is expected? | Common mode choke coil reduces the current flowing in the same direction as differential signal line and prevents the occurrence of common mode noise. Phase and voltage differences of DP and DM signals are expected to be improved. It is not directly related to the improvement of eye pattern opening.                                                                                                                                                                                           | 0 | 0 | 0 | 0 | 0 | 0 | _ |

| Q4-13 | Is it all right to connect USB Host or Device when the IC is powered off?            | No problem.<br>When USB Host is connected:<br>DP and DM pins are pulled down on the USB Host side. VBUS voltage<br>is applied to VBUS pin (normally about 5V) but does not damage the<br>pin. However, about 40uA current flows to VBUS pin from the USB<br>Host due to the internal pull-down register of 125 k $\Omega$ , (Min. 110k $\Omega$ ; Max<br>150k $\Omega$ .)<br>When USB Device is connected:                                                                                             |   | 0 | 0 | 0 | 0 | 0 | - |

|       |                                                                                      | DP and DM pins on the Host side are in the Hi-Z state; VBUS is not output and thus there should be no problem.                                                                                                                                                                                                                                                                                                                                                                                         |   |   |   |   |   |   |   |

| Q4-14 | Are the $10\Omega$ resistor and 1µF capacitor required as shown<br>in the recommended circuit around the VBUS pin? Is it<br>possible to change these resistance and capacitance<br>values? | <ul> <li>Yes, required.</li> <li>These are to protect the IC from the surge-like excessive voltage from the VBUS pin. These values are determined based on Epson's evaluation results of many different products on the market. If desired to change the values, pay attention to the following points:</li> <li>Voltage applied to VBUS pin should not exceed the absolute maximum rating (6V)</li> <li>VBUS pin is internally pulled down by 125kΩ (min. 110kΩ, max. 150kΩ), and thus its input level determined by the ratio to the external resistance must exceed the H-level trigger voltage of VBUS pin.</li> </ul> | 0 | 0 | 0 | 0 | 0 | 0 | - |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|---|

| Q4-15 | Is the VBUS pin on the IC for supplying power from the USB Host?                                                                                                                           | VBUS pin is not a pin to supply power to the IC.<br>The pin is used to detect the connection with USB Host and it is<br>internally pulled down by $125k\Omega$ (Min. $110k\Omega$ ; Max. $150k\Omega$ ) resistance.<br>When connected with USB Host, it consumes the amount of current<br>corresponding to its resistance.                                                                                                                                                                                                                                                                                                 | 0 | 0 | 0 | 0 | 0 | 0 | - |

|       | Design / External Components                                                                                                                                                               | Descendings of whether as not there are unused functions by starting it is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |   |   |   |   |   |   |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|---|

| Q5-01 | Are there any decoupling capacitors possible to omit?                                                                                                                                      | Regardless of whether or not there are unused function blocks, it is recommended to use decoupling capacitors for all power supply pins from the view point of stable power supply.                                                                                                                                                                                                                                                                                                                                                                             | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Q5-02 | Is it all right to use a cable to connect the USB connector with the board where a USB controller IC is mounted?                                                                           | It may degrade the signal integrity and thus not recommended.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0 | 0 | 0 | 0 | 0 | 0 | - |

| Q5-03 | Are there any points to pay attention when selecting an external VBUS power switch?                                                                                                        | Switches capable of preventing reverse current are recommended.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | - | 0 | 0 | 0 | 0 | 0 | - |

| Q5-04 | Does the resistor connected to R1 pin need to be<br>6.2 <b>kΩ</b> ±1%?                                                                                                                     | Yes. It is the resistor to generate the reference current that determines<br>the USB analog circuit characteristics. Too much margin will affect the<br>analog characteristics, and thus it is recommended to meet the<br>specified value.                                                                                                                                                                                                                                                                                                                      | 0 | 0 | 0 | 0 | 0 | 0 | - |

| Q5-05 | Are the $10\Omega$ resistor and 1uF capacitor required as shown<br>in the recommended circuit around the VBUS pin? Is it<br>possible to change these resistance and capacitance<br>values? | Yes, required.<br>These are to protect the IC from the surge-like excessive voltage from<br>the VBUS pin. These values are determined based on Epson's<br>evaluation results of a variety of products on the market. If desired to<br>change the values, pay attention to the following points:<br>- Voltage applied to VBUS pin should not exceed the absolute<br>maximum rating (6V)<br>- VBUS pin is internally pulled down to $125k\Omega(min110k\Omega, max150k\Omega)$ , and thus its input level must exceed the H-level trigger<br>voltage of VBUS pin. | 0 | 0 | 0 | 0 | 0 | 0 | - |

| Q5-06 | Please explain how to handle unused USB port pins.                                                                                                                                         | Leave DP, DM, R1, and VBUS pins all open. If with host functions, also leave VBUSEN and VBUSFLG pins open.                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0 | 0 | 0 | 0 | 0 | 0 | - |

| Q5-07 | Please explain how to handle the CLKIN pin when<br>connecting a crystal oscillator with XI and XO pins.                                                                                    | When using a crystal oscillator, connect the CLKIN pin with GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | - | - | 0 | 0 | - | - | - |

| Q5-08 | Please explain how to handle XI and XO pins when inputting an external clock to CLKIN pin.                                                                                                 | When clock is directly input to CLKIN pin, connect the XI pin with GND and leave the XO pin open.                                                                                                                                                                                                                                                                                                                                                                                                                                                               | - | - | 0 | 0 | - | - | - |

| Q5-09 | When inputting an external clock to CLKIN pin, what AC characteristics and amplitude level need to be met by the clock?                                                                    | When the clock is directly input to CLKIN pin, the clock needs to meet the same AC characteristics as the crystal oscillator. The frequency accuracy=±100ppm, Duty=45% to 55%. The amplitude level needs to be the same level of voltage supplied to the CVDD pin. (For more information, see "DC characteristics" in the data sheet.)                                                                                                                                                                                                                          | - | - | 0 | 0 | - | - | - |

| Q5-10 | Please explain how to set the IC endians.                                                                                                                                                  | Refer to the Appendix of the specification documents.<br>Detailed description is also given in the CPU Connection Guide.                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Q5-11 | If a common mode choke coil is inserted in DP and DM lines, what effect is expected?                                                                                                       | Common mode choke coil reduces the current flowing in the same direction as differential signal line and prevents the occurrence of common mode noise. Phase and voltage differences of DP and DM signals are expected to be improved. It is not directly related to the improvement of eye pattern opening.                                                                                                                                                                                                                                                    | 0 | 0 | 0 | 0 | 0 | 0 | - |

# Crystal / Clock / Power Management

| Q6-01 | What frequency accuracy is required for the crystal oscillator to use?                                                  | USB2.0 High-Speed frequency accuracy is defined ±500ppm. The USB signal waveform is significantly affected by the input clock jitter and frequency accuracy, and thus Epson recommends a crystal oscillator with frequency accuracy within ±100ppm to ensure the signal integrity of end products.                                        | 0 | 0 | 0 | 0 | 0 | 0 | - |

|-------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|---|

| Q6-02 | The crystal oscillator does not oscillate though the IC is powered on.                                                  | The initial state of the IC when powered on is the Sleep Mode where th<br>oscillator is inactive. To release the Sleep Mode, refer to Chapter 4 in<br>the CPU Connection Guide for each IC.                                                                                                                                               | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Q6-03 | Please explain how to handle the CLKIN pin when<br>connecting a crystal oscillator with XI and XO pins.                 | When using a crystal oscillator, connect the CLKIN pin with GND.                                                                                                                                                                                                                                                                          | - | - | 0 | 0 | - | - | - |

| Q6-04 | Please explain how to handle XI and XO pins when inputting an external clock to CLKIN pin.                              | When clock is directly input to CLKIN pin, connect the XI pin with GND and leave the XO pin open.                                                                                                                                                                                                                                         | - | - | 0 | 0 | - | - | - |

| Q6-05 | When inputting an external clock to CLKIN pin, what AC characteristics and amplitude level need to be met by the clock? | When the clock is directly input to CLKIN pin, the clock needs to meet the same AC characteristics as the crystal oscillator. The frequency accuracy=±100ppm, Duty=45% to 55%. The amplitude level needs to be the same level as the voltage supplied to the CVDD pin. (For mor information, see "DC characteristics" in the data sheet.) |   | - | 0 | 0 | - | - | - |

| Q6-06 | Is it possible to use a ceramic oscillator instead of a crystal | As for ceramic oscillators, Murata Manufacturing is now verifying the |   |   |   |   |   |   |   |

|-------|-----------------------------------------------------------------|-----------------------------------------------------------------------|---|---|---|---|---|---|---|

|       | oscillator?                                                     | operation using Ceralock. For detailed information, please contact    | 0 | 0 | 0 | 0 | 0 | 0 | - |

|       |                                                                 | Murata.                                                               | - |   | - |   | - |   |   |

| Power | Supply                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |   |   |   |   |   |   |

|-------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|---|

| Q7-01 | What is the IC consumption current?                                                                                            | Please refer to the consumption current measurement data in the listing<br>of related materials. For data not found in the listing, please contact<br>EpsonUSBIC@exc.epson.co.jp.                                                                                                                                                                                                                                                                                                                                              | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Q7-02 | Is it possible to power off only this IC whille USB is not<br>used? What are the status of pins when the IC is powered<br>off? | No, it is not possible to power off this IC only. The IC needs to be<br>always powered on because the pins will not go Hi-Z. Current will flow<br>towards power supply pins by the internal elements to protect each pin.                                                                                                                                                                                                                                                                                                      |   | 0 | 0 | 0 | 0 | 0 | 0 |

| Q7-03 | Is it all right to connect USB Host or Device when the IC is powered off?                                                      | No problem.<br>When USB Host is connected:<br>DP and DM pins are pulled down on the USB Host side. VBUS voltage<br>is applied to VBUS pin (normally about 5V) but does not damage the<br>pin. However, about 40uA current flows to VBUS pin from the USB<br>Host due to the internal pull-down register of 125 k $\Omega$ (Min. 110k $\Omega$ ; Max.<br>150k $\Omega$ ).<br>When USB Device is connected:<br>DP and DM pins on the Host side are in the Hi-Z state; VBUS is not<br>output and thus there should be no problem. |   | 0 | 0 | 0 | 0 | 0 | - |

| Q7-04 | Multiple power supplies exist. Are there any constraints on the power-on and -off sequences?                                   | Yes. Please follow the power-on and -off sequences described in the data sheet.                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Q7-05 | The specified power-on and -off sequences are not possibl to follow. Are there any other allowable sequences or conditions?    | If power-on and -off sequences are completed within a second, no<br>specific sequences are required to follow                                                                                                                                                                                                                                                                                                                                                                                                                  | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Q7-06 | Is it all right to use the same power supply as LVDD (1.8V)<br>or HVDD (3.3V) for CVDD (1.8/3.3V)?                             | Yes, it is all right.<br>However, exercise caution as LVDD is susceptible to noise that may<br>affect the quality of USB eye patterns.                                                                                                                                                                                                                                                                                                                                                                                         | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Q7-07 | Is the VBUS pin on the IC for supplying power from the USB Host?                                                               | The VBUS pin is not a pin to supply power to the IC.<br>The pin is used to detect the connection with USB Host and internally<br>pulled down by $125k\Omega$ (Min. $110k\Omega$ ; Max. $150k\Omega$ ) resistance.<br>When connected with USB Host, it consumes the amount of current<br>corresponding to its resistance.                                                                                                                                                                                                       | 0 | 0 | 0 | 0 | 0 | 0 | - |