## **CMOS 8-BIT SINGLE CHIP MICROCOMPUTER** S1C88816 Technical Manual S1C88816 Technical Hardware

### Revisions and Additions for this manual

| Chapter  | Section | Page | Item                      | Contents                 |

|----------|---------|------|---------------------------|--------------------------|

| 1        | 1.1     | 1    | Table 1.1.1 Main features | The package was changed. |

|          | 1.3     | 3    | Pin Layout Diagram        |                          |

|          | 1.4     | 5    | Mask Option               | Explanation was added.   |

| 5        | 5.10.12 | 87   | Programming notes         | Item (6) was added.      |

| 8        | 8.1     | 156  | Plastic Package           | The package was changed. |

| Appendix |         | 162  | Appendix                  | The chapter was added.   |

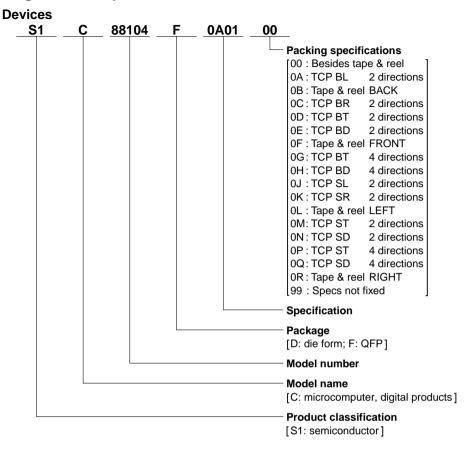

### Configuration of product number

### Contents

| 1 | INT | TRODUCTION                                                                                                     | 1  |

|---|-----|----------------------------------------------------------------------------------------------------------------|----|

|   | 1.1 | Features                                                                                                       | 1  |

|   | 1.2 | Block Diagram                                                                                                  | 2  |

|   | 1.3 | Pin Layout Diagram                                                                                             | 3  |

|   | 1.4 | Mask Option                                                                                                    | 5  |

| 2 | PO  | WER SUPPLY                                                                                                     | 7  |

|   | 2.1 | Operating Voltage                                                                                              | 7  |

|   | 2.2 | Internal Power Supply Circuit                                                                                  | 7  |

|   | 2.3 | Heavy Load Protection Mode                                                                                     | 8  |

| 3 | CPl | U AND MEMORY CONFIGURATION                                                                                     | 9  |

|   | 3.1 | CPU                                                                                                            | 9  |

|   | 3.2 | Internal Memory                                                                                                |    |

|   |     | 3.2.1 ROM                                                                                                      |    |

|   |     | 3.2.2 RAM                                                                                                      |    |

|   |     | 3.2.3 I/O memory                                                                                               |    |

|   | 2.2 | 3.2.4 Display memory                                                                                           |    |

|   | 3.3 | Exception Processing Vectors                                                                                   |    |

|   | 3.4 | CC (Customized Condition Flag)                                                                                 |    |

| 4 | INI | TIAL RESET                                                                                                     | 11 |

|   | 4.1 | Initial Reset Factors                                                                                          |    |

|   |     | 4.1.1 RESET terminal                                                                                           |    |

|   |     | 4.1.2 Simultaneous LOW level input at input port terminals K00–K034.1.3 Supply voltage detection (SVD) circuit |    |

|   |     | 4.1.4 Initial reset sequence                                                                                   |    |

|   | 4.2 | Initial Settings After Initial Reset                                                                           |    |

|   | 4.3 | Programming Note                                                                                               |    |

| 5 | PEI | RIPHERAL CIRCUITS AND THEIR OPERATION                                                                          | 14 |

|   | 5.1 | I/O Memory Map                                                                                                 | 14 |

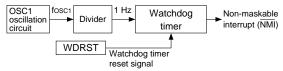

|   | 5.2 | Watchdog Timer                                                                                                 |    |

|   |     | 5.2.1 Configuration of watchdog timer                                                                          |    |

|   |     | 5.2.2 Interrupt function                                                                                       | 25 |

|   |     | 5.2.3 I/O memory for watchdog timer                                                                            |    |

|   |     | 5.2.4 Programming notes                                                                                        |    |

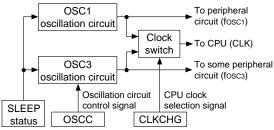

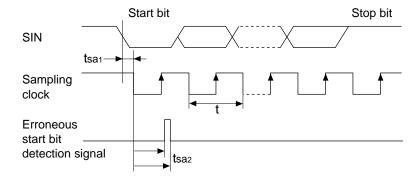

|   | 5.3 | Oscillation Circuits and Operating Mode                                                                        |    |

|   |     | 5.3.1 Configuration of oscillation circuits                                                                    |    |

|   |     | 5.3.2 Mask option                                                                                              |    |

|   |     | 5.3.4 OSC3 oscillation circuit                                                                                 |    |

|   |     | 5.3.5 Operating mode                                                                                           |    |

|   |     | 5.3.6 Switching the CPU clocks                                                                                 |    |

|   |     | 5.3.7 I/O memory for oscillation circuit                                                                       |    |

|   |     | 5.3.8 Programming notes                                                                                        | 30 |

### **CONTENTS**

| 5.4  | Input Ports (K ports)                                  |    |

|------|--------------------------------------------------------|----|

|      | 5.4.1 Configuration of input ports                     |    |

|      | 5.4.2 Mask option                                      |    |

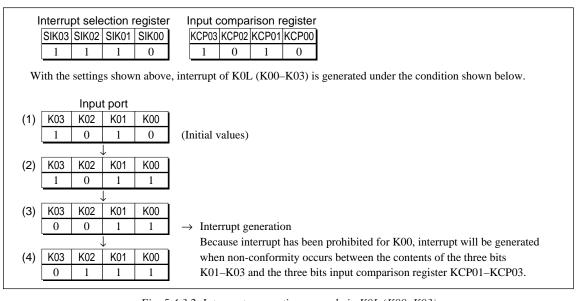

|      | 5.4.3 Interrupt function and input comparison register |    |

|      | 5.4.4 I/O memory for input ports                       |    |

|      | 5.4.5 Programming note                                 | 36 |

| 5.5  | Output Ports (R ports)                                 | 37 |

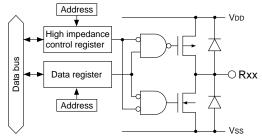

|      | 5.5.1 Configuration of output ports                    |    |

|      | 5.5.2 Mask option                                      |    |

|      | 5.5.3 High impedance control                           | 37 |

|      | 5.5.4 DC output                                        | 37 |

|      | 5.5.5 Special output                                   |    |

|      | 5.5.6 I/O memory for output ports                      | 40 |

|      | 5.5.7 Programming notes                                |    |

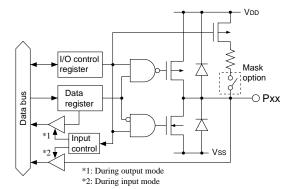

| 5.6  | I/O Ports (P ports)                                    | 44 |

|      | 5.6.1 Configuration of I/O ports                       |    |

|      | 5.6.2 Mask option                                      | 44 |

|      | 5.6.3 I/O control registers and I/O mode               | 45 |

|      | 5.6.4 I/O memory for I/O ports                         | 45 |

|      | 5.6.5 Programming note                                 | 46 |

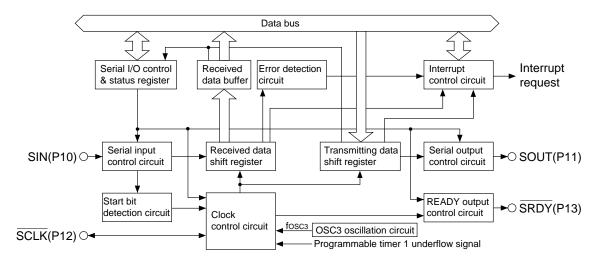

| 5.7  | Serial Interface                                       | 47 |

| .,   | 5.7.1 Configuration of serial interface                |    |

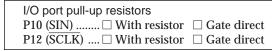

|      | 5.7.2 Mask option                                      |    |

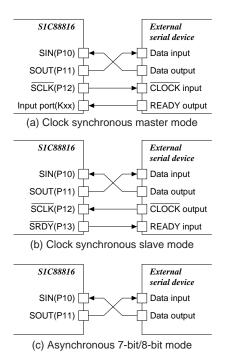

|      | 5.7.3 Transfer modes                                   |    |

|      | 5.7.4 Clock source                                     |    |

|      | 5.7.5 Transmit-receive control                         | 50 |

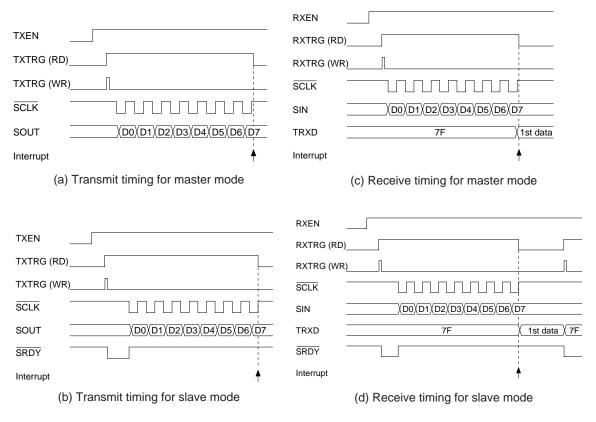

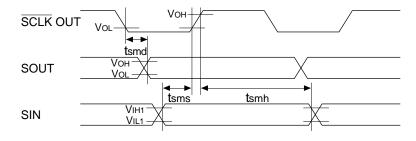

|      | 5.7.6 Operation of clock synchronous transfer          | 51 |

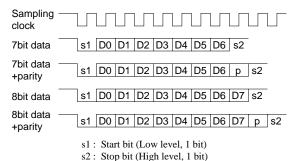

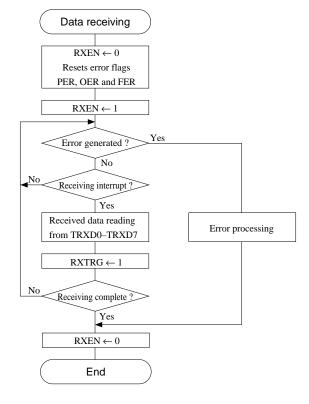

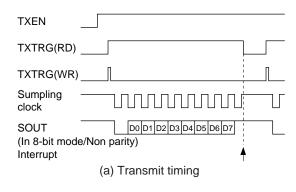

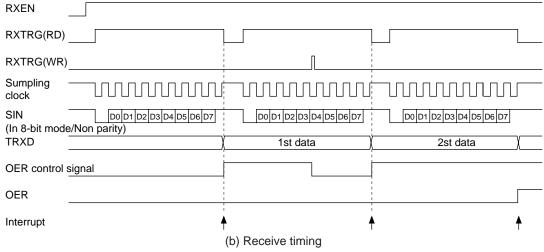

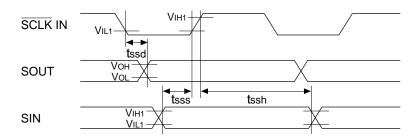

|      | 5.7.7 Operation of asynchronous transfer               | 55 |

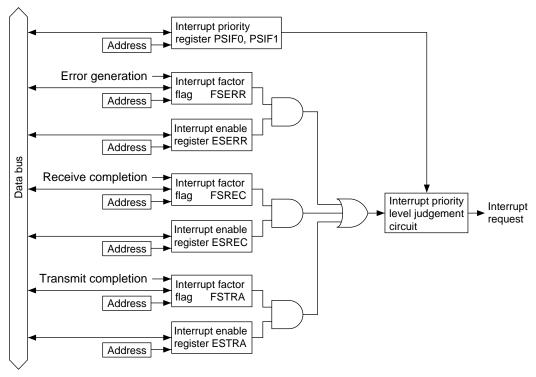

|      | 5.7.8 Interrupt function                               | 59 |

|      | 5.7.9 I/O memory for serial interface                  |    |

|      | 5.7.10 Programming notes                               | 65 |

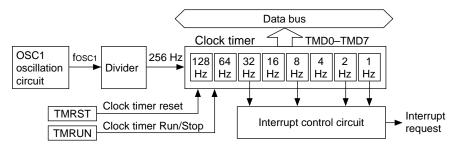

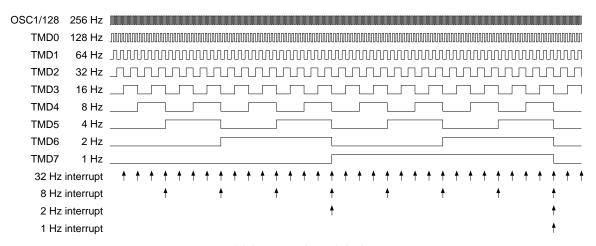

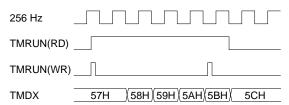

| 5.8  | Clock Timer                                            | 66 |

|      | 5.8.1 Configuration of clock timer                     |    |

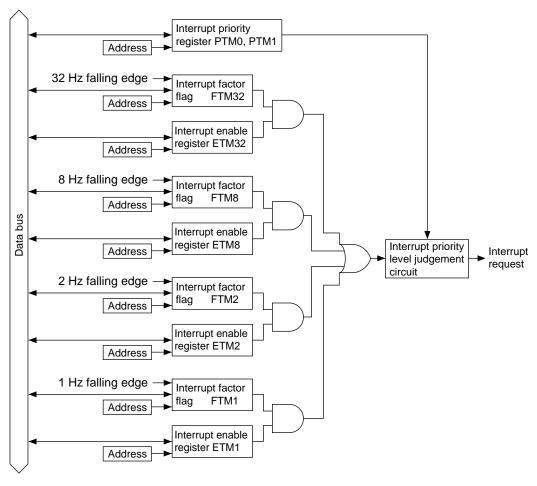

|      | 5.8.2 Interrupt function                               |    |

|      | 5.8.3 I/O memory for clock timer                       |    |

|      | 5.8.4 Programming notes                                |    |

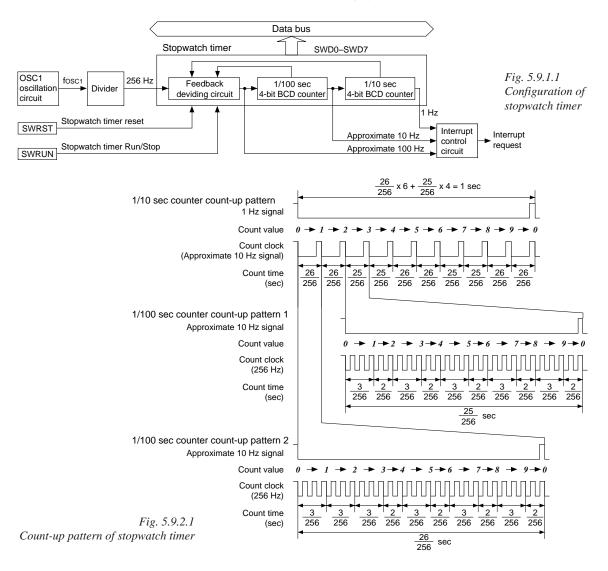

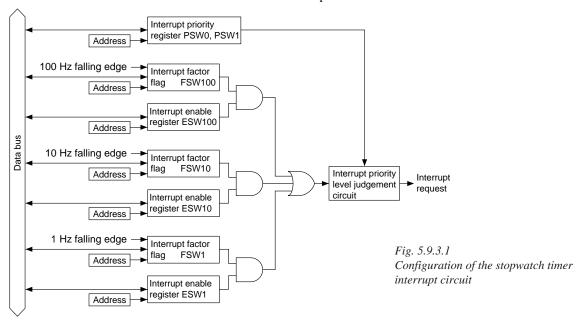

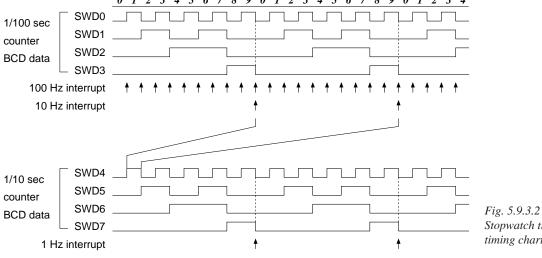

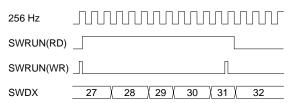

| 5.9  | Stopwatch Timer                                        | 71 |

| 3.7  | 5.9.1 Configuration of stopwatch timer                 |    |

|      | 5.9.2 Count up pattern                                 |    |

|      | 5.9.3 Interrupt function                               |    |

|      | 5.9.4 I/O memory for stopwatch timer                   |    |

|      | 5.9.5 Programming notes                                |    |

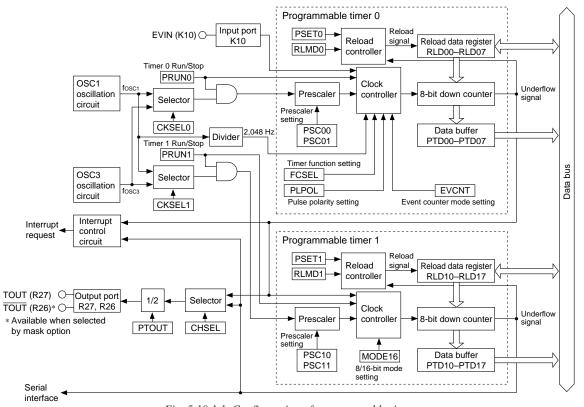

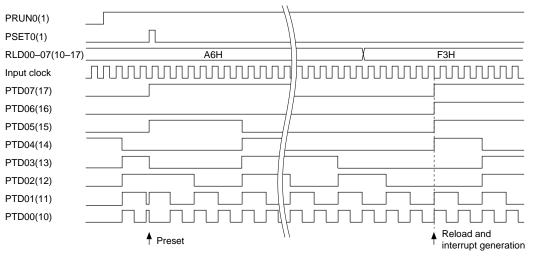

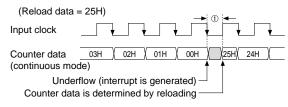

| 5.10 | Programmable Timer                                     |    |

| 3.10 | 5.10.1 Configuration of programmable timer             |    |

|      | 5.10.2 Mask option                                     |    |

|      | 5.10.3 Count operation and setting basic mode          |    |

|      | 5.10.4 Setting of input clock                          |    |

|      | 5.10.5 Timer mode                                      |    |

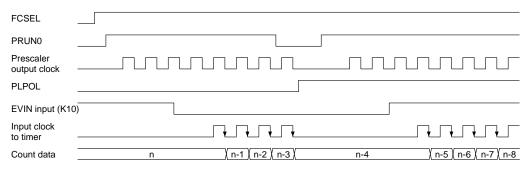

|      | 5.10.6 Event counter mode                              |    |

|      | 5.10.7 Pulse width measurement timer mode              |    |

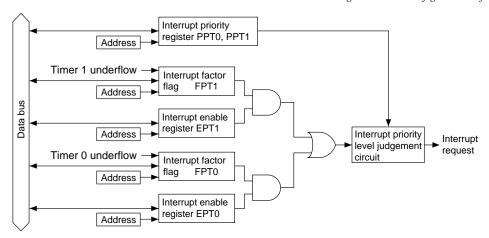

|      | 5.10.8 Interrupt function                              |    |

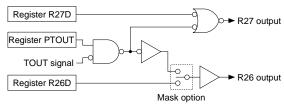

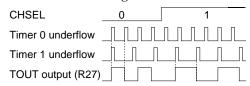

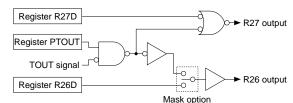

|      | 5.10.9 Setting of TOUT output                          |    |

|      | 5.10.10 Transmission rate setting of serial interface  |    |

|      | 5.10.11 I/O memory for programmable timer              | 82 |

|      | 5.10.12 Programming notes                              | 87 |

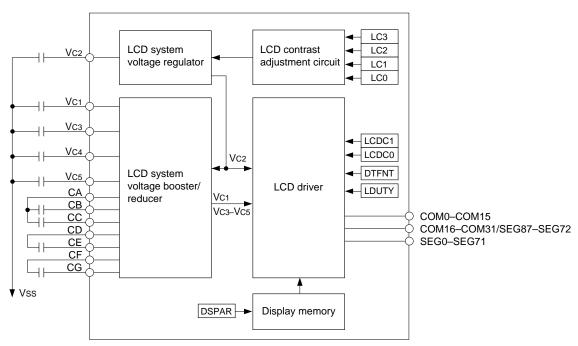

|   | 5.11 | LCD Controller                                                     |     |

|---|------|--------------------------------------------------------------------|-----|

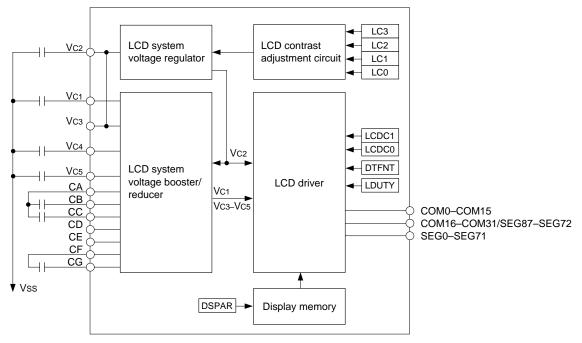

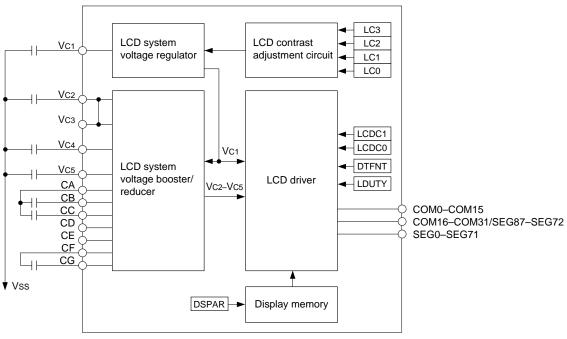

|   |      | 5.11.1 Configuration of LCD controller                             |     |

|   |      | 5.11.2 Mask option                                                 |     |

|   |      | 5.11.3 LCD power supply<br>5.11.4 LCD driver                       |     |

|   |      | 5.11.5 Display memory                                              |     |

|   |      | 5.11.6 Display control                                             |     |

|   |      | 5.11.7 I/O memory for LCD controller                               |     |

|   |      | 5.11.8 Programming note                                            |     |

|   | 5.12 | Sound Generator                                                    |     |

|   |      | 5.12.1 Configuration of sound generator                            |     |

|   |      | 5.12.2 Mask option                                                 |     |

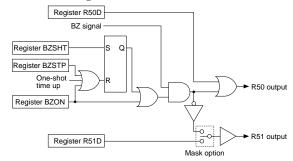

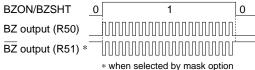

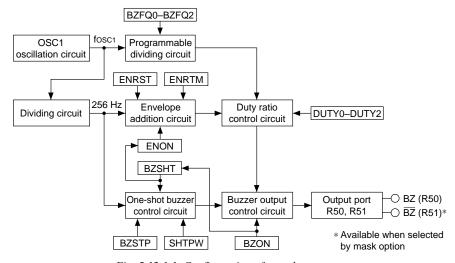

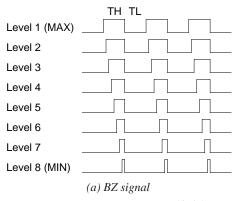

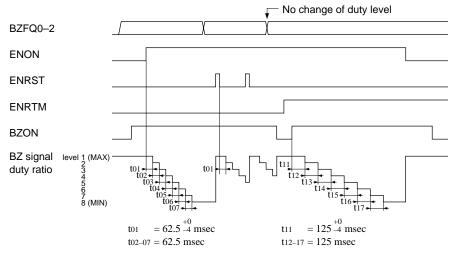

|   |      | 5.12.3 Control of buzzer output                                    |     |

|   |      | 5.12.5 Digital envelope                                            |     |

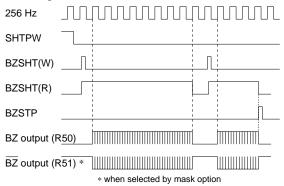

|   |      | 5.12.6 One-shot output                                             |     |

|   |      | 5.12.7 I/O memory for sound generator                              |     |

|   |      | 5.12.8 Programming notes                                           | 108 |

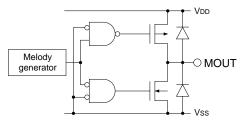

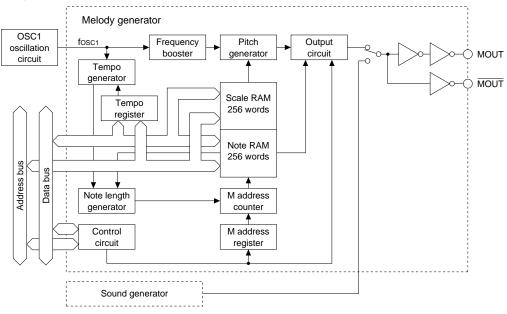

|   | 5.13 | Melody Generator                                                   | 109 |

|   |      | 5.13.1 Features and configuration of melody generator              |     |

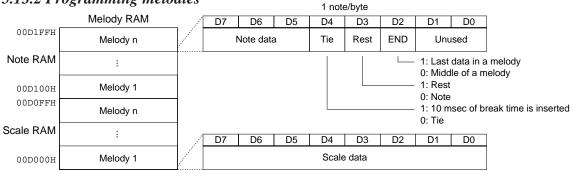

|   |      | 5.13.2 Programming melodies                                        |     |

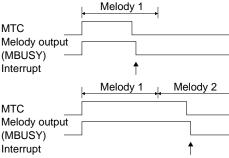

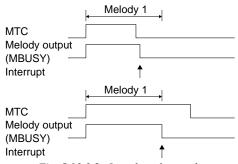

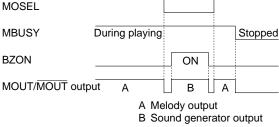

|   |      | 5.13.3 Controlling melody output                                   |     |

|   |      | 5.13.4 Interrupt function                                          |     |

|   |      | 5.13.6 Programming notes                                           |     |

|   | 5.14 | Supply Voltage Detection (SVD) Circuit                             |     |

|   | 3.14 | 5.14.1 Configuration of SVD circuit                                |     |

|   |      | 5.14.2 Operation of SVD circuit                                    |     |

|   |      | 5.14.3 I/O memory for SVD circuit                                  |     |

|   |      | 5.14.4 Programming notes                                           |     |

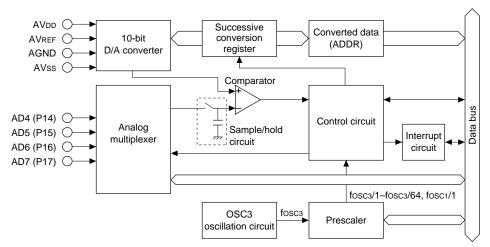

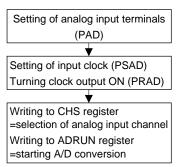

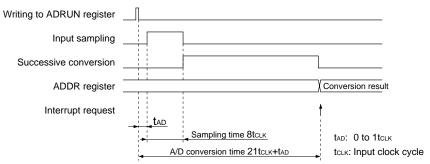

|   | 5.15 | A/D Converter                                                      | 121 |

|   |      | 5.15.1 Characteristics and configuration of A/D converter          |     |

|   |      | 5.15.2 Terminal configuration of A/D converter                     |     |

|   |      | 5.15.3 Mask option                                                 | 121 |

|   |      | 5.15.4 A/D conversion                                              |     |

|   |      | 5.15.5 Interrupt function                                          |     |

|   |      | 5.15.6 I/O memory for A/D converter                                |     |

|   | 5 16 |                                                                    |     |

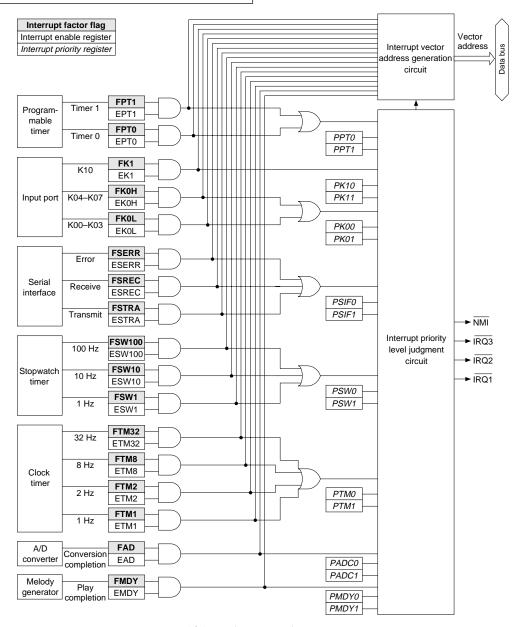

|   | 5.16 | Interrupt and Standby Status5.16.1 Interrupt generation conditions |     |

|   |      | 5.16.2 Interrupt factor flag                                       |     |

|   |      | 5.16.3 Interrupt enable register                                   |     |

|   |      | 5.16.4 Interrupt priority register and interrupt priority level    |     |

|   |      | 5.16.5 Exception processing vectors                                |     |

|   |      | 5.16.6 I/O memory for interrupt                                    |     |

|   |      | 5.16.7 Programming notes                                           |     |

|   | 5.17 | Notes for Low Current Consumption                                  |     |

| 5 | BAS  | SIC EXTERNAL WIRING DIAGRAM                                        |     |

| 7 | ELE  | ECTRICAL CHARACTERISTICS                                           |     |

|   | 7.1  | Absolute Maximum Rating                                            | 136 |

|   | 7.2  | Recommended Operating Conditions                                   |     |

|   | 7.3  | DC Characteristics                                                 |     |

|   | 7.4  | Analog Circuit Characteristics                                     | 138 |

|   |      |                                                                    |     |

### **CONTENTS**

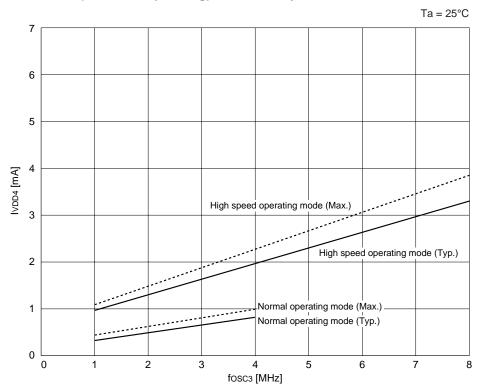

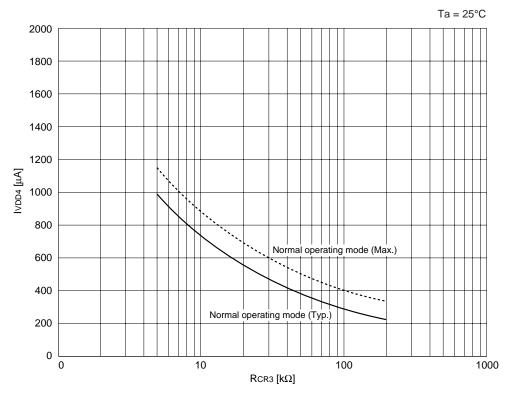

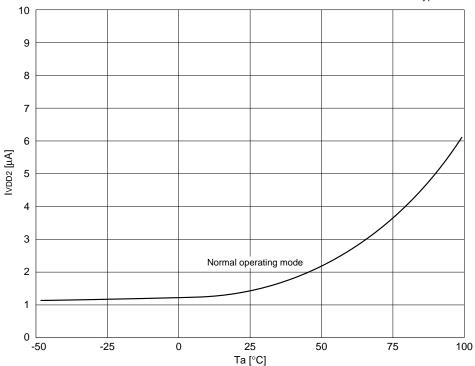

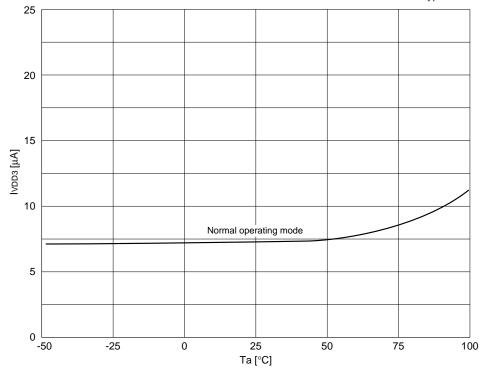

|     | 7.5  | Power Current Consumption                                            | 140 |

|-----|------|----------------------------------------------------------------------|-----|

|     | 7.6  | AC Characteristics                                                   | 141 |

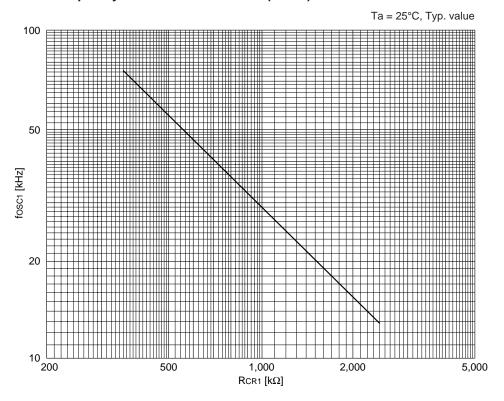

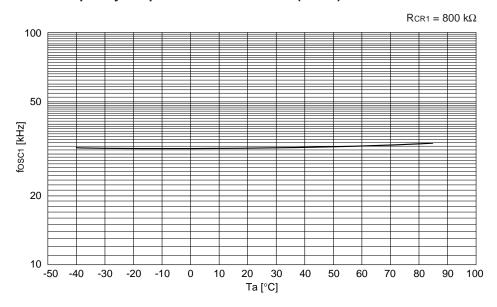

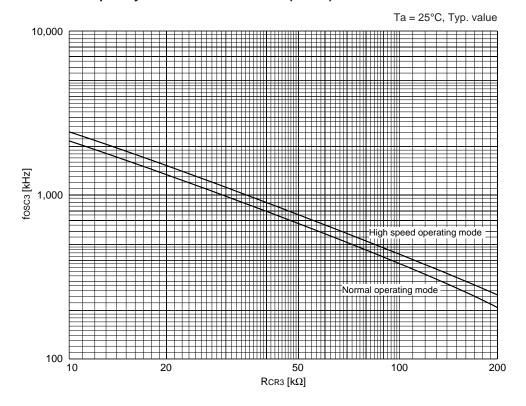

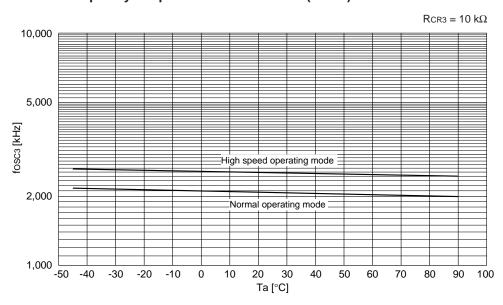

|     | 7.7  | Oscillation Characteristics                                          | 147 |

|     | 7.8  | A/D Converter Characteristics                                        | 148 |

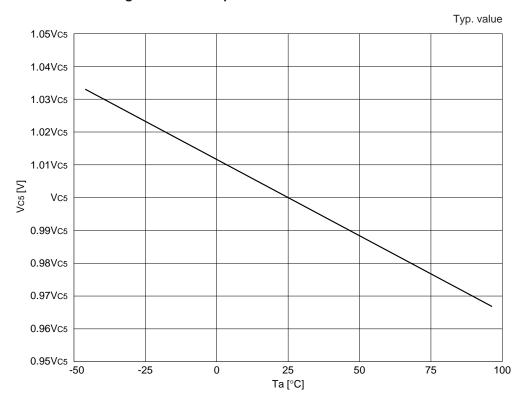

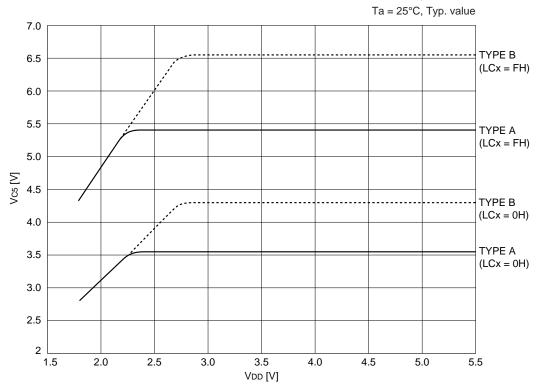

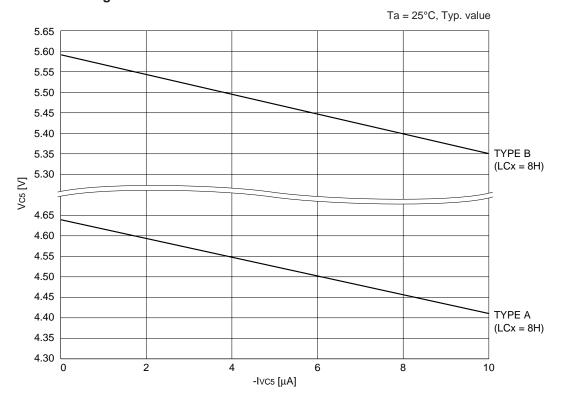

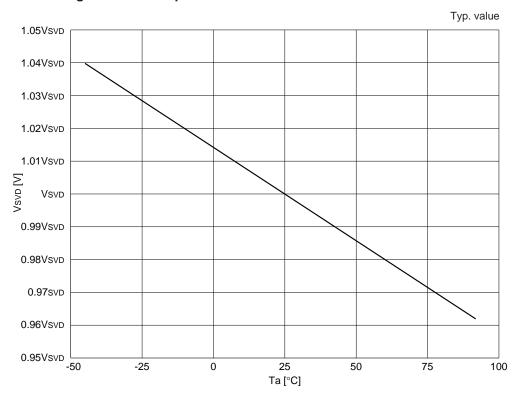

|     | 7.9  | Characteristics Curves (reference value)                             | 149 |

| 8   | PAC  | CKAGE                                                                |     |

|     | 8.1  | Plastic Package                                                      | 156 |

|     | 8.2  | Ceramic Package                                                      | 157 |

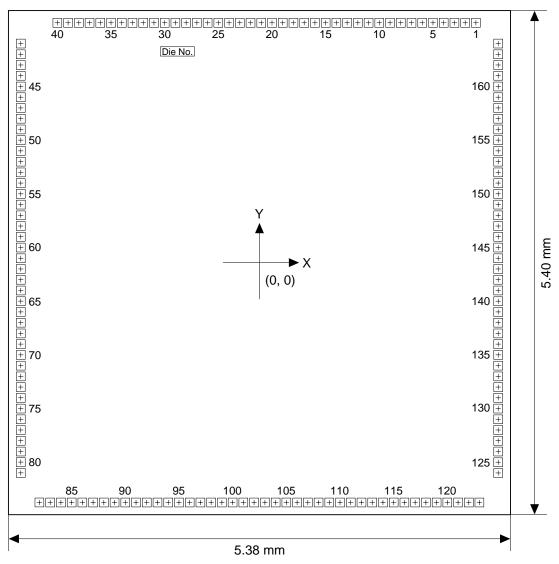

| 9   | PAI  | D LAYOUT                                                             | 158 |

|     | 9.1  | Diagram of Pad Layout                                                | 158 |

|     | 9.2  | Pad Coordinates                                                      |     |

| 10  | PRI  | ECAUTIONS ON MOUNTING                                                | 160 |

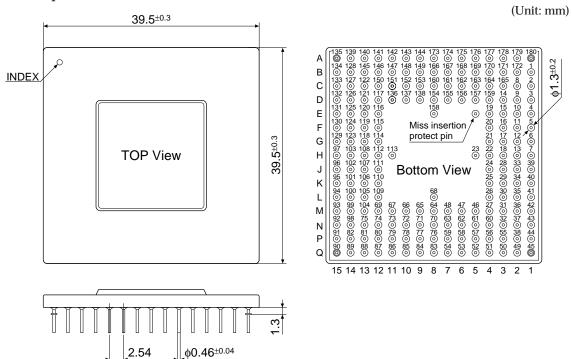

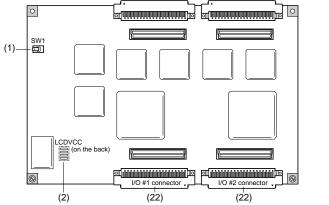

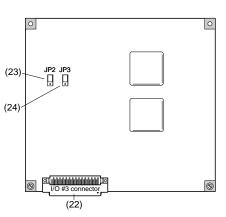

| API | PEND | OIX S5U1C88000P1&S5U1C88816P2 MANUAL                                 |     |

|     | LIVE | (Peripheral Circuit Board for S1C88816)                              | 162 |

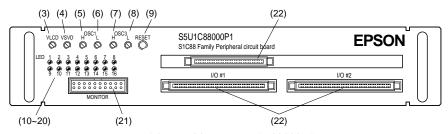

|     | A.1  | Names and Functions of Each Part                                     |     |

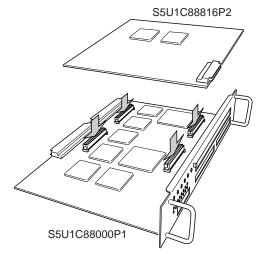

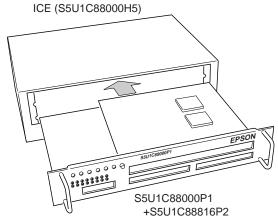

|     | A.2  | Installation                                                         |     |

|     |      | A.2.1 Installing S5U1C88816P2 to S5U1C88000P1                        |     |

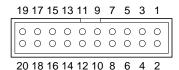

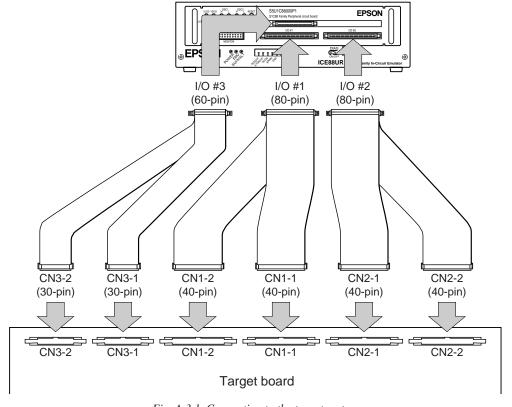

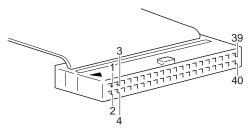

|     | A.3  | Connecting to the Target System                                      | 165 |

|     | A.4  | Downloading Circuit Data to the S5U1C88000P1                         | 167 |

|     | A.5  | Precautions                                                          | 168 |

|     |      | A.5.1 Precaution for operation                                       |     |

|     |      | A.5.2 Differences from actual IC                                     |     |

|     | A.6  | Product Specifications                                               |     |

|     |      | A.0.1 S5U1C88816P2 specifications  A 6 2 S5U1C88816P2 specifications |     |

## 1 INTRODUCTION

The S1C88816 microcomputer features the S1C88 (MODEL 3) CMOS 8-bit core CPU along with a 116K bytes of ROM, an 8K bytes of RAM, three different timers, a serial interface with optional asynchronization or clock synchronization, a melody generator and an A/D converter.

The S1C88816 has large capacity of ROM and RAM and fully operable over a wide range of voltages. Furthermore, it can perform high speed operations even at low voltage. Like all the equipment in the S1C Family, these microcomputers have low power consumption.

### 1.1 Features

Table 1.1.1 lists the features of the S1C88816.

Table 1.1.1 Main features

| Core CPU                        | S1C88 (MODEL3) CMOS 8-bit core CPU                                                                                 |  |  |  |  |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|--|

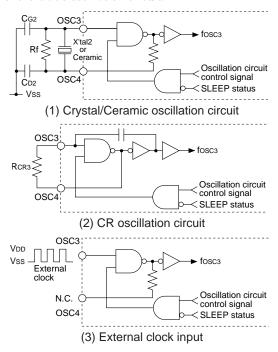

| OSC1 Oscillation circuit        | Crystal oscillation circuit/CR oscillation circuit/external clock input 32.768 kHz (Typ.)                          |  |  |  |  |

| OSC3 Oscillation circuit        | Crystal oscillation circuit/ceramic oscillation circuit/CR oscillation circuit/external clock input 8.2 MHz (Max.) |  |  |  |  |

| Instruction set                 | 608 types (usable for multiplication and division instructions)                                                    |  |  |  |  |

| Min. instruction execution time | 0.244 μsec/8.2 MHz (2 clock)                                                                                       |  |  |  |  |

| Internal ROM capacity           | 116K bytes                                                                                                         |  |  |  |  |

| Internal RAM capacity           | 8K bytes/RAM, 4224 bits/display memory, 512 bytes/melody RAM                                                       |  |  |  |  |

| Input port                      | 9 bits (1 bit can be set for event counter external clock input)                                                   |  |  |  |  |

| Output port                     | 7 bits (can be set for BZ, \overline{BZ}, TOUT, \overline{TOUT} and FOUT output)                                   |  |  |  |  |

| I/O port                        | 16 bits (P10–P13 and P14–P17 can be set for serial I/F input/output and A/D converter input, respectively)         |  |  |  |  |

| Serial interface                | 1ch (Optional clock synchronous system or asynchronous system)                                                     |  |  |  |  |

| Timer                           | Programmable timer (8 bits): 2ch                                                                                   |  |  |  |  |

|                                 | (1ch can be set as a an event counter or 2ch as a 16 bits programmable timer for 1ch)                              |  |  |  |  |

|                                 | Clock timer (8 bits): 1ch                                                                                          |  |  |  |  |

|                                 | Stopwatch timer (8 bits): 1ch                                                                                      |  |  |  |  |

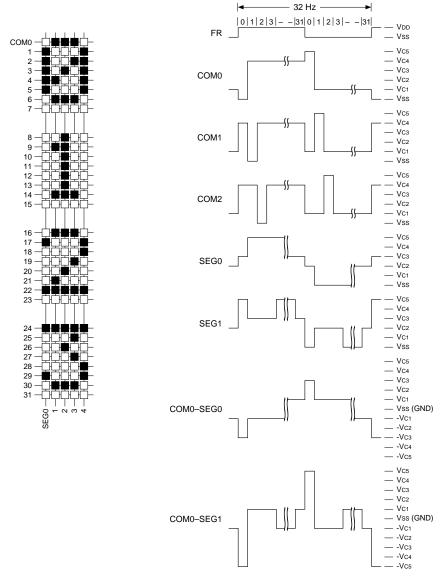

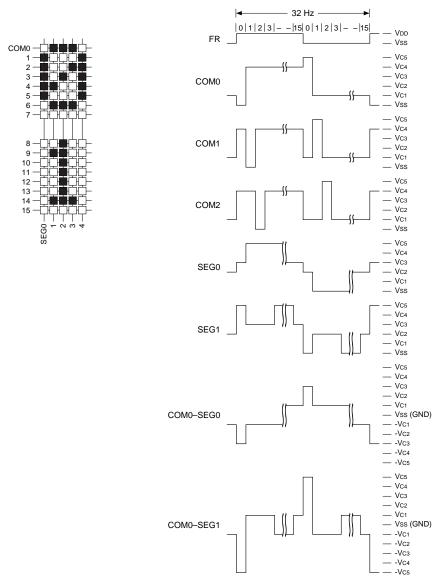

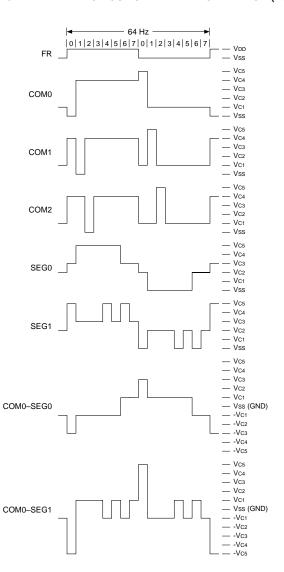

| LCD driver                      | Dot matrix type (supports $5 \times 8$ and $5 \times 5$ fonts)                                                     |  |  |  |  |

|                                 | 72 segments $\times$ 32 common (1/5 bias)                                                                          |  |  |  |  |

|                                 | 88 segments $\times$ 16 common (1/5 or 1/4 bias)                                                                   |  |  |  |  |

|                                 | 88 segments × 8 common (1/5 or 1/4 bias)                                                                           |  |  |  |  |

|                                 | LCD drive power supply circuit built-in (booster/reducer type, 5 potentials/4 potentials)                          |  |  |  |  |

| Sound generator                 | Envelope function, equipped with volume control                                                                    |  |  |  |  |

| Watchdog timer                  | Built-in                                                                                                           |  |  |  |  |

| Supply voltage detection        | Can detect up to 16 different voltage levels                                                                       |  |  |  |  |

| (SVD) circuit                   |                                                                                                                    |  |  |  |  |

| Melody generator                | 1 sound source (scale: 3 octaves, note: 8 types, tempo: 16 types)                                                  |  |  |  |  |

|                                 | Note and scale data are stored into the melody RAM (allows the CPU to read and write)                              |  |  |  |  |

| A/D converter                   | Successive-approximation type, resolution: 10 bits, input: 4ch (shared with P14–P17)                               |  |  |  |  |

| Interrupt                       | External interrupt: Input interrupt 2 systems (3 types)                                                            |  |  |  |  |

|                                 | Internal interrupt: Timer interrupt 3 systems (9 types)                                                            |  |  |  |  |

|                                 | Serial interface interrupt 1 system (3 types)                                                                      |  |  |  |  |

|                                 | Melody interrupt 1 system (1 type)                                                                                 |  |  |  |  |

|                                 | A/D converter interrupt 1 system (1 type)                                                                          |  |  |  |  |

| Supply voltage                  | Normal mode: 2.4 V–5.5 V (Max. 4.2 MHz)                                                                            |  |  |  |  |

|                                 | Low power mode: 1.8 V-5.5 V (Max. 80 kHz)                                                                          |  |  |  |  |

|                                 | High speed mode: 3.5 V–5.5 V (Max. 8.2 MHz)                                                                        |  |  |  |  |

| Current consumption             | SLEEP mode: 0.45 µA (Typ./normal mode)                                                                             |  |  |  |  |

|                                 | HALT mode (32.768 kHz): 1.5 μA (Typ./normal mode)                                                                  |  |  |  |  |

|                                 | , , , , , , , , , , , , , , , , , , ,                                                                              |  |  |  |  |

|                                 | During running (32.768 kHz): 7 μA (Typ./normal mode)                                                               |  |  |  |  |

|                                 | `                                                                                                                  |  |  |  |  |

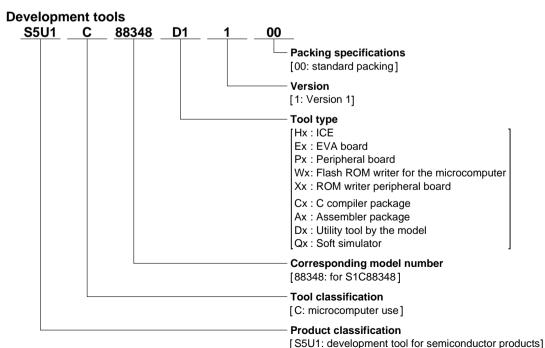

### 1.2 Block Diagram

Fig. 1.2.1 S1C88816 block diagram

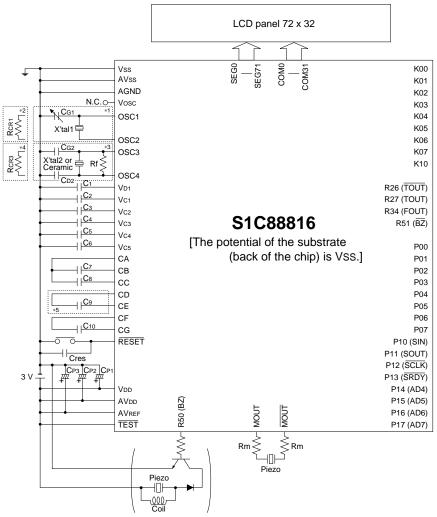

### 1.3 Pin Layout Diagram

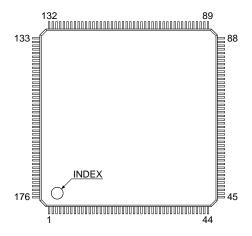

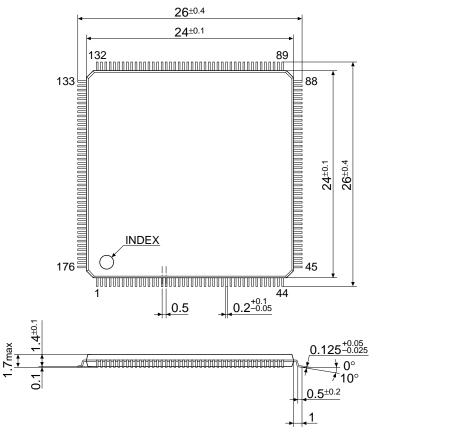

### QFP21-176pin

| Pin No. | Pin name | Pin No. | Pin name    | Pin No. | Pin name          | Pin No. | Pin name                |

|---------|----------|---------|-------------|---------|-------------------|---------|-------------------------|

| 1       | N.C.     | 45      | N.C.        | 89      | N.C.              | 133     | N.C.                    |

| 2       | N.C.     | 46      | SEG56       | 90      | N.C.              | 134     | N.C.                    |

| 3       | SEG16    | 47      | SEG57       | 91      | Vc3               | 135     | P01                     |

| 4       | SEG17    | 48      | SEG58       | 92      | V <sub>C2</sub>   | 136     | P00                     |

| 5       | SEG18    | 49      | SEG59       | 93      | Vc1               | 137     | MOUT                    |

| 6       | SEG19    | 50      | SEG60       | 94      | OSC3              | 138     | $\overline{	ext{MOUT}}$ |

| 7       | SEG20    | 51      | SEG61       | 95      | OSC4              | 139     | R26/TOUT                |

| 8       | SEG21    | 52      | SEG62       | 96      | $V_{D1}$          | 140     | R27/TOUT                |

| 9       | SEG22    | 53      | SEG63       | 97      | $V_{\mathrm{DD}}$ | 141     | R34/FOUT                |

| 10      | SEG23    | 54      | SEG64       | 98      | Vss               | 142     | R50/BZ                  |

| 11      | SEG24    | 55      | SEG65       | 99      | Vosc              | 143     | R51/BZ                  |

| 12      | SEG25    | 56      | SEG66       | 100     | OSC1              | 144     | COM0                    |

| 13      | SEG26    | 57      | SEG67       | 101     | OSC2              | 145     | COM1                    |

| 14      | SEG27    | 58      | SEG68       | 102     | TEST              | 146     | COM2                    |

| 15      | SEG28    | 59      | SEG69       | 103     | RESET             | 147     | COM3                    |

| 16      | SEG29    | 60      | SEG70       | 104     | K10/EVIN          | 148     | COM4                    |

| 17      | SEG30    | 61      | SEG71       | 105     | K07               | 149     | COM5                    |

| 18      | SEG31    | 62      | COM31/SEG72 | 106     | K06               | 150     | COM6                    |

| 19      | SEG32    | 63      | COM30/SEG73 | 107     | K05               | 151     | COM7                    |

| 20      | SEG33    | 64      | COM29/SEG74 | 108     | K04               | 152     | COM8                    |

| 21      | SEG34    | 65      | COM28/SEG75 | 109     | K03               | 153     | COM9                    |

| 22      | SEG35    | 66      | COM27/SEG76 | 110     | K02               | 154     | COM10                   |

| 23      | SEG36    | 67      | COM26/SEG77 | 111     | K01               | 155     | COM11                   |

| 24      | SEG37    | 68      | COM25/SEG78 | 112     | K00               | 156     | COM12                   |

| 25      | SEG38    | 69      | COM24/SEG79 | 113     | P17/AD7           | 157     | COM13                   |

| 26      | SEG39    | 70      | COM23/SEG80 | 114     | P16/AD6           | 158     | COM14                   |

| 27      | SEG40    | 71      | COM22/SEG81 | 115     | P15/AD5           | 159     | COM15                   |

| 28      | SEG41    | 72      | COM21/SEG82 | 116     | P14/AD4           | 160     | SEG0                    |

| 29      | SEG42    | 73      | COM20/SEG83 | 117     | P13/SRDY          | 161     | SEG1                    |

| 30      | SEG43    | 74      | COM19/SEG84 | 118     | P12/SCLK          | 162     | SEG2                    |

| 31      | SEG44    | 75      | COM18/SEG85 | 119     | P11/SOUT          | 163     | SEG3                    |

| 32      | SEG45    | 76      | COM17/SEG86 | 120     | P10/SIN           | 164     | SEG4                    |

| 33      | SEG46    | 77      | COM16/SEG87 | 121     | $AV_{DD}$         | 165     | SEG5                    |

| 34      | SEG47    | 78      | CG          | 122     | AGND              | 166     | SEG6                    |

| 35      | SEG48    | 79      | CF          | 123     | AVss              | 167     | SEG7                    |

| 36      | SEG49    | 80      | CE          | 124     | AVREF             | 168     | SEG8                    |

| 37      | SEG50    | 81      | CD          | 125     | P07               | 169     | SEG9                    |

| 38      | SEG51    | 82      | CC          | 126     | P06               | 170     | SEG10                   |

| 39      | SEG52    | 83      | CB          | 127     | P05               | 171     | SEG11                   |

| 40      | SEG53    | 84      | CA          | 128     | P04               | 172     | SEG12                   |

| 41      | SEG54    | 85      | Vc5         | 129     | P03               | 173     | SEG13                   |

| 42      | SEG55    | 86      | VC4         | 130     | P02               | 174     | SEG14                   |

| 43      | N.C.     | 87      | N.C.        | 131     | N.C.              | 175     | SEG15                   |

| 44      | N.C.     | 88      | N.C.        | 132     | N.C.              | 176     | N.C.                    |

|         |          |         |             |         |                   | N       | V.C.: No Connection     |

Fig. 1.3.1 S1C88816 pin layout

Table 1.3.1 S1C88816 pin description

| Pin name        | Pin No.           | In/out  | Function                                                                        |

|-----------------|-------------------|---------|---------------------------------------------------------------------------------|

| V <sub>DD</sub> | 97                | III/Out | Power supply (+) terminal                                                       |

| Vss             | 98                |         | Power supply (47) terminal                                                      |

| V <sub>D1</sub> | 96                |         | Regulated voltage for internal circuit                                          |

| Vosc            | 99                |         | Regulated voltage for OSC1 oscillation circuit                                  |

| VC1–VC5         |                   | 0       |                                                                                 |

|                 | 93–91, 86, 85     |         | LCD drive voltage output terminals                                              |

| CA-CG           | 84–78             |         | Voltage boost/reduce-capacitor connection terminals for LCD                     |

| OSC1            | 100               | I       | OSC1 oscillation input terminal                                                 |

| 0502            | 101               |         | (select crystal oscillation/CR oscillation/external clock input by mask option) |

| OSC2            | 101               | 0       | OSC1 oscillation output terminal                                                |

| OSC3            | 94                | I       | OSC3 oscillation input terminal                                                 |

| onga            | 0.5               |         | (select crystal/ceramic/CR oscillation/external clock input by mask option)     |

| OSC4            | 95                | 0       | OSC3 oscillation output terminal                                                |

| K00-K07         | 112–105           | I       | Input terminals (K00–K07)                                                       |

| K10/EVIN        | 104               | I       | Input terminal (K10) or event counter external clock input terminal (EVIN)      |

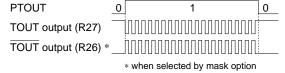

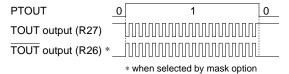

| R26/TOUT        | 139               | О       | Output terminal (R26) or programmable timer underflow signal inverted           |

|                 |                   |         | output terminal (TOUT) (selectable by mask option)                              |

| R27/TOUT        | 140               | О       | Output terminal (R27)                                                           |

|                 |                   |         | or programmable timer underflow signal output terminal (TOUT)                   |

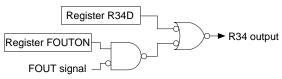

| R34/FOUT        | 141               | 0       | Output terminal (R34) or clock output terminal (FOUT)                           |

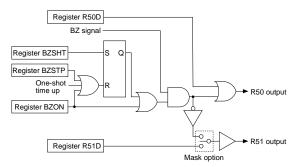

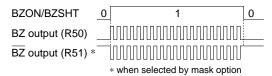

| R50/BZ          | 142               | О       | Output terminal (R50) or buzzer output terminal (BZ)                            |

| R51/BZ          | 143               | О       | Output terminal (R51) or buzzer inverted output terminal (BZ)                   |

|                 |                   |         | (selectable by mask option)                                                     |

| P00–P07         | 136, 135, 130–125 | I/O     | I/O terminals (P00–P07)                                                         |

| P10/SIN         | 120               | I/O     | I/O terminal (P10) or serial I/F data input terminal (SIN)                      |

| P11/SOUT        | 119               | I/O     | I/O terminal (P11) or serial I/F data output terminal (SOUT)                    |

| P12/SCLK        | 118               | I/O     | I/O terminal (P12) or serial I/F clock I/O terminal (SCLK)                      |

| P13/SRDY        | 117               | I/O     | I/O terminal (P13) or serial I/F ready signal output terminal (SRDY)            |

| P14/AD4         | 116               | I/O     | I/O terminal (P14) or A/D converter input terminal (AD4)                        |

| P15/AD5         | 115               | I/O     | I/O terminal (P15) or A/D converter input terminal (AD5)                        |

| P16/AD6         | 114               | I/O     | I/O terminal (P16) or A/D converter input terminal (AD6)                        |

| P17/AD7         | 113               | I/O     | I/O terminal (P17) or A/D converter input terminal (AD7)                        |

| MOUT            | 137               | О       | Melody output terminal                                                          |

| MOUT            | 138               | О       | Melody inverted output terminal                                                 |

| COM0-COM15      | 144–159           | О       | LCD common output terminals                                                     |

| COM16-COM31     | 77–62             | O       | LCD common output terminals (when 1/32 duty is selected)                        |

| /SEG87–SEG72    |                   |         | or LCD segment output terminal (when 1/16 or 1/8 duty is selected)              |

| SEG0-SEG71      | 160–175, 3–42,    | O       | LCD segment output terminals                                                    |

|                 | 46–61             |         |                                                                                 |

| RESET           | 103               | I       | Initial reset input terminal                                                    |

| TEST *1         | 102               | I       | Test input terminal                                                             |

| AVDD            | 121               | -       | Analog system power supply (+) terminal                                         |

| AVss            | 123               | -       | Analog system power supply (–) terminal                                         |

| AGND            | 122               | -       | Analog system ground terminal                                                   |

| AVREF           | 124               | I       | Analog system reference voltage input terminal                                  |

$<sup>*1 \</sup>quad \overline{TEST} \text{ is the terminal used for shipping inspection of the IC. For normal operation be sure it is connected to $V$DD.}$

### 1.4 Mask Option

Mask options shown below are provided for the S1C88816.

Several hardware specifications are prepared in each mask option, and one of them can be selected according to the application.

Select the specifications that meet the target system and check the appropriate box.

The option selection is done interactively on the screen during function option generator winfog execution, using this option list as reference. Mask pattern of the IC is finally generated based on the data created by the winfog.

Refer to the "S5U1C88000C Manual II" for details on the winfog.

### PERIPHERAL CIRCUIT BOARD option list

| The following shows the options for configuring the Peripheral Circuit Board (S5U1C88000P1 with S5U1C88816P2) installed in the ICE (S5U1C88000H5). The selections do not affect the IC's mask option. |                                                                                                                                                                                                         |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| A OSC1 SYSTEM CLOCK  ☐ 1. Internal Clock ☐ 2. User Clock                                                                                                                                              | When User Clock is selected, input a clock to the OSC1 terminal. When Internal Clock is selected, the clock frequency is changed according to the oscillation circuit selected by the IC's mask option. |  |  |  |  |  |

| B OSC3 SYSTEM CLOCK  ☐ 1. Internal Clock ☐ 2. User Clock                                                                                                                                              | When User Clock is selected, input a clock to the OSC3 terminal. When Internal Clock is selected, the clock frequency is changed according to the oscillation circuit selected by the IC's mask option. |  |  |  |  |  |

|                                                                                                                                                                                                       |                                                                                                                                                                                                         |  |  |  |  |  |

| S1C88816 mask option list                                                                                      |                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The following shows the option list<br>Board installed in the ICE does no                                      |                                                                                                                                                                                                                              | e IC's mask pattern. Note that the Peripheral Circuit tions.                                                                                                                                                                                                                                                                                                                                                         |

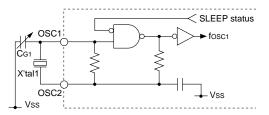

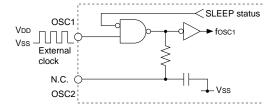

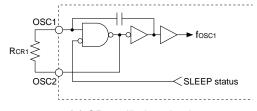

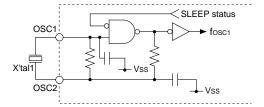

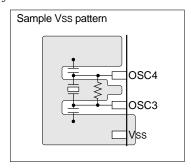

| 1 OSC1 SYSTEM CLOCK  □ 1. Crystal □ 2. External Clock □ 3. CR □ 4. Crystal (with 0                             |                                                                                                                                                                                                                              | The specification of the OSC1 oscillation circuit can be selected from among four types: "Crystal oscillation", "CR oscillation", "Crystal oscillation (gate capacitor built-in)" and "External clock input". Refer to Section 5.3.3, "OSC1 oscillation circuit", for details.                                                                                                                                       |

| 2 OSC3 SYSTEM CLOCK  □ 1. Crystal □ 2. Ceramic □ 3. CR □ 4. External Clock                                     |                                                                                                                                                                                                                              | The specification of the OSC3 oscillation circuit can be selected from among four types: "Crystal oscillation", "Ceramic oscillation", "CR oscillation" and "External clock input". Refer to Section 5.3.4, "OSC3 oscillation circuit", for details.                                                                                                                                                                 |

| 3 MULTIPLE KEY ENTRY RESET  • Combination □ 1. Not Use □ 2. Use K00, K01 □ 3. Use K00, K01, □ 4. Use K00, K01, |                                                                                                                                                                                                                              | This function resets the IC when several keys are pressed simultaneously. The mask option is used to select whether this function is used or not. Further when the function is used, a combination of the input ports (K00–K03), which are connected to the keys to be pressed simultaneously, can be selected. Refer to Section 4.1.2, "Simultaneous LOW level input at input port terminals K00–K03", for details. |

| 4 SVD RESET  □ 1. Not Use □ 2. Use                                                                             |                                                                                                                                                                                                                              | The SVD circuit has a function that generates an initial reset signal when the supply voltage drops to level 0 or less. The mask option is used to select whether this function is used or not. Refer to Section 5.14, "Supply Voltage Detection (SVD) Circuit", for details.                                                                                                                                        |

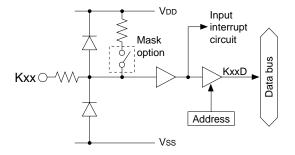

| 5 INPUT PORT PULL UP RESISTOR  • K00                                                                           | □ 2. Gate Direct | This mask option can select whether the pull-up resistor for the input port terminal is used or not. It is possible to select for each bit of the input ports. Refer to Section 5.4, "Input Ports (K ports)", for details. Furthermore, a pull-up option is also provided for the RESET terminal.                                                                                                                    |

| 6  | I/O PORT PULL UP RESISTOR           • P00         □ 1. With Resistor         □ 2. Gate Direct           • P01         □ 1. With Resistor         □ 2. Gate Direct           • P02         □ 1. With Resistor         □ 2. Gate Direct           • P03         □ 1. With Resistor         □ 2. Gate Direct           • P04         □ 1. With Resistor         □ 2. Gate Direct           • P05         □ 1. With Resistor         □ 2. Gate Direct           • P06         □ 1. With Resistor         □ 2. Gate Direct           • P10         □ 1. With Resistor         □ 2. Gate Direct           • P11         □ 1. With Resistor         □ 2. Gate Direct           • P12         □ 1. With Resistor         □ 2. Gate Direct           • P13         □ 1. With Resistor         □ 2. Gate Direct           • P14         □ 1. With Resistor         □ 2. Gate Direct           • P15         □ 1. With Resistor         □ 2. Gate Direct           • P16         □ 1. With Resistor         □ 2. Gate Direct           • P17         □ 1. With Resistor         □ 2. Gate Direct           • P17         □ 1. With Resistor         □ 2. Gate Direct | This mask option can select whether the pull-up resistor for the I/O port terminal (it works during input mode) is used or not. It is possible to select for each bit of the I/O ports. Refer to Section 5.6, "I/O Ports (P ports)", for details. Since P10 to P13 are shared with the serial interface I/O terminals, the selected P10 and P12 terminal configuration is applied to the serial input (SIN) terminal and serial clock input terminal (SCLK in clock synchronous mode) when the serial interface is used. Refer to Section 5.7, "Serial Interface", for details.                                                                                                                                                                                                               |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | <i>LCD DRIVE DUTY</i> □ 1. 1/32 & 1/16 Duty □ 2. 1/8 Duty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | The drive duty for the built-in LCD driver can be selected whether it will be 1/32 and 1/16 software-switched or fixed at 1/8. Refer to Section 5.11, "LCD Controller", for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

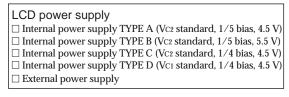

| 8  | LCD POWER SUPPLY  □ 1. Internal TYPE A (Vc2 Standard, 1/5 Bias, 4.5 V) □ 2. External □ 3. Internal TYPE B (Vc2 Standard, 1/5 Bias, 5.5 V) □ 4. Internal TYPE C (Vc2 Standard, 1/4 Bias, 4.5 V) □ 5. Internal TYPE D (Vc1 Standard, 1/4 Bias, 4.5 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Either the internal power supply or an external power supply can be selected as the LCD system power source. Furthermore, when using the internal power supply, the LCD drive voltage can be set for a 4.5 V panel or a 5.5 V panel and the drive bias to 1/5 or 1/4. Refer to Section 5.11, "LCD Controller", for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 9  | $\overline{BZ}$ OUTPUT (R51) $\Box$ 1. Use $\Box$ 2. Not Use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | The R51 port can be configured as a general purpose output port or as the $\overline{BZ}$ output port (BZ inverted output). Refer to Section 5.5, "Output Ports (R ports)" for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 10 | <i>TOUT OUTPUT (R26)</i> ☐ 1. Use ☐ 2. Not Use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | The R26 port can be configured as a general purpose output port or as the TOUT output port (TOUT inverted output). Refer to Section 5.5, "Output Ports (R ports)" for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11 | CPU MODE  □ 1. Maximum Mode □ 2. Minimum Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | The CPU mode of the S1C88 core can select either maximum mode or minimum mode (fixed after selection). In the maximum mode, since the S1C88816 saves the program counter (PC), system condition flag (SC) and code bank register (CB) values into the stack when an interrupt is generated, the program sequence is able to return to the previous bank if the interrupt handler routines change banks without saving. The minimum mode can be selected only when the program code size is less than 52K bytes and the "Compact code" model is specified using the EPSON C Compiler. Since the subroutine call in the minimum mode accesses the stack area with a 2-byte address (3 bytes in maximum mode), it has better RAM-access efficiency and process-cycle time than the maximum mode. |

| 12 | MODE DURING BUZZER OUTPUT  ☐ 1. Normal Mode ☐ 2. Heavy Load Protection Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | This option allows selection whether the heavy load protection mode is set or not when the buzzer (BZ) signal is output. When direct driving a piezoelectric buzzer, select Normal mode to reduce current consumption. When using an external bipolar transistor, select Heavy load protection mode. Refer to Section 2.3, "Heavy Load Protection Mode", for details.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 13 | MODE DURING MELODY OUTPUT  □ 1. Normal Mode □ 2. Heavy Load Protection Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | This option allows selection whether the heavy load protection mode is set or not when the melody (MOUT) signal is output. When direct driving a piezoelectric buzzer, select Normal mode to reduce current consumption. When using an external bipolar transistor, select Heavy load protection mode. Refer to Section 2.3, "Heavy Load Protection Mode", for details.                                                                                                                                                                                                                                                                                                                                                                                                                       |

### 2 POWER SUPPLY

In this section, we will explain the operating voltage and the configuration of the internal power supply circuit of the S1C88816.

### 2.1 Operating Voltage

The S1C88816 operating power voltage is as follows:

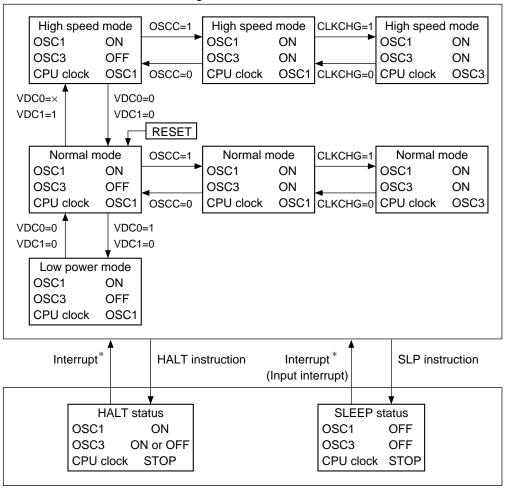

Normal mode: 2.4 V to 5.5 V Low power mode: 1.8 V to 5.5 V High speed mode: 3.5 V to 5.5 V

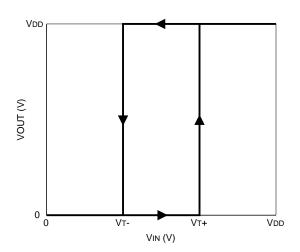

If supply voltage drops below level 0 (see Chapter 7, "ELECTRICAL CHARACTERISTICS"), the system is automatically reset by a supply voltage detection (SVD) circuit described in the latter. This function can be selected by mask option.

### 2.2 Internal Power Supply Circuit

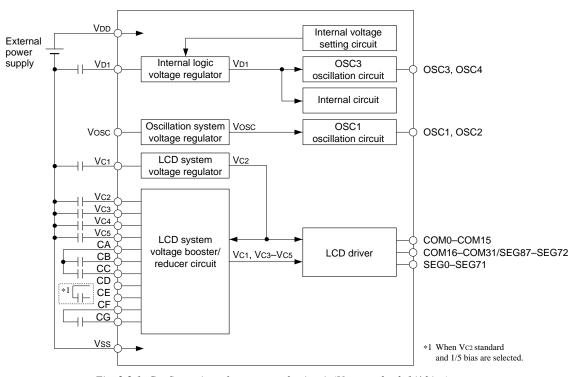

The S1C88816 incorporates the power supply circuit shown in Figure 2.2.1. When voltage within the range described above is supplied to VDD (+) and Vss (GND), all the voltages needed for the internal circuit are generated internally in the IC.

Roughly speaking, the power supply circuit is divided into three sections.

The internal logic voltage regulator generates the operating voltage <VD1> for driving the internal logic circuits and the OSC3 oscillation circuit.

The VD1 voltage can be selected from the following three types: 1.3 V for low-power mode, 2.2 V for normal mode and 3.3 V for high-speed mode. It should be selected by a program to switch according to the supply voltage and oscillation frequency.

See Section 5.3, "Oscillation Circuits and Operating Mode", for the switching of operating mode.

The oscillation system voltage regulator generates the operating voltage <Vosc> for the OSC1 oscillation circuit.

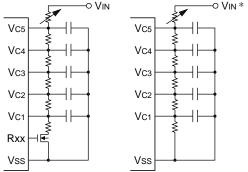

The LCD system power supply circuit generates the LCD drive voltages <VC1> to <VC5>. In 1/5 bias mode, VC1 is generated by halving VC2 output from the LCD system voltage regulator and VC3 to VC5 are generated by boosting VC2. These five voltages can be supplied from outside the IC by mask option. See Chapter 7, "ELECTRICAL CHARACTERISTICS" for the voltage values.

In the S1C88816, the LCD drive voltage is supplied to the built-in LCD driver which drives the LCD panel connected to the SEG and COM terminals.

Note: Do not use the voltages output from the internal power supply circuit for driving external circuits.

Fig. 2.2.1 Configuration of power supply circuit (Vc2 standard, 1/4 bias)

### 2.3 Heavy Load Protection Mode

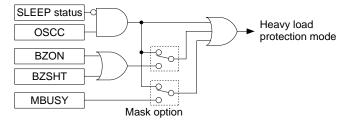

The S1C88816 has a heavy load protection function for stable operation even when the supply voltage fluctuates by driving a heavy load. The heavy load protection mode becomes valid when the peripheral circuits are in the following status:

- (1) When the OSC3 oscillation circuit is ON (OSCC = "1" and not in SLEEP)

- (2) When the buzzer output is ON (BZON = "1" or BZSHT = "1")

- (3) When the melody output is ON (MBUSY = "1")

The conditions (2) and (3) can be selected by mask option.

Heavy load protection mode

during buzzer output

Normal mode

Heavy load protection mode

Heavy load protection mode

during melody output

Normal mode

Heavy load protection mode

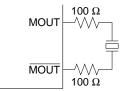

When direct driving a piezoelectric buzzer with the buzzer (BZ,  $\overline{BZ}$ ) or melody signal (MOUT,  $\overline{MOUT}$ ), select Normal mode to reduce current consumption. When driving an external bipolar transistor with the BZ or MOUT signal, select Heavy load protection mode.

When using the melody output terminal (MOUT,  $\overline{MOUT}$ ) for buzzer output, select the same option for both the buzzer and melody outputs.

For details of the OSC3 oscillation circuit, buzzer output and melody output, refer to "5.3 Oscillation Circuits and Operating Mode", "5.12 Sound Generator" and "5.13 Melody Generator", respectively.

Fig. 2.3.1 Configuration of heavy load protection mode control circuit

## 3 CPUAND MEMORY CONFIGURATION

In this section, we will explain the CPU and memory configuration.

### 3.1 CPU

The S1C88816 utilize the S1C88 8-bit core CPU whose resistor configuration, command set, etc. are virtually identical to other units in the family of processors incorporating the S1C88.

See the "S1C88 Core CPU Manual" for the S1C88.

The S1C88816 supports Model 3/minimum mode of the S1C88 CPU which allows accessing of the internal memory mapped within the physical space from 000000H to 01FFFFH.

### 3.2 Internal Memory

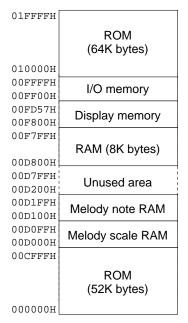

The S1C88816 is equipped with internal ROM and RAM as shown in Figure 3.2.1.

Fig. 3.2.1 Internal memory map

#### 3.2.1 ROM

The internal ROM capacity is shown below.

Capacity: 116K bytes

Address: 000000H to 00CFFFH 010000H to 01FFFFH

### 3.2.2 RAM

The internal ROM capacity is shown below.

Capacity: 8K bytes

Address: 00D800H to 00F7FFH

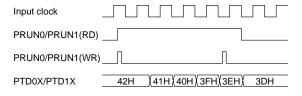

### 3.2.3 I/O memory

A memory mapped I/O method is employed in the S1C88816 for interfacing with internal peripheral circuit. Peripheral circuit control bits and data register are arranged in data memory space. Control and data exchange are conducted via normal memory access. The I/O memory is arranged from address 00FF00H to address 00FFFFH. See Section 5.1, "I/O Memory Map", for details of the I/O memory.

### 3.2.4 Display memory

The S1C88816 is equipped with an internal display memory which stores a display data for LCD driver.

The display memory is arranged from address 00F800H to address 00FD57H (including the unused area). See Section 5.11, "LCD Controller", for details of the display memory.

### 3.3 Exception Processing Vectors

Address 000000H to address 000027H in the program area of the S1C88816 is assigned as exception processing vectors. Furthermore, from address 00002AH to address 0000FFH, software interrupt vectors are assignable to any two bytes which begin with an even address. Table 3.3.1 lists the vector addresses and the exception processing factors to which they correspond.

Table 3.3.1 Vector addresses and exception processing factors

| Vector address | Exception processing factor                | Priority     |

|----------------|--------------------------------------------|--------------|

| 000000H        | Reset                                      | High         |

| 000002H        | Zero division                              | <b>↑</b>     |

| 000004H        | Watchdog timer (NMI)                       |              |

| 000006Н        | Programmable timer 1 interrupt             |              |

| 000008H        | Programmable timer 0 interrupt             |              |

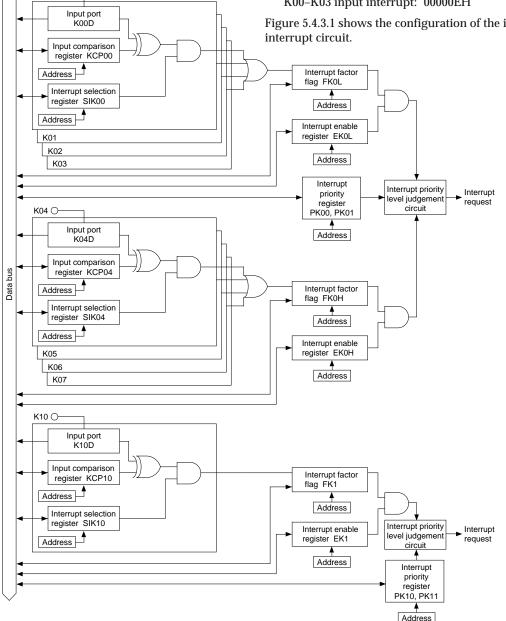

| 00000AH        | K10 input interrupt                        |              |

| 00000CH        | K04–K07 input interrupt                    |              |

| 00000EH        | K00–K03 input interrupt                    |              |

| 000010H        | Serial I/F error interrupt                 |              |

| 000012H        | Serial I/F receiving complete interrupt    |              |

| 000014H        | Serial I/F transmitting complete interrupt |              |

| 000016H        | Stopwatch timer 100 Hz interrupt           |              |

| 000018H        | Stopwatch timer 10 Hz interrupt            |              |

| 00001AH        | Stopwatch timer 1 Hz interrupt             |              |

| 00001CH        | Clock timer 32 Hz interrupt                |              |

| 00001EH        | Clock timer 8 Hz interrupt                 |              |

| 000020H        | Clock timer 2 Hz interrupt                 |              |

| 000022H        | Clock timer 1 Hz interrupt                 |              |

| 000024H        | A/D conversion complete interrupt          | $\downarrow$ |

| 000026Н        | Melody play complete interrupt             | Low          |

| 000028H        | System reserved (cannot be used)           | No           |

| 00002AH        |                                            | priority     |

| :              | Software interrupt                         | rating       |

| 0000FEH        |                                            | raung        |

For each vector address and the address after it, the start address of the exception processing routine is written into the subordinate and super ordinate sequence. When an exception processing factor is generated, the exception processing routine is executed starting from the recorded address.

When multiple exception processing factors are generated at the same time, execution starts with the highest priority item.

The priority sequence shown in Table 3.3.1 assumes that the interrupt priority levels are all the same. The interrupt priority levels can be set by software in each system. (See Section 5.16, "Interrupt and Standby Status".)

Note: For exception processing other than reset, SC (system condition flag) and PC (program counter) are evacuated to the stack and branches to the exception processing routines. Consequently, when returning to the main routine from exception processing routines, please use the RETE instruction.

See the "S1C88 Core CPU Manual" for information on CPU operations when an exception processing factor is generated.

### 3.4 CC (Customized Condition Flag)

The S1C88816 does not use the customized condition flag (CC) in the core CPU. Accordingly, it cannot be used as a branching condition for the conditional branching instruction (JRS, CARS).

### 4 INITIAL RESET

Initial reset in the S1C88816 is required in order to initialize circuits. This chapter describes initial reset factors and the initial settings for internal registers.

### 4.1 Initial Reset Factors

There are three initial reset factors for the S1C88816 as shown below.

- (1) RESET terminal

- (2) Simultaneous LOW level input at input port terminals K00–K03

- (3) Supply voltage detection (SVD) circuit

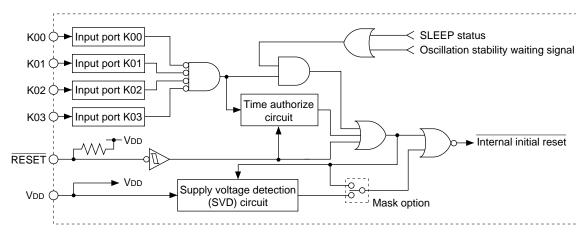

Figure 4.1.1 shows the configuration of the initial reset circuit.

The CPU and peripheral circuits are initialized by means of initial reset factors. When the factor is canceled, the CPU commences reset exception processing. (See "S1C88 Core CPU Manual".)

When this occurs, reset exception processing vectors, Bank 0, 000000H–000001H from program memory are read out and the program (initialization routine) which begins at the readout address is executed.

Fig. 4.1.1 Configuration of initial reset circuit

### 4.1.1 RESET terminal

Initial reset can be done by executed externally inputting a LOW level to the  $\overline{RESET}$  terminal. Be sure to maintain the  $\overline{RESET}$  terminal at LOW level for the regulation time after the power on to assure the initial reset.

In addition, be sure to use the  $\overline{RESET}$  terminal for the first initial reset after the power is turned on. The  $\overline{RESET}$  terminal is equipped with a pull-up resistor. You can select whether or not to use by mask option.

| RESET terminal pull-up res                        | sistors               |

|---------------------------------------------------|-----------------------|

| $\overline{\text{RESET}}$ $\square$ With resistor | $\square$ Gate direct |

## 4.1.2 Simultaneous LOW level input at input port terminals K00–K03

Another way of executing initial reset externally is to input a LOW level simultaneously to the input ports (K00–K03) selected by mask option.

Since there is a built-in time authorize circuit, be sure to maintain the designated input port terminal at LOW level for two seconds (when the oscillation frequency fosc1 = 32.768 kHz) or more to perform the initial reset by means of this function.

However, the time authorize circuit is bypassed during the SLEEP (standby) status and oscillation stabilization waiting period, and initial reset is executed immediately after the simultaneous LOW level input to the designated input ports.

The combination of input ports (K00–K03) that can be selected by mask option are as follows:

| Multiple key entry reset |

|--------------------------|

| ☐ Not use                |

| □ K00 & K01              |

| □ K00 & K01 & K02        |

| ☐ K00 & K01 & K02 & K03  |

|                          |

11

For instance, if mask option "K00 & K01 & K02 & K03" is selected, initial reset will take place when the input level at input ports K00-K03 is simultaneously LOW.

When using this function, make sure that the designated input ports do not simultaneously switch to LOW level while the system is in normal operation.

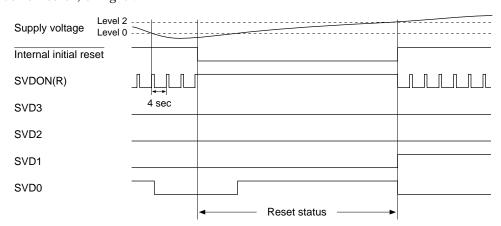

### 4.1.3 Supply voltage detection (SVD) circuit

When the SVD circuit detects that supply voltage has dropped below level 0 four successive times (see Chapter 7, "ELECTRICAL CHARACTERIS-TICS"), it outputs an initial reset signal until the supply voltage has been restored to level 2. You can select whether or not to use the initial reset according to the SVD circuit by mask option. If you use it, the supply voltage must be at least level 2 for the first sampling of the SVD circuit, when the power is turned on. At this time, if the power voltage level is less than level 2, the initial reset status will not be canceled and instead the SVD circuit will continue sampling until the supply voltage reaches level 2 or more. For more information, see "5.14 Supply Voltage Detection (SVD) Circuit" in this Manual.

### 4.1.4 Initial reset sequence

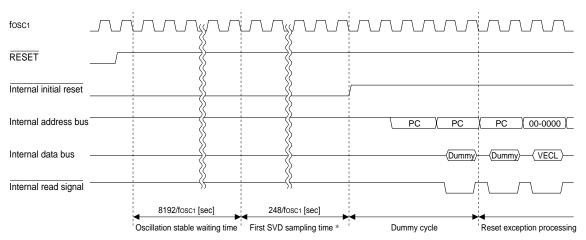

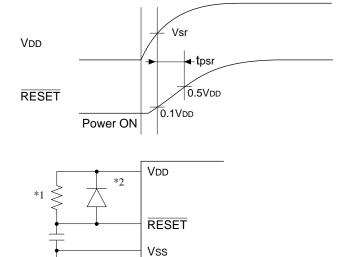

After cancellation of the LOW level input to the RESET terminal, when the power is turned on, the start-up of the CPU is held back until the oscillation stabilization waiting time (8,192/fosc1 sec.) has elapsed. When the initial reset by the SVD circuit has been used, an initial sampling time (248/fosc1 sec.) is added as additional waiting time. Figure 4.1.4.1 shows the operating sequence following initial reset release.

Also, when using the initial reset by simultaneous LOW level input into the input port, you should be careful of the following points.

- (1) During SLEEP status, since the time authorization circuit is bypassed, an initial reset is triggered immediately after a LOW level simultaneous input value. In this case, the CPU starts after waiting the oscillation stabilization time and the SVD circuit initial sampling time (when used with the mask option), following cancellation of the LOW level simultaneous input.

- (2) Other than during SLEEP status, an initial reset will be triggered 1–2 seconds after a LOW level simultaneous input. In this case, since a reset differential pulse (64/fosc1 sec.) is generated within the S1C88816, the CPU will start even if the LOW level simultaneous input status is not canceled.

\* When the initial reset by the SVD circuit with the mask option has been used, this cycle is inserted as the waiting time.

Fig. 4.1.4.1 Initial reset sequence

### 4.2 Initial Settings After Initial Reset

The CPU internal registers are initialized as follows during initial reset.

Table 4.2.1 Initial settings

| Register name               | Code | Bit length | Setting value |

|-----------------------------|------|------------|---------------|

| Data register A             | A    | 8          | Undefined     |

| Data register B             | В    | 8          | Undefined     |

| Index (data) register L     | L    | 8          | Undefined     |

| Index (data) register H     | Н    | 8          | Undefined     |

| Index register IX           | IX   | 16         | Undefined     |

| Index register IY           | IY   | 16         | Undefined     |

| Program counter             | PC   | 16         | Undefined*    |

| Stack pointer               | SP   | 16         | Undefined     |

| Base register               | BR   | 8          | Undefined     |

| Zero flag                   | Z    | 1          | 0             |

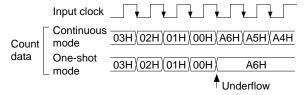

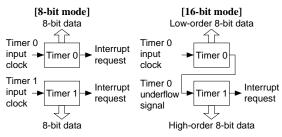

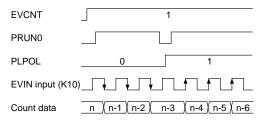

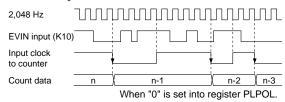

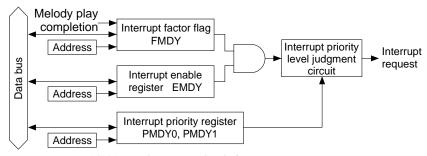

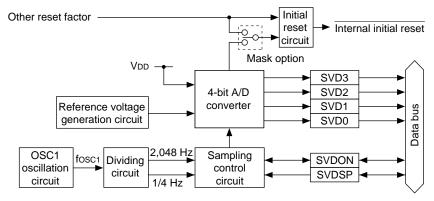

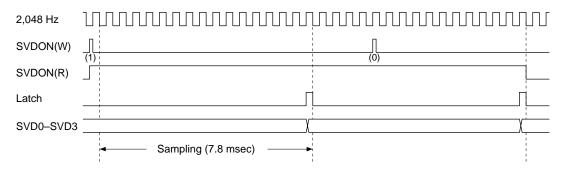

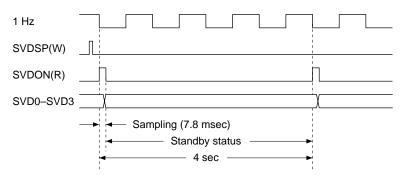

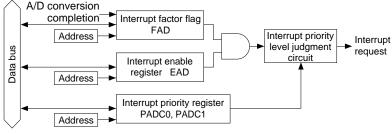

| Carry flag                  | C    | 1          | 0             |