# S1R72005 Application Note

## NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of Economy, Trade and Industry or other approval from another government agency.

All other product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

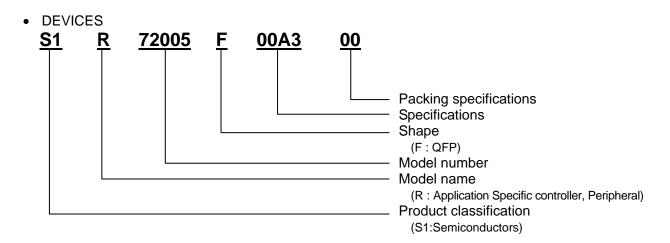

## **Product number format**

## **Table of Contents**

| 1        | DI  | ESCRIPTIC | DN                                                      | 1         |

|----------|-----|-----------|---------------------------------------------------------|-----------|

| <b>2</b> | RI  | EGISTERS  |                                                         | $\dots 2$ |

|          | 2.1 | Register  | Мар                                                     | 2         |

|          | 2.2 | Detailed  | Description of Each Register                            | 8         |

|          | 2   | .2.1 Inte | errupt Main Block                                       |           |

|          |     | 2.2.1.1   | 0x00 Main Interrupt Status0 (MainIntStat_0)             |           |

|          |     | 2.2.1.2   | 0x01 Main Interrupt Status1 (MainIntStat_1)             |           |

|          |     | 2.2.1.3   | 0x02 Host Controller Interrupt Status (HCIntStat)       |           |

|          |     | 2.2.1.4   | 0x03 PipeInterrupt Status (PIPEIntStat)                 |           |

|          |     | 2.2.1.5   | 0x04 Peripheral Controller Interrupt Status (PCIntStat) |           |

|          |     | 2.2.1.6   | 0x05 EndpointInterrupt Status (EPIntStat)               | 15        |

|          |     | 2.2.1.7   | 0x06 (Reserved)                                         | 16        |

|          |     | 2.2.1.8   | 0x07 (Reserved)                                         | 16        |

|          |     | 2.2.1.9   | 0x08 Main Interrupt Enable0 (MainIntEnb_0)              | 17        |

|          |     | 2.2.1.10  | 0x09 Main Interrupt Enable1 (MainIntEnb_1)              | 18        |

|          |     | 2.2.1.11  | 0x0A Host Controller Interrupt Enable (HCIntEnb)        | 19        |

|          |     | 2.2.1.12  | 0x0B PipeInterrupt Enable (PIPEIntEnb)                  | 20        |

|          |     | 2.2.1.13  | 0x0C Peripheral Controller Interrupt Enable (PCIntEnb)  | 21        |

|          |     | 2.2.1.14  | 0x0D EndpointInterrupt Enable (EPIntEnb)                | 22        |

|          |     | 2.2.1.15  | 0x0E (Reserved)                                         | 23        |

|          |     | 2.2.1.16  | 0x0F (Reserved)                                         | 23        |

|          | 2   | .2.2 Pipe | e Interrupt Block                                       | 24        |

|          |     | 2.2.2.1   | 0x10 Pipe0 Interrupt Status (PIPE0IntStat)              | 24        |

|          |     | 2.2.2.2   | 0x11 (Reserved)                                         | 26        |

|          |     | 2.2.2.3   | 0x12 PipeA Interrupt Status (PIPEaIntStat)              | 27        |

|          |     | 2.2.2.4   | 0x13 PipeB Interrupt Status (PIPEbIntStat)              | 29        |

|          |     | 2.2.2.5   | 0x14 PipeC Interrupt Status (PIPEcIntStat)              | 31        |

|          |     | 2.2.2.6   | 0x15 PipeD Interrupt Status (PIPEdIntStat)              | 33        |

|          |     | 2.2.2.7   | 0x16 (Reserved)                                         | 35        |

|          |     | 2.2.2.8   | 0x17 (Reserved)                                         | 36        |

|          |     | 2.2.2.9   | 0x18 Pipe0 Interrupt Enable (PIPE0IntEnb)               | 37        |

|          |     | 2.2.2.10  | 0x19 (Reserved)                                         | 38        |

|          |     | 2.2.2.11  | 0x1A PipeA Interrupt Enable (PIPEaIntEnb)               | 39        |

|          |     | 2.2.2.12  | 0x1B PipeB Interrupt Enable (PIPEbIntEnb)               | 40        |

|          |     | 2.2.2.13  | 0x1C PipeC Interrupt Enable (PIPEcIntEnb)               | 41        |

|          |     | 2.2.2.14  | 0x1D PipeD Interrupt Enable (PIPEdIntEnb)               | 42        |

|          |     | 2.2.2.15  | 0x1E (Reserved)                                         | 43        |

| 2.2.2.16  | 0x1F (Reserved)                                                          |

|-----------|--------------------------------------------------------------------------|

| 2.2.3 En  | dpoint Interrupt Block                                                   |

| 2.2.3.1   | 0x20 Endpoint0 Interrupt Status (EP0IntStat)                             |

| 2.2.3.2   | 0x21 (Reserved)                                                          |

| 2.2.3.3   | 0x22 EndpointA Interrupt Status (EPaIntStat)                             |

| 2.2.3.4   | 0x23 EndpointB Interrupt Status (EPbIntStat)                             |

| 2.2.3.5   | 0x24 EndpointC Interrupt Status (EPcIntStat)                             |

| 2.2.3.6   | 0x25 EndpointD Interrupt Status (EPdIntStat)                             |

| 2.2.3.7   | 0x26 EndpointE Interrupt Status (EPeIntStat)                             |

| 2.2.3.8   | 0x27 (Reserved)                                                          |

| 2.2.3.9   | 0x28 Endpoint0 Interrupt Enable (EP0IntEnb)53                            |

| 2.2.3.10  | 0x29 (Reserved)                                                          |

| 2.2.3.11  | 0x2A EndpointA Interrupt Enable (EPaIntEnb)55                            |

| 2.2.3.12  | 0x2B EndpointB Interrupt Enable (EPbIntEnb)56                            |

| 2.2.3.13  | 0x2C EndpointC Interrupt Enable (EPcIntEnb)57                            |

| 2.2.3.14  | 0x2D EndpointD Interrupt Enable (EPdIntEnb)58                            |

| 2.2.3.15  | 0x2E EndpointE Interrupt Enable (EPeIntEnb)59                            |

| 2.2.3.16  | 0x2F (Reserved)                                                          |

| 2.2.4 Con | mmon Block61                                                             |

| 2.2.4.1   | 0x30 Macro Configuration (MacroConfig)61                                 |

| 2.2.4.2   | 0x31 Revision Number (RevNumber)62                                       |

| 2.2.4.3   | 0x32 Common Control (CommonControl)63                                    |

| 2.2.4.4   | 0x33 Host Controller & Peripheral Controller Common Control (HCPCCommon) |

|           | 65                                                                       |

| 2.2.4.5   | 0x34 OTG Controller Monitor (OTGCMonitor)66                              |

| 2.2.4.6   | 0x35 OTG Controller Control (OTGCControl)                                |

| 2.2.4.7   | 0x36 (Reserved)                                                          |

| 2.2.4.8   | 0x37 Host Controller Control (HCControl)71                               |

| 2.2.4.9   | 0x38 Host Controller Frame Number HIGH (HCFmNumber_H)73                  |

| 2.2.4.10  | 0x39 Host Controller Frame Number LOW (HCFmNumber_L)74                   |

| 2.2.4.11  | 0x3A Peripheral Controller Control (PCControl)75                         |

| 2.2.4.12  | 0x3B Peripheral Controller USB Address (PCUSBAddress)76                  |

| 2.2.4.13  | 0x3C Peripheral Controller Frame Number HIGH (PCFmNumber_H)77            |

| 2.2.4.14  | 0x3D Peripheral Controller Frame Number LOW (PCFmNumber_L)78             |

| 2.2.4.15  | 0x3E Pipe & EndpointCommon (PipeEPCommon)                                |

| 2.2.4.16  | 0x3F EndpointCommon (EPCommon)80                                         |

| 2.2.5 DM  | IA/CPU/Clock Block                                                       |

| 2.2.5.1   | 0x40 DMA Configuration0 (DMAConfig_0)81                                  |

| 2.2.5.2   | 0x41 DMA Configuration1 (DMAConfig_1)                             |           |

|-----------|-------------------------------------------------------------------|-----------|

| 2.2.5.3   | 0x42 DMA Control0 (DMAControl_0)                                  |           |

| 2.2.5.4   | 0x43 DMA Control1 (DMAControl_1)                                  |           |

| 2.2.5.5   | 0x44 (Reserved)                                                   |           |

| 2.2.5.6   | 0x45 DMA Count HIGH (DMACount_H)                                  | 90        |

| 2.2.5.7   | 0x46 DMA Count Middle (DMACount_M)                                | 90        |

| 2.2.5.8   | 0x47 DMA Count LOW (DMACount_L)                                   |           |

| 2.2.5.9   | 0x48 CPU Configuration0 (CPUConfig_0)                             | 92        |

| 2.2.5.10  | 0x49 CPU Configuration1 (CPUConfig_1)                             | 94        |

| 2.2.5.11  | 0x4A Clock Monitor (ClkMonitor)                                   |           |

| 2.2.5.12  | 0x4B Clock Control (ClkControl)                                   |           |

| 2.2.5.13  | 0x4C (Reserved)                                                   | 100       |

| 2.2.5.14  | 0x4D Clock Command (ClkCommand)                                   | 101       |

| 2.2.5.15  | 0x4E (Reserved)                                                   | 102       |

| 2.2.5.16  | 0x4F (Reserved)                                                   | 102       |

| 2.2.6 Con | ntrol Transfer Command Register Block                             |           |

| 2.2.6.1   | 0x50 to 0x57 Pipe0 Setup Command0 to 7 (PIPE0Setup_0 to PIPE0Setu | up_7).103 |

| 2.2.6.2   | 0x58 to 0x5F Endpoint0 Setup0 to 7 (EP0Setup_0 to EP0Setup_7)     | 104       |

| 2.2.7 Ch  | annel0 Control Register Block                                     | 105       |

| 2.2.7.1   | 0x60 Channel0 Configuration0 (0Config_0)                          | 105       |

| 2.2.7.2   | 0x61 Channel0 Configuration1 (0Config_1)                          | 106       |

| 2.2.7.3   | 0x62 Channel0 Max Packet Size HIGH (0MaxPktSize_H)                |           |

| 2.2.7.4   | 0x63 Channel0 Max Packet Size LOW (0MaxPktSize_L)                 | 109       |

| 2.2.7.5   | 0x64 Pipe0 Control Transfer Auto Mode (PIPE0CTLAutoMode)          | 110       |

| 2.2.7.6   | 0x65 Pipe0 Transfer Configuration (PIPE0TranConfig)               | 112       |

| 2.2.7.7   | 0x66 Pipe0 Control (PIPE0Control)                                 | 113       |

| 2.2.7.8   | 0x67 Pipe0 Total Size HIGH (PIPE0TotalSize_H)                     | 115       |

| 2.2.7.9   | 0x68 Pipe0 Total Size Middle (PIPE0TotalSize_M)                   | 115       |

| 2.2.7.10  | 0x69 Pipe0 Total Size LOW (PIPE0TotalSize_L)                      | 115       |

| 2.2.7.11  | 0x6A Endpoint0 Control0 (EP0Control_0)                            | 117       |

| 2.2.7.12  | 0x6B Endpoint0 Control1 (EP0Control_1)                            | 120       |

| 2.2.7.13  | 0x6C Channel0 FIFO for CPU HIGH (0FIFOforCPU_H)                   | 122       |

| 2.2.7.14  | 0x6D Channel0 FIFO for CPU LOW (0FIFOforCPU_L)                    | 123       |

| 2.2.7.15  | 0x6E Channel0 FIFO Control0 (0FIFOControl_0)                      | 124       |

| 2.2.7.16  | 0x6F Channel0 FIFO Control1 (0FIFOControl_1)                      | 126       |

| 2.2.8 Ch  | annelA Control Block                                              | 127       |

| 2.2.8.1   | 0x70 ChannelA Configuration0 (aConfig_0)                          | 127       |

| 2.2.8.2   | 0x71 ChannelA Configuration1 (aConfig_1)                          | 129       |

|   | 2.2.8.3    | 0x72 ChannelA Max Packet Size HIGH (aMaxPktSize_H)                          |          |

|---|------------|-----------------------------------------------------------------------------|----------|

|   | 2.2.8.4    | 0x73 ChannelA Max Packet Size LOW (aMaxPktSize_L)                           |          |

|   | 2.2.8.5    | 0x74 PipeA Interval Time (PIPEaInterval)                                    |          |

|   | 2.2.8.6    | 0x75 PipeA Transfer Configuration (PIPEaTranConfig)                         |          |

|   | 2.2.8.7    | 0x76 PipeA Control (PIPEaControl)                                           |          |

|   | 2.2.8.8    | 0x77 PipeA Total Size HIGH (PIPEaTotalSize_H)                               | 137      |

|   | 2.2.8.9    | 0x78 PipeA Total Size Middle (PIPEaTotalSize_M)                             | 137      |

|   | 2.2.8.10   | 0x79 PipeA Total Size LOW (PIPEaTotalSize_L)                                |          |

|   | 2.2.8.11   | 0x7A EndpointA Control0 (EPaControl_0)                                      |          |

|   | 2.2.8.12   | 0x7B EndpointA Control1 (EPaControl_1)                                      | 141      |

|   | 2.2.8.13   | 0x7C ChannelA FIFO for CPU HIGH (aFIFOforCPU_H)                             |          |

|   | 2.2.8.14   | 0x7D ChannelA FIFO for CPU LOW (aFIFOforCPU_L)                              | 143      |

|   | 2.2.8.15   | 0x7E ChannelA FIFO Control0 (aFIFOControl_0)                                |          |

|   | 2.2.8.16   | 0x7F ChannelA FIFO Control1 (aFIFOControl_1)                                |          |

|   | 2.2.9 Cha  | annelB Register Block                                                       | 147      |

|   | 2.2.10 Cha | annelC Register Block                                                       | 147      |

|   | 2.2.11 Cha | annelD Register Block                                                       |          |

|   | 2.2.12 Cha | annelE Register Block                                                       |          |

|   | 2.2.13 0xH | C1 Extra OTG State Command (E_OTGStateCmd)                                  |          |

|   | 2.2.14 0x0 | 20 to 0xFF Register Blocks                                                  |          |

| 3 | KNOWN PRO  | BLEMS AND CORRECTIVE RESPONSE                                               |          |

|   | 3.1 Known  | Problems When the S1R72005 Operates as a USB Host                           |          |

|   | 3.2 Known  | Problems When the S1R72005 Operates as USB Device                           |          |

|   | 3.2.1 Ste  | ps that May Cause Problems When the $\mathrm{S1R72005}$ Operates as a USB . | Host 150 |

|   | 3.2.2 Bas  | sic Response (Recommended)                                                  | 151      |

| ŀ | REVISION H | HISTORY                                                                     |          |

3

4

## **1 DESCRIPTION**

The S1R72005 is an On-The-Go (OTG) device controller LSI supporting USB2.0-compliant, full-speed (12 Mbps) mode. In addition to both host and peripheral functions, it incorporates OTG functions on one chip, enabling an OTG dual-role device operation.

The S1R72005 Application Note summarizes and provides register information for S1R72005.

#### 2 REGISTERS

## 2.1 Register Map

| بر ام ام     | Registe       | r Name        | bit15          | bit14            | bit13          | bit12             | bit11               | bit10           | bit9             | bit8           |

|--------------|---------------|---------------|----------------|------------------|----------------|-------------------|---------------------|-----------------|------------------|----------------|

| Addr.        | (16bitAccess) | (8bitAccess)  | bit7           | bit6             | bit5           | bit4              | bit3                | bit2            | bit1             | bit0           |

| 0x00         |               | MainIntStat_0 | DetFreezeDMA   | PCIntStat        | HCIntStat      | MainIntStat_1     | DMACmp              | PortErr         | Cross44V         | RcvEP0Setup    |

| 0x01         | MainIntStat   | MainIntStat_1 | DetReset       | DetResume        | DetNonJ        | DetSuspend        | DetRmtWkup          | DetSRP          | ChangeConnStat   | ChangelD       |

| 0x02         | LICIAtOtat    | HCIntStat     |                |                  |                |                   |                     |                 | FmNumberOver     | SOF            |

| 0x03         | HCIntStat     | PIPEIntStat   |                |                  |                | PIPEdIntStat      | PIPEcIntStat        | PIPEbIntStat    | PIPEaIntStat     | PIPE0IntStat   |

| 0x04         | DOIntOtet     | PCIntStat     |                |                  |                |                   |                     |                 |                  | RcvSOF         |

| 0x05         | PCIntStat     | EPIntStat     | INTranCmp      |                  | EPeIntStat     | EPdIntStat        | EPcIntStat          | EPbIntStat      | EPaIntStat       | EP0IntStat     |

| 0x06         | (Decenary)    | (Reserved)    |                |                  |                |                   |                     |                 |                  |                |

| 0x07         | (Reserved)    | (Reserved)    |                |                  |                |                   |                     |                 |                  |                |

| 0x08         | MainlatEab    | MainIntEnb_0  | EnDetFreezeDMA | EnPCIntStat      | EnHCIntStat    | EnMainIntStat_1   | EnDMACmp            | EnPortErr       | EnCross44V       | EnRcvEP0Setup  |

| 0x09         | MainIntEnb    | MainIntEnb_1  | EnDetReset     | EnDetResume      | EnDetNonJ      | EnDetSuspend      | EnDetRmtWkup        | EnDetSRP        | EnChangeConnStat | EnChangeID     |

| 0x0A         | HCIntEnh      | HCIntEnb      |                |                  |                |                   |                     |                 | EnFmNumberOver   | EnSOF          |

| 0x0B         | HCIntEnb      | PIPEIntEnb    |                |                  |                | EnPIPEdIntStat    | EnPIPEcIntStat      | EnPIPEbIntStat  | EnPIPEaIntStat   | EnPIPE0IntStat |

| 0x0C         | DOIntEnh      | PCIntEnb      |                |                  |                |                   |                     |                 |                  | EnRcvSOF       |

| 0x0D         | PCIntEnb      | EPIntEnb      | EnINTranCmp    |                  | EnEPeIntStat   | EnEPdIntStat      | EnEPcIntStat        | EnEPbIntStat    | EnEPaIntStat     | EnEP0IntStat   |

| 0x0E         | (5            | (Reserved)    |                |                  |                |                   |                     |                 |                  |                |

| 0x0F         | (Reserved)    | (Reserved)    |                |                  |                |                   |                     |                 |                  |                |

|              |               |               |                |                  |                |                   |                     |                 |                  |                |

| 0x10         |               | PIPE0IntStat  | PIPE0TranCmp   | CTLTranCmp       |                | PIPE0InShortRcv   | PIPE0InOverSize     | PIPE0TranErr    | PIPE0Stalled     | PIPE0NoResp    |

| 0x11         | PIPE0IntStat  | (Reserved)    |                |                  |                |                   |                     |                 |                  |                |

| 0x12         |               | PIPEaIntStat  | PIPEaTranCmp   |                  |                | PIPEaInShortRcv   | PIPEaInOverSize     | PIPEaTranErr    | PIPEaStalled     | PIPEaNoResp    |

| 0x13         | PIPEabIntStat | PIPEbIntStat  | PIPEbTranCmp   |                  |                | PIPEbInShortRcv   | PIPEbInOverSize     | PIPEbTranErr    | PIPEbStalled     | PIPEbNoResp    |

| 0x14         |               | PIPEcIntStat  | PIPEcTranCmp   |                  |                | PIPEcInShortRcv   | PIPEcInOverSize     | PIPEcTranErr    | PIPEcStalled     | PIPEcNoResp    |

| 0x15         | PIPEcdIntStat | PIPEdIntStat  | PIPEdTranCmp   |                  |                | PIPEdInShortRcv   | PIPEdInOverSize     | PIPEdTranErr    | PIPEdStalled     | PIPEdNoResp    |

| 0x16         |               | (Reserved)    |                |                  |                |                   |                     |                 |                  |                |

| 0x17         | (Reserved)    | (Reserved)    |                |                  |                |                   |                     |                 |                  |                |

| 0x18         |               | PIPE0IntEnb   | EnPIPE0TranCmp | EnCTLTranCmp     |                | EnPIPE0InShortRcv | EnPIPE0InOverSize   | EnPIPE0TranErr  | EnPIPE0Stalled   | EnPIPE0NoResp  |

| 0x19         | PIPE0IntEnb   | (Reserved)    |                |                  |                |                   |                     |                 |                  |                |

| 0x1A         |               | PIPEaIntEnb   | EnPIPEaTranCmp |                  |                | EnPIPEaInShortRcv | EnPIPEaInOverSize   | EnPIPEaTranErr  | EnPIPEaStalled   | EnPIPEaNoResp  |

| 0x1B         | PIPEabIntEnb  | PIPEbIntEnb   | EnPIPEbTranCmp |                  |                | EnPIPEbInShortRcv | EnPIPEbInOverSize   | EnPIPEbTranErr  | EnPIPEbStalled   | EnPIPEbNoResp  |

| 0x1C         |               | PIPEcIntEnb   | EnPIPEcTranCmp |                  |                | EnPIPEcInShortRcv | EnPIPEcInOverSize   | EnPIPEcTranErr  | EnPIPEcStalled   | EnPIPEcNoResp  |

| 0x1D         | PIPEcdIntEnb  | PIPEdIntEnb   | EnPIPEdTranCmp |                  |                | EnPIPEdInShortRcv | EnPIPEdInOverSize   | EnPIPEdTranErr  | EnPIPEdStalled   | EnPIPEdNoResp  |

| 0x1E         |               | (Reserved)    |                |                  |                |                   |                     |                 |                  |                |

| 0x1F         | (Reserved)    | (Reserved)    |                |                  |                |                   |                     |                 |                  |                |

|              | 1             |               |                |                  |                |                   |                     |                 |                  | 1              |

| 0x20         |               | EP0IntStat    |                |                  | EP0INTranACK   | EP00UTTranACK     | <b>EP0INTranNAK</b> | EP00UTTranNAK   | EP0INTranErr     | EP0OUTTranErr  |

| 0x21         | EP0IntStat    | (Reserved)    |                |                  |                |                   |                     |                 |                  |                |

| 0x22         |               | EPaIntStat    |                | EPaOUTShortACK   | EPaINTranACK   | EPaOUTTranACK     | EPaINTranNAK        | EPaOUTTranNAK   | EPaINTranErr     | EPaOUTTranErr  |

| 0x23         | EPabIntStat   | EPbIntStat    |                | EPbOUTShortACK   | EPbINTranACK   | EPbOUTTranACK     | EPbINTranNAK        | EPbOUTTranNAK   | EPbINTranErr     | EPbOUTTranErr  |

| 0x24         |               | EPcIntStat    |                | EPcOUTShortACK   | EPcINTranACK   | EPcOUTTranACK     | EPcINTranNAK        | EPcOUTTranNAK   | EPcINTranErr     | EPcOUTTranErr  |

| 0x25         | EPcdIntStat   | EPdIntStat    |                | EPdOUTShortACK   | EPdINTranACK   | EPdOUTTranACK     | EPdINTranNAK        | EPdOUTTranNAK   | EPdINTranErr     | EPdOUTTranErr  |

| 0x26         |               | EPeIntStat    |                | EPeOUTShortACK   | EPeINTranACK   | EPeOUTTranACK     | EPeINTranNAK        | EPeOUTTranNAK   | EPelNTranErr     | EPeOUTTranErr  |

| 0x27         | EPeIntStat    | (Reserved)    |                |                  |                |                   |                     |                 |                  |                |

| 0x28         |               | EP0IntEnb     |                |                  | EnEP0INTranACK | EnEP0OUTTranACK   | EnEP0INTranNAK      | EnEP0OUTTranNAK | EnEP0INTranErr   | EnEP0OUTTranEr |

| 0x29         | EP0IntEnb     | (Reserved)    |                |                  |                |                   |                     |                 |                  |                |

| 0x2A         |               | EPaIntEnb     |                | EnEPaOUTShortACK | EnEPaINTranACK | EnEPaOUTTranACK   | EnEPaINTranNAK      | EnEPaOUTTranNAK | EnEPaINTranErr   | EnEPaOUTTranEr |

| 0x2B         | EPabIntEnb    | EPbIntEnb     |                | EnEPbOUTShortACK | EnEPbINTranACK | EnEPbOUTTranACK   | EnEPbINTranNAK      | EnEPbOUTTranNAK | EnEPbINTranErr   | EnEPbOUTTranEr |

| 0x2C         |               | EPcIntEnb     |                | EnEPcOUTShortACK | EnEPcINTranACK | EnEPcOUTTranACK   | EnEPcINTranNAK      | EnEPcOUTTranNAK | EnEPcINTranErr   | EnEPcOUTTranEr |

| 0x2D         | EPcdIntEnb    | EPdIntEnb     |                | EnEPdOUTShortACK | EnEPdINTranACK | EnEPdOUTTranACK   | EnEPdINTranNAK      | EnEPdOUTTranNAK | EnEPdINTranErr   | EnEPdOUTTranEr |

| 0x2D<br>0x2E |               | EPeIntEnb     |                | EnEPeOUTShortACK | EnEPelNTranACK | EnEPeOUTTranACK   | EnEPelNTranNAK      | EnEPeOUTTranNAK | EnEPeINTranErr   | EnEPeOUTTranEr |

|              | EPeIntEnb     | (Reserved)    | l              |                  |                |                   |                     |                 | _ner on tranell  |                |

## 0x30 to 0x5F

| Addr. | Registe        | r Name        | bit15           | bit14          | bit13 | bit12          | bit11           | bit10           | bit9             | bit8          |  |  |  |

|-------|----------------|---------------|-----------------|----------------|-------|----------------|-----------------|-----------------|------------------|---------------|--|--|--|

| Addr. | (16bitAccess)  | (8bitAccess)  | bit7            | bit6           | bit5  | bit4           | bit3            | bit2            | bit1             | bit0          |  |  |  |

| 0x30  | MacroConfig    | MacroConfig   |                 |                |       | COMPPwrDown    |                 |                 |                  | ExtResMode    |  |  |  |

| 0x31  | Macrocoring    | RevNumber     |                 | RevNumber[7:0] |       |                |                 |                 |                  |               |  |  |  |

| 0x32  | CommonControl  | CommonControl |                 |                |       | ResetXcvr      | ResetPC         | ResetHC         | ResetOTGC        | ResetALL      |  |  |  |

| 0x33  | CommonControl  | HCPCCommon    |                 |                |       |                |                 |                 | OpMode[2:0]      |               |  |  |  |

| 0x34  | OTGCCommon     | OTGCMonitor   | LSConnect       | ID             | Lines | State[1:0]     |                 |                 | Comp20V          | Comp44V       |  |  |  |

| 0x35  | Orgecommon     | OTGCControl   | AllowRmtWkup    |                |       | BusPwrSel      |                 | OTGState        | eCmd[3:0]        |               |  |  |  |

| 0x36  | HCCommon       | (Reserved)    |                 |                |       |                |                 |                 |                  |               |  |  |  |

| 0x37  | HCCommon       | HCControl     |                 |                |       | EnNoFmBulkMode |                 | HCStateCmd[1:0] |                  |               |  |  |  |

| 0x38  | HCFmNumber     | HCFmNumber_H  |                 |                |       |                |                 |                 | HCFmNumber[10:8] |               |  |  |  |

| 0x39  | HCFMNumber     | HCFmNumber_L  | HCFmNumber[7:0] |                |       |                |                 |                 |                  |               |  |  |  |

| 0x3A  | PCCommon       | PCControl     |                 |                |       |                |                 |                 |                  | SendWakeup    |  |  |  |

| 0x3B  | PCCommon       | PCUSBAddress  |                 |                |       |                | USBAddress[6:0] |                 |                  |               |  |  |  |

| 0x3C  | DOF            | PCFmNumber_H  | FnInValid       |                |       |                |                 |                 | PCFmNumber[10:8] |               |  |  |  |

| 0x3D  | PCFmNumber     | PCFmNumber_L  | PCFmNumber[7:0] |                |       |                |                 |                 |                  |               |  |  |  |

| 0x3E  | DisaFDCommun   | PipeEPCommon  |                 |                |       |                |                 |                 |                  | SetBuffer     |  |  |  |

| 0x3F  | PipeEPCommon - | EPCommon      |                 |                |       |                |                 | AutoEnShort     | ALLForceNAK      | EPrForceSTALL |  |  |  |

| 0x40 | DMAConfig                      | DMAConfig_0  |               | DINLate         | ency[4:0]       |             |              | DOUTLa       | tency[4:0] |            |  |  |  |  |

|------|--------------------------------|--------------|---------------|-----------------|-----------------|-------------|--------------|--------------|------------|------------|--|--|--|--|

| 0x41 | DIVIACONING                    | DMAConfig_1  | ActiveDMA     | DMAClkPhase     | DMATran         | Mode[1:0]   | DREQLevel    | DMAEndian    | StrobeMode | DMABus8x16 |  |  |  |  |

| 0x42 | DMAControl                     | DMAControl_0 |               |                 | BurstFIFORemain |             |              |              | BurstLe    | ngth[1:0]  |  |  |  |  |

| 0x43 | DIMACONITO                     | DMAControl_1 | DMAAbort      |                 |                 |             |              |              |            | DMAGo      |  |  |  |  |

| 0x44 | DMACount H                     | (Reserved)   |               |                 |                 |             |              |              |            |            |  |  |  |  |

| 0x45 | DIMACOUNT_H                    | DMACount_H   |               |                 |                 | DMACou      | unt[23:16]   |              |            |            |  |  |  |  |

| 0x46 | DMACount L                     | DMACount_M   |               | DMACount[15:8]  |                 |             |              |              |            |            |  |  |  |  |

| 0x47 | DWACOUNT_L                     | DMACount_L   | DMACount[7:0] |                 |                 |             |              |              |            |            |  |  |  |  |

| 0x48 | CPUConfig                      | CPUConfig_0  |               | WaitPortDisable | WaitMode        | IntMode     |              | CPUEndian    |            | CPUBus8x16 |  |  |  |  |

| 0x49 | Croconing                      | CPUConfig_1  |               | WaitPortDisable | WaitMode        | IntMode     |              | CPUEndian    |            | CPUBus8x16 |  |  |  |  |

| 0x4A | ClkControl                     | ClkMonitor   |               |                 |                 |             | CPUCIkActive | PLLCIkActive | EnPLL      | EnOSC      |  |  |  |  |

| 0x4B | CIRCONID                       | ClkControl   | OSCWakel      | JpTime[1:0]     | PLLWakeU        | lpTime[1:0] | HCSleep      | PCSleep      | MainSleep  | XcvrSleep  |  |  |  |  |

| 0x4C | ClkCommond                     | (Reserved)   |               |                 |                 |             |              |              |            |            |  |  |  |  |

| 0x4D | <ul> <li>ClkCommand</li> </ul> | ClkCommand   |               |                 |                 | ClkComr     | mand[7:0]    |              |            |            |  |  |  |  |

| 0x4E | (Reserved)                     | (Reserved)   |               |                 |                 |             |              |              |            |            |  |  |  |  |

| 0x4F | (iveselveu)                    | (Reserved)   |               |                 |                 |             |              |              |            |            |  |  |  |  |

| 0x50 | PIPE0Setup_0  | PIPE0Setup_0 | PIPE0Setup_0[7:0] |

|------|---------------|--------------|-------------------|

| 0x51 | FIF E0Setup_0 | PIPE0Setup_1 | PIPE0Setup_1[7:0] |

| 0x52 | PIPE0Setup_2  | PIPE0Setup_2 | PIPE0Setup_2[7:0] |

| 0x53 | FIF E03etup_2 | PIPE0Setup_3 | PIPE0Setup_3[7:0] |

| 0x54 | PIPE0Setup_4  | PIPE0Setup_4 | PIPE0Setup_4[7:0] |

| 0x55 | FIFE0Setup_4  | PIPE0Setup_5 | PIPE0Setup_5[7:0] |

| 0x56 | PIPE0Setup_6  | PIPE0Setup_6 | PIPE0Setup_6[7:0] |

| 0x57 | PIPE0Setup_6  | PIPE0Setup_7 | PIPE0Setup_7[7:0] |

| 0x58 | EP0Setup_0    | EP0Setup_0   | EP0Setup_0[7:0]   |

| 0x59 | Er obeidp_o   | EP0Setup_1   | EP0Setup_1[7:0]   |

| 0x5A | EP0Setup_2    | EP0Setup_2   | EP0Setup_2[7:0]   |

| 0x5B | Er obeiup_z   | EP0Setup_3   | EP0Setup_3[7:0]   |

| 0x5C | EP0Setup_4    | EP0Setup_4   | EP0Setup_4[7:0]   |

| 0x5D | EF03etup_4    | EP0Setup_5   | EP0Setup_5[7:0]   |

| 0x5E | EP0Setup_6    | EP0Setup_6   | EP0Setup_6[7:0]   |

| 0x5F | Er 05etup_0   | EP0Setup_7   | EP0Setup_7[7:0]   |

## 0x60 to 0x8F

| م ما ما بر | Registe          | r Name               | bit15            | bit14        | bit13         | bit12           | bit11            | bit10        | bit9                 | bit8          |  |  |

|------------|------------------|----------------------|------------------|--------------|---------------|-----------------|------------------|--------------|----------------------|---------------|--|--|

| Addr.      | (16bitAccess)    | (8bitAccess)         | bit7             | bit6         | bit5          | bit4            | bit3             | bit2         | bit1                 | bit0          |  |  |

| 0x60       | 0Config          | 0Config_0            | JoinDMA          | FIFOCIr      |               |                 |                  |              |                      |               |  |  |

| 0x61       | oconing          | 0Config_1            | DirPl            | D[1:0]       |               |                 |                  | EPNum        | nber[3:0]            |               |  |  |

| 0x62       | 0MaxPktSize      | 0MaxPktSize_H        |                  |              |               | BufferPage[4:0] |                  |              |                      |               |  |  |

| 0x63       | UMaxPKISIZe      | 0MaxPktSize_L        |                  |              |               |                 | MaxPktSize[6:0]  |              |                      |               |  |  |

| 0x64       | PIPE0Control 0   | PIPE0CTLAutoMod<br>e |                  |              |               |                 |                  | DataStageDir | NoDataStage          | EnCTLAuto     |  |  |

| 0x65       | 1 11 200011101_0 | PIPE0TranConfig      |                  |              | FuncAddr[2:0] |                 |                  |              |                      |               |  |  |

| 0x66       | PIPE0Control_1   | PIPE0Control         |                  |              |               | Toggle          |                  |              |                      | TranGo        |  |  |

| 0x67       | FIFE0C01001_1    | PIPE0TotalSize_H     | TotalSize[23:16] |              |               |                 |                  |              |                      |               |  |  |

| 0x68       |                  | PIPE0TotalSize_M     |                  |              |               | Totals          | Size[15:8]       |              |                      |               |  |  |

| 0x69       | PIPE0Control_2   | PIPE0TotalSize_L     | TotalSize[7:0]   |              |               |                 |                  |              |                      |               |  |  |

| 0x6A       | EP0Control       | EP0Control_0         |                  | AutoForceNAK | InEnShortPkt  |                 | InForceNAK       | InForceSTALL | OutForceNAK          | OutForceSTALL |  |  |

| 0x6B       | EPOCOntrol       | EP0Control_1         | InToggleStat     |              | InToggleSet   | InToggleClr     | OutToggleStat    |              | OutToggleSet         | OutToggleClr  |  |  |

| 0x6C       | 0FIFOforCPU      | 0FIFOforCPU_H        |                  |              |               |                 |                  |              |                      |               |  |  |

| 0x6D       | OFIFOIOICPU      | 0FIFOforCPU_L        |                  |              |               | FIFOfo          | rCPU[7:0]        |              |                      |               |  |  |

| 0x6E       | 0FIFOControl     | 0FIFOControl_0       | FIFOEmpty        | FIFOFull     | EnFIFOwr      | EnFIFOrd        | EnFIFOByteAccess | F            | FIFODataRemain[10:8] |               |  |  |

| 0x6F       | UFIFUCONTIO      | 0FIFOControl_1       |                  | •            | -             | FIFOData        | Remain[7:0]      |              |                      |               |  |  |

| 0x70 | aConfig         | aConfig_0        | JoinDMA            | FIFOCIr                        | ToggleMode | AutoZeroLen       |                  |   |                     |            |  |

|------|-----------------|------------------|--------------------|--------------------------------|------------|-------------------|------------------|---|---------------------|------------|--|

| 0x71 | acomig          | aConfig_1        | DirPll             | D[1:0]                         | TranTy     | /pe[1:0]          | EPNumber[3:0]    |   |                     |            |  |

| 0x72 | aMaxPktSize     | aMaxPktSize_H    |                    | BufferPage[4:0] MaxPktSize[9:6 |            |                   |                  |   |                     |            |  |

| 0x73 | awaxr ktoize    | aMaxPktSize_L    |                    | MaxPktSize[7:0]                |            |                   |                  |   |                     |            |  |

| 0x74 | PIPEaControl 0  | PIPEaInterval    |                    |                                |            | Interv            | al[7:0]          |   |                     |            |  |

| 0x75 | FIFEaCOIIIIOI_0 | PIPEaTranConfig  |                    | Continuity[2:0] F              |            |                   |                  |   |                     |            |  |

| 0x76 | PIPEaControl 1  | PIPEaControl     |                    |                                |            | Toggle            |                  |   |                     | TranGo     |  |

| 0x77 | FIFEaCOIIIIOI_I | PIPEaTotalSize_H |                    |                                |            | TotalSiz          |                  |   |                     |            |  |

| 0x78 | PIPEaControl 2  | PIPEaTotalSize_M |                    |                                |            | TotalSi           | ze[15:8]         |   |                     |            |  |

| 0x79 | FIFEaCOIIII0I_2 | PIPEaTotalSize_L | TotalSize[7:0]     |                                |            |                   |                  |   |                     |            |  |

| 0x7A | EPaControl      | EPaControl_0     | EnEndPoint         | AutoForceNAK                   | EnShortPkt | AutoForceNAKShort |                  |   | ForceNAK            | ForceSTALL |  |

| 0x7B | LFacontion      | EPaControl_1     |                    |                                |            |                   | ToggleStat       |   | ToggleSet           | ToggleClr  |  |

| 0x7C | aFIFOforCPU     | aFIFOforCPU_H    |                    |                                |            | FIFOforC          | PU[15:8]         |   |                     |            |  |

| 0x7D | aFIFOIDICFU     | aFIFOforCPU_L    | _L FIFOforCPU[7:0] |                                |            |                   |                  |   |                     |            |  |

| 0x7E | aFIFOControl    | aFIFOControl_0   | FIFOEmpty          | FIFOFull                       | EnFIFOwr   | EnFIFOrd          | EnFIFOByteAccess | F | FIFODataRemain[10:8 | 3]         |  |

| 0x7F |                 | aFIFOControl_1   |                    |                                |            | FIFODataF         | Remain[7:0]      |   |                     |            |  |

| 0x80 | bConfig        | bConfig_0        | JoinDMA        | FIFOCIr                       | ToggleMode      | AutoZeroLen       |                  |                   |            |  |  |  |  |

|------|----------------|------------------|----------------|-------------------------------|-----------------|-------------------|------------------|-------------------|------------|--|--|--|--|

| 0x81 | bConing        | bConfig_1        | DirPl          | D[1:0]                        | TranType[1:0]   |                   | EPNumber[3:0]    |                   |            |  |  |  |  |

| 0x82 | bMaxPktSize    | bMaxPktSize_H    |                | BufferPage[4:0] MaxPktSize[9: |                 |                   |                  |                   |            |  |  |  |  |

| 0x83 | Diviaxi KiGize | bMaxPktSize_L    |                | MaxPktSize(7:0)               |                 |                   |                  |                   |            |  |  |  |  |

| 0x84 | PIPEbControl 0 | PIPEbInterval    |                | Interval[7:0]                 |                 |                   |                  |                   |            |  |  |  |  |

| 0x85 | FIFEbcontrol_0 | PIPEbTranConfig  |                |                               | Continuity[2:0] |                   |                  | FuncAddr[2:0]     |            |  |  |  |  |

| 0x86 | PIPEbControl 1 | PIPEbControl     |                |                               |                 | Toggle            |                  |                   | TranGo     |  |  |  |  |

| 0x87 | FIFEbconator_1 | PIPEbTotalSize_H |                |                               |                 | TotalSiz          | ze[23:16]        |                   |            |  |  |  |  |

| 0x88 | PIPEbControl 2 | PIPEbTotalSize_M |                |                               |                 | TotalSi           | ze[15:8]         |                   |            |  |  |  |  |

| 0x89 | FIFEDCOILLOI_2 | PIPEbTotalSize_L | TotalSize[7:0] |                               |                 |                   |                  |                   |            |  |  |  |  |

| 0x8A | EPbControl     | EPbControl_0     | EnEndPoint     | AutoForceNAK                  | EnShortPkt      | AutoForceNAKShort |                  | ForceNAK          | ForceSTALL |  |  |  |  |

| 0x8B | Erbeonitor     | EPbControl_1     |                |                               |                 |                   | ToggleStat       | ToggleSet         | ToggleClr  |  |  |  |  |

| 0x8C | bFIFOforCPU    | bFIFOforCPU_H    |                |                               |                 | FIFOfor           | CPU[15:8]        |                   |            |  |  |  |  |

| 0x8D | DFIFOIDICFO    | bFIFOforCPU_L    |                |                               |                 | FIFOfor           | CPU[7:0]         |                   |            |  |  |  |  |

| 0x8E | bFIFOControl   | bFIFOControl_0   | FIFOEmpty      | FIFOFull                      | EnFIFOwr        | EnFIFOrd          | EnFIFOByteAccess | FIFODataRemain[10 | :8]        |  |  |  |  |

| 0x8F | 51 II CCONIIO  | bFIFOControl_1   |                |                               |                 | FIFODataF         | Remain[7:0]      |                   |            |  |  |  |  |

## 0x90 to 0xBF

| Addr. | Registe        | r Name               | bit15            | bit14                                                   | bit13         | bit12              | bit11       | bit10 | bit9      | bit8            |  |  |

|-------|----------------|----------------------|------------------|---------------------------------------------------------|---------------|--------------------|-------------|-------|-----------|-----------------|--|--|

| Addr. | (16bitAccess)  | (8bitAccess)         | bit7             | bit6                                                    | bit5          | bit4               | bit3        | bit2  | bit1      | bit0            |  |  |

| 0x90  | cConfig        | cConfig_0            | JoinDMA          | FIFOCIr                                                 | ToggleMode    | AutoZeroLen        |             |       |           |                 |  |  |

| 0x91  | cooning        | cConfig_1            | DirPl            | D[1:0]                                                  | TranT         | ype[1:0]           |             | EPNur | mber[3:0] |                 |  |  |

| 0x92  | cMaxPktSize    | cMaxPktSize_H        |                  | BufferPage[4:0]                                         |               |                    |             |       |           | MaxPktSize[9:8] |  |  |

| 0x93  | CIVIAXPRISIZE  | cMaxPktSize_L        |                  | MaxPktSize[7:0]                                         |               |                    |             |       |           |                 |  |  |

| 0x94  | PIPEcControl 0 | PIPEcInterval        |                  |                                                         |               | Interv             | al[7:0]     |       |           |                 |  |  |

| 0x95  | PIPECCONTOL_0  | PIPEcTranConfig      |                  |                                                         | FuncAddr[2:0] |                    |             |       |           |                 |  |  |

| 0x96  |                | PIPEcControl         |                  |                                                         |               | Toggle             |             |       |           | TranGo          |  |  |

| 0x97  | PIPEcControl_1 | PIPEcTotalSize_H     | TotalSize[23:16] |                                                         |               |                    |             |       |           |                 |  |  |

| 0x98  | PIPEcControl 2 | PIPEcTotalSize_<br>M |                  |                                                         |               | TotalSiz           | ze[15:8]    |       |           |                 |  |  |

| 0x99  |                | PIPEcTotalSize_L     | TotalSize[7:0]   |                                                         |               |                    |             |       |           |                 |  |  |

| 0x9A  | EPcControl     | EPcControl_0         | EnEndPoint       | AutoForceNAK                                            | EnShortPkt    | AutoForceNAKShort  |             |       | ForceNAK  | ForceSTALL      |  |  |

| 0x9B  | EPCCOntrol     | EPcControl_1         |                  |                                                         |               |                    | ToggleStat  |       | ToggleSet | ToggleClr       |  |  |

| 0x9C  | cFIFOforCPU    | cFIFOforCPU_H        |                  | FIFOforCPU[15:8]                                        |               |                    |             |       |           |                 |  |  |

| 0x9D  | CEIEOIOICEO    | cFIFOforCPU_L        | FIFOforCPU[7:0]  |                                                         |               |                    |             |       |           |                 |  |  |

| 0x9E  | cFIFOControl   | cFIFOControl_0       | FIFOEmpty        | FOEmpty FIFOFull EnFIFOwr EnFIFOrd EnFIFOByteAccess FIF |               | FIFODataRemain[10: | 8]          |       |           |                 |  |  |

| 0x9F  | CFIFUCONTION   | cFIFOControl_1       |                  | •                                                       | -             | FIFODataF          | Remain[7:0] |       |           |                 |  |  |

| 0xA0 | dConfig         | dConfig_0        | JoinDMA    | FIFOCIr             | ToggleMode      | AutoZeroLen       |                  |   |                     |            |

|------|-----------------|------------------|------------|---------------------|-----------------|-------------------|------------------|---|---------------------|------------|

| 0xA1 | aconing         | dConfig_1        | DirPI      | D[1:0]              | TranTy          | TranType[1:0]     |                  |   | iber[3:0]           |            |

| 0xA2 | dMaxPktSize     | dMaxPktSize_H    |            | BufferPage[4:0]     |                 |                   |                  |   | MaxPkt              | Size[9:8]  |

| 0xA3 | UNIAXI' KUSIZE  | dMaxPktSize_L    |            |                     |                 | MaxPkt            | Size[7:0]        |   |                     |            |

| 0xA4 | PIPEdControl 0  | PIPEdInterval    |            |                     |                 | Interv            | al[7:0]          |   |                     |            |

| 0xA5 | Fir Edeonator_o | PIPEdTranConfig  |            |                     | Continuity[2:0] |                   |                  |   | FuncAddr[2:0]       |            |

| 0xA6 | PIPEdControl_1  | PIPEdControl     |            |                     |                 | Toggle            |                  |   |                     | TranGo     |

| 0xA7 | FIFEdControl_1  | PIPEdTotalSize_H |            | TotalSize[23:16]    |                 |                   |                  |   |                     |            |

| 0xA8 | PIPEdControl 2  | PIPEdTotalSize_M |            |                     |                 | TotalSi           | ze[15:8]         |   |                     |            |

| 0xA9 | FIFEdControl_2  | PIPEdTotalSize_L |            |                     |                 | TotalS            | ize[7:0]         |   |                     |            |

| 0xAA | EPdControl      | EPdControl_0     | EnEndPoint | AutoForceNAK        | EnShortPkt      | AutoForceNAKShort |                  |   | ForceNAK            | ForceSTALL |

| 0xAB | Erdeontio       | EPdControl_1     |            |                     |                 |                   | ToggleStat       |   | ToggleSet           | ToggleClr  |

| 0xAC | dFIFOforCPU     | dFIFOforCPU_H    |            | FIFOforCPU[15:8]    |                 |                   |                  |   |                     |            |

| 0xAD | GEIFOIDICEO     | dFIFOforCPU_L    |            | FIFOforCPU[7:0]     |                 |                   |                  |   |                     |            |

| 0xAE | dFIFOControl    | dFIFOControl_0   | FIFOEmpty  | FIFOFull            | EnFIFOwr        | EnFIFOrd          | EnFIFOByteAccess | F | FIFODataRemain[10:8 | 3]         |

| 0xAF |                 | dFIFOControl_1   |            | FIFODataRemain[7:0] |                 |                   |                  |   |                     |            |

| 0xB0 | eConfig        | eConfig_0                         | JoinDMA    | FIFOCIr             | ToggleMode      | AutoZeroLen       |                  |   |                     |            |

|------|----------------|-----------------------------------|------------|---------------------|-----------------|-------------------|------------------|---|---------------------|------------|

| 0xB1 | econing        | eConfig_1                         | DirPl      | D[1:0]              | TranT           | TranType[1:0] E   |                  |   | lumber[3:0]         |            |

| 0xB2 | eMaxPktSize    | eMaxPktSize_H                     |            |                     |                 | BufferPage[4:0]   |                  |   | MaxPkt              | Size[9:8]  |

| 0xB3 | elviaxi ktoize | eMaxPktSize_L                     |            |                     |                 | MaxPkt            | Size[7:0]        |   |                     |            |

| 0xB4 | PIPEeControl 0 | PIPEeInterval                     |            |                     |                 | Interv            | al[7:0]          |   |                     |            |

| 0xB5 | FIF Lecondo_0  | PIPEeTranConfig                   |            |                     | Continuity[2:0] |                   |                  |   | FuncAddr[2:0]       |            |

| 0xB6 | PIPEeControl 1 | PIPEeControl                      |            |                     |                 | Toggle            |                  |   |                     | TranGo     |

| 0xB7 | FIF Lecondo_1  | PIPEeTotalSize_H                  |            | TotalSize[23:16]    |                 |                   |                  |   |                     |            |

| 0xB8 | PIPEeControl 2 | PIPEeTotalSize_M                  |            | TotalSize(15:8)     |                 |                   |                  |   |                     |            |

| 0xB9 | FIFEeContio_2  | PIPEeTotalSize_L                  |            |                     |                 | TotalSi           | ze[7:0]          |   |                     |            |

| 0xBA | EPeControl     | EPeControl_0                      | EnEndPoint | AutoForceNAK        | EnShortPkt      | AutoForceNAKShort |                  |   | ForceNAK            | ForceSTALL |

| 0xBB | Erecontion     | EPeControl_1                      |            |                     |                 |                   | ToggleStat       |   | ToggleSet           | ToggleClr  |

| 0xBC | eFIFOforCPU    | eFIFOforCPU_H                     |            | FIFOforCPU[15:8]    |                 |                   |                  |   |                     |            |

| 0xBD |                | eFIFOforCPU_L                     |            | FIFOforCPU[7:0]     |                 |                   |                  |   |                     |            |

| 0xBE | eFIFOControl   | eFIFOControl_0 FIFOEmpty FIFOFull |            |                     | EnFIFOwr        | EnFIFOrd          | EnFIFOByteAccess | F | FIFODataRemain[10:8 | 3]         |

| 0xBF |                | eFIFOControl_1                    |            | FIFODataRemain[7:0] |                 |                   |                  |   |                     |            |

## 0xC0 to 0xEF

| Addr.        | Registe       | r Name       | bit15 | bit14 | bit13 | bit12 | bit11 | bit10 | bit9 | bit8 |

|--------------|---------------|--------------|-------|-------|-------|-------|-------|-------|------|------|

| Auur.        | (16bitAccess) | (8bitAccess) | bit7  | bit6  | bit5  | bit4  | bit3  | bit2  | bit1 | bit0 |

| 0xC0         | (Reserved)    | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xC1         | (Iteselved)   | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xC2         | (Reserved)    | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xC3         | (iteseived)   | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xC4         | (Reserved)    | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xC5         | (Reserved)    | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xC6         | (Reserved)    | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xC7         | (Reserved)    | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xC8         | (Reserved)    | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xC9         | (Reserved)    | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xCA         | (Reserved)    | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xCB         | (Reserved)    | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xCC         | (Reserved)    | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xCD         | (Reserved)    | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xCE<br>0xCF | (Reserved)    | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xCF         | (Reserved)    | (Reserved)   |       |       |       |       |       |       |      |      |

|      |            | · · · · · · · · · · · · · · · · · · · |  |  |  |  |

|------|------------|---------------------------------------|--|--|--|--|

| 0xD0 | (Reserved) | (Reserved)                            |  |  |  |  |

| 0xD1 | (reserved) | (Reserved)                            |  |  |  |  |

| 0xD2 | (Reserved) | (Reserved)                            |  |  |  |  |

| 0xD3 | (Reserved) | (Reserved)                            |  |  |  |  |

| 0xD4 | (Reserved) | (Reserved)                            |  |  |  |  |

| 0xD5 | (Reserved) | (Reserved)                            |  |  |  |  |

| 0xD6 | (Reserved) | (Reserved)                            |  |  |  |  |

| 0xD7 | (Reserved) | (Reserved)                            |  |  |  |  |

| 0xD8 | (Reserved) | (Reserved)                            |  |  |  |  |

| 0xD9 | (Reserved) | (Reserved)                            |  |  |  |  |

| 0xDA | (Reserved) | (Reserved)                            |  |  |  |  |

| 0xDB | (Reserved) | (Reserved)                            |  |  |  |  |

| 0xDC | (Reserved) | (Reserved)                            |  |  |  |  |

| 0xDD | (Reserved) | (Reserved)                            |  |  |  |  |

| 0xDE | (Reserved) | (Reserved)                            |  |  |  |  |

| 0xDF | (Reserved) | (Reserved)                            |  |  |  |  |

| 0xE0 |               | (Reserved)    |  |           |             |           |  |  |  |

|------|---------------|---------------|--|-----------|-------------|-----------|--|--|--|

| 0xE1 | E_OTGStateCmd | E_OTGStateCmd |  | E_OTGStat | teCmd [7:0] | Cmd [7:0] |  |  |  |

| 0xE2 | ( <b>7</b> )) | (Reserved)    |  |           |             |           |  |  |  |

| 0xE3 | (Reserved)    | (Reserved)    |  |           |             |           |  |  |  |

| 0xE4 | (Reserved)    | (Reserved)    |  |           |             |           |  |  |  |

| 0xE5 | (Reserved)    | (Reserved)    |  |           |             |           |  |  |  |

| 0xE6 | (Reserved)    | (Reserved)    |  |           |             |           |  |  |  |

| 0xE7 | (Iteserved)   | (Reserved)    |  |           |             |           |  |  |  |

| 0xE8 | (Reserved)    | (Reserved)    |  |           |             |           |  |  |  |

| 0xE9 | (Reserved)    | (Reserved)    |  |           |             |           |  |  |  |

| 0xEA | (Reserved)    | (Reserved)    |  |           |             |           |  |  |  |

| 0xEB | (Reactived)   | (Reserved)    |  |           |             |           |  |  |  |

| 0xEC | (Reserved)    | (Reserved)    |  |           |             |           |  |  |  |

| 0xED | (1.000.100)   | (Reserved)    |  |           |             |           |  |  |  |

| 0xEE | (Reserved)    | (Reserved)    |  |           |             |           |  |  |  |

| 0xEF | (110001100)   | (Reserved)    |  |           |             |           |  |  |  |

## 0xF0 to 0xFF

| Addr. | Registe     | r Name       | bit15 | bit14 | bit13 | bit12 | bit11 | bit10 | bit9 | bit8 |

|-------|-------------|--------------|-------|-------|-------|-------|-------|-------|------|------|

| Auur. |             | (8bitAccess) | bit7  | bit6  | bit5  | bit4  | bit3  | bit2  | bit1 | bit0 |

| 0xF0  | (Reserved)  | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xF1  | (reserved)  | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xF2  | (Reserved)  | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xF3  | (iveseived) | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xF4  | (Reserved)  | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xF5  | (Reserved)  | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xF6  | (Reserved)  | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xF7  | (iveseived) | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xF8  | (Reserved)  | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xF9  | (iveseived) | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xFA  | (Reserved)  | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xFB  | (iveseived) | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xFC  | (Reserved)  | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xFD  | (iveseived) | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xFE  | (Reserved)  | (Reserved)   |       |       |       |       |       |       |      |      |

| 0xFF  | (iveseived) | (Reserved)   |       |       |       |       |       |       |      |      |

## 2.2 Detailed Description of Each Register

## 2.2.1 Interrupt Main Block

## 2.2.1.1 0x00 Main Interrupt Status0 (MainIntStat\_0)

| Address | Register Name | Bit Symbol       | R/W  | C       | Description                       | Reset |

|---------|---------------|------------------|------|---------|-----------------------------------|-------|

| 0x00    | MainIntStat_0 | 7: DetFreezeDMA  | R(W) | 0: None | 1: DetFreezeDMA Occurred          |       |

|         |               | 6: PCIntStat     | R    | 0: None | 1: Peripheral Interrupt Occurred  |       |

|         |               | 5: HCIntStat     | R    | 0: None | 1: Host Interrupt Occurred        |       |

|         |               | 4: MainIntStat_1 | R    | 0: None | 1: Main Interrupt 1 Occurred      | 00h   |

|         |               | 3: DMACmp        | R(W) | 0: None | 1: DMA Transfer Complete          | 0011  |

|         |               | 2: PortErr       | R(W) | 0: None | 1: Port Error Occurred            |       |

|         |               | 1: Cross44V      | R(W) | 0: None | 1: Vbus Crossed 4.4V              |       |

|         |               | 0: RcvEP0Setup   | R(W) | 0: None | 1: Receive EP 0 Setup Transaction |       |

Displays an S1R72005 interrupt. You can identify an interrupt cause by referring to this register when an interrupt is issued. This register has bits both indirectly and directly indicating an interrupt cause.

A bit indirectly indicating a cause allows determination of the relevant interrupt status register to track the bit directly indicating the cause. Clearing a bit directly indicating the fundamental cause automatically clears the bit indirectly indicating this register's interrupt cause.

For a bit directly indicating an interrupt cause, you can clear the cause by setting the relevant bit to "1." If an interrupt is enabled by the MainIntEnb\_0 register, the xINT pin is asserted when an interrupt cause is set to "1," issuing an interrupt to the CPU. The xINT pin is negated if all relevant interrupt causes are cleared.

## Bit7 DetFreezeDMA

Directly indicates an interrupt cause.

This bit is set to "1" when DMA word access (16-bit access) is used, the FIFODataRemain of the channel using the DMA is set to "1," and the DMACount at that time is greater than "1" during USB reception (IN transaction during host operation or OUT transaction when peripherals are operating).

DMA transfer is halted when this bit is set to "1." However, the DMAControl register's DMAGo bit is not changed to "0."

This interrupt continues to be asserted while FIFODataRemain = 1 and DMACount > 1.

Since reading of odd-bytes is disabled when the DMACount is greater than "1" during DMA word access, if this interrupt is asserted, the data for the remaining one byte must be read from the FIFOforCPU register while the FIFOControl register's EnFIFOByteAccess bit in the relevant channel is set to "1."

This interrupt is issued during both host and peripheral operations.

This interrupt is issued, for example, when the last packet is received in an odd byte, although the DMACount remains adequate after the DMACount register has been set to an excessive size.

**EPSON**

## Bit6 PCIntStat

Indirectly indicates an interrupt cause.

This bit is set to "1" when the PCIntStat or EPIntStat register has an interrupt cause and the relevant cause is enabled. This interrupt is issued only when peripherals are operating.

## Bit5 HCIntStat

Indirectly indicates an interrupt cause.

This bit is set to "1" when the HCIntStat or PIPEIntStat register has an interrupt cause and the relevant cause is enabled. This interrupt is issued only during host operations.

#### Bit4 MainIntStat\_1

Indirectly indicates an interrupt cause.

This bit is set to "1" when the MainIntStat\_1 register has an interrupt cause and the relevant cause is enabled. This bit is used for 8-bit register access.

## Bit3 DMACmp

Directly indicates an interrupt cause.

This bit is set to "1" when DMA transfers triggered by the DMAControl\_1 register's DMAGo bit are completed up to the size specified by the DMACount\_H to L registers. This cause is also set when the DMAControl\_1 register's DMAGo bit is changed from "1" to "0" before DMA transfer is completed.

### Bit2 PortErr

Set to "1" if a port error (the USB bus does not enter into an idle state, even though a transaction is completed at the frame end: bubble) is detected during host operations. At the same time, the PIPExControl register's TranGo bit is cleared in all channels and the transaction is halted. To restart the transaction, clear this PortErr bit and set the relevant channel's TranGo bit accordingly. This interrupt is issued only during host operations.

## Bit1 Cross44V

Directly indicates an interrupt cause.

This bit is set to "1" if the V<sub>BUS</sub> voltage crosses a threshold of 4.4 V. This bit is enabled regardless of clock input conditions.

## Bit0 RcvEP0Setup

Directly indicates an interrupt cause.

This bit is set to "1" when the setup stage is completed at endpoint 0 and the received data is stored in the EP0Setup\_0 to EP0Setup\_7 registers.When this bit is set to "1," the EP0Control\_0 register's InForceSTALL and OutForceSTALL bits are automatically set to "0," and the InForceNAK and OutForceNAK bits to "1."

While the RcvEP0Setup bit is set to "1," do not change the EP0Control\_0 register's InForceNAK, OutForceNAK, InForceSTALL and OutForceSTALL bits.

This interrupt is issued only when peripherals are operating.

| Address | Register Name | Bit Symbol        | R/W  | ſ       | Description                    | Reset |

|---------|---------------|-------------------|------|---------|--------------------------------|-------|

| 0x01    | MainIntStat_1 | 7: DetReset       | R(W) | 0: None | 1: Reset Detected              |       |

|         |               | 6: DetResume      | R(W) | 0: None | 1: Resume Detected             |       |

|         |               | 5: DetNonJ        | R(W) | 0: None | 1: NonJ Interrupt Occurred     |       |

|         |               | 4: DetSuspend     | R(W) | 0: None | 1: Susupend Detected           | 00h   |

|         |               | 3: DetRmtWkup     | R(W) | 0: None | 1: RemoteWakeup Detected       | 000   |

|         |               | 2: DetSRP         | R(W) | 0: None | 1: SRP Detected                |       |

|         |               | 1: ChangeConnStat | R(W) | 0: None | 1: Connection Status Changed   |       |

|         |               | 0: ChangeID       | R(W) | 0: None | 1: ChangeID Interrupt Occurred |       |

## 2.2.1.2 0x01 Main Interrupt Status1 (MainIntStat\_1)

As with the MainIntStat\_0 register, this also displays an S1R72005 interrupt. You can identify an interrupt cause by referring to this register when an interrupt is issued. This register only has bits directly indicating an interrupt cause. You can clear an interrupt cause by setting the relevant bit to "1." If an interrupt is enabled by the MainIntEnb\_1 register, the xINT pin is asserted when an interrupt cause is set to "1," issuing an interrupt to the CPU. The xINT pin is negated if all relevant interrupt causes are cleared.

## Bit7 DetReset

Set to "1" if the USB reset state (SE0) is detected when peripherals are operating.

Reset state detection is performed only when peripherals are operating.

## Bit6 DetResume

Set to "1" if the USB resume state (K state) is detected when peripherals are operating.

Resume state detection is performed only when peripherals are operating.

## Bit5 DetNonJ

Set to "1" if a state other than J is detected on the USB bus in suspend state when peripherals are operating.

If this interrupt is issued, assess the detected signal type based on the SE0 and K states in the OTGCMonitor register's LineState bit.

This bit is enabled regardless of clock input conditions. Non-J state detection is performed only in suspend state when peripherals are operating.

## Bit4 DetSuspend

Set to "1" if the USB suspend state (J state for 3 ms) is detected when peripherals are operating.

Suspend state detection is performed only when peripherals are operating.

## Bit3 DetRmtWkup

Set to "1" if the remote wakeup state (K state) is detected on the USB bus when the OTGCCommon register's AllowRmtWkup bit is set to "1" during host operations. Remote wakeup state detection is performed only during host operations and when the remote wakeup is enabled.

## Bit2 DetSRP

Set to "1" if an SRP signal (data line pulsing: J state for 5 to 10 ms) is detected on the USB bus while device A is in idle state. SRP signal detection is performed only while device A is in idle state.

**EPSON**

## Bit1 ChangeConnStat

Set to "1" if pullup resistance connection (J state for  $2.5\mu s$ ) or disconnection (SE0 for  $2.5\mu s$ ) is detected for the connection target.

## Bit0 ChangelD

Set to "1" if mini A plug's insertion or removal is detected at the OTG receptacle.

This bit is enabled regardless of clock input conditions.

| Address | Register Name | Bit Symbol      | R/W  | 1       | Description          | Reset |

|---------|---------------|-----------------|------|---------|----------------------|-------|

| 0x02    | HCIntStat     | 7:              |      |         |                      |       |

|         |               | 6:              |      |         |                      |       |

|         |               | 5:              |      |         |                      |       |

|         |               | 4:              |      |         |                      | 00h   |

|         |               | 3:              |      |         |                      | 0011  |

|         |               | 2:              |      |         |                      |       |

|         |               | 1: FmNumberOver | R(W) | 0: None | 1: Frame Number Over |       |

|         |               | 0: SOF          | R(W) | 0: None | 1: SOF Send Complete |       |

## 2.2.1.3 0x02 Host Controller Interrupt Status (HCIntStat)

Displays an interrupt applicable to the entire host controller. This register has bits directly indicating an interrupt cause.

When this register is set to "1," you can clear an interrupt cause by writing "1" to the relevant bit.

Bit7 Reserved

- Bit6 Reserved

- Bit5 Reserved

- Bit4 Reserved

- Bit3 Reserved

- Bit2 Reserved

- Bit1 FmNumberOver

Set to "1" if the frame number counter overflows (the HCFmNumber\_H register's MSb [bit 2] is changed from "1" to "0"). An insufficient count digit in the HCFmNumber\_H or L register, if any, can be complemented by counting this interrupt.

## Bit0 SOF

Set to "1" when the host controller sends an SOF token.

| Address | Register Name | Bit Symbol      | R/W | D       | Description                 | Reset |

|---------|---------------|-----------------|-----|---------|-----------------------------|-------|

| 0x03    | PIPEIntStat   | 7:              |     |         |                             |       |

|         |               | 6:              |     |         |                             |       |

|         |               | 5:              |     |         |                             |       |

|         |               | 4: PIPEdIntStat | R   | 0: None | 1: Piped Interrupt Occurred | 0.01- |

|         |               | 3: PIPEcIntStat | R   | 0: None | 1: Pipec Interrupt Occurred | 00h   |

|         |               | 2: PIPEbIntStat | R   | 0: None | 1: Pipeb Interrupt Occurred |       |

|         |               | 1: PIPEaIntstat | R   | 0: None | 1: Pipea Interrupt Occurred |       |

|         |               | 0: PIPE0IntStat | R   | 0: None | 1: Pipe0 Interrupt Occurred |       |

## 2.2.1.4 0x03 PipeInterrupt Status (PIPEIntStat)

Indirectly indicates an interrupt applicable to host controller's pipe control (USB transfer control).

If all bits of the relevant fundamental interrupt cause register (PIPEaIntStat to PIPEeIntStat registers) are cleared, this register's relevant bit is also cleared.

## Bit7 Reserved

#### Bit6 Reserved

#### Bit5 Reserved

### Bit4 PIPEdIntStat

Set to "1" when the PIPEdIntStat register has an interrupt cause and the PIPEdIntEnb register's relevant bit is enabled.

#### Bit3 PIPEcIntStat

Set to "1" when the PIPEcIntStat register has an interrupt cause and the PIPEcIntEnb register's relevant bit is enabled.

#### Bit2 PIPEbIntStat

Set to "1" when the PIPEbIntStat register has an interrupt cause and the PIPEbIntEnb register's relevant bit is enabled.

## Bit1 PIPEaIntStat

Set to "1" when the PIPEaIntStat register has an interrupt cause and the PIPEaIntEnb register's relevant bit is enabled.

## Bit0 PIPE0IntStat

Set to "1" when the PIPE0IntStat register has an interrupt cause and the PIPE0IntEnb register's relevant bit is enabled.

| Address | Register Name | Bit Symbol | R/W  | 1       | Description          | Reset |

|---------|---------------|------------|------|---------|----------------------|-------|

| 0x04    | PCIntStat     | 7:         |      |         |                      |       |

|         |               | 6:         |      |         |                      |       |

|         |               | 5:         |      |         |                      |       |

|         |               | 4:         |      |         |                      | 00h   |

|         |               | 3:         |      |         |                      | UUN   |

|         |               | 2:         |      |         |                      |       |

|         |               | 1:         |      |         |                      |       |

|         |               | 0: RcvSOF  | R(W) | 0: None | 1: Receive SOF Token |       |

## 2.2.1.5 0x04 Peripheral Controller Interrupt Status (PCIntStat)

Displays an interrupt applicable to the entire peripheral controller. This register has bits directly indicating an interrupt cause.

When this register is set to "1," you can clear an interrupt cause by writing "1" to the relevant bit.

| Bit7 | Reserved |

|------|----------|

| Bit6 | Reserved |

| Bit5 | Reserved |

| Bit4 | Reserved |

| Bit3 | Reserved |

| Bit2 | Reserved |

| Bit1 | Reserved |

| Bit0 | RcvSOF   |

Set to "1" when an SOF token is received.

| Address | Register Name | Bit Symbol    | R/W   | D       | Description                 |       |

|---------|---------------|---------------|-------|---------|-----------------------------|-------|

| 0x05    | EPIntStat     | 7: INTranCmp  | R/(W) | 0: None | 1: IN Transaction Completed |       |

|         |               | 6:            |       |         |                             |       |

|         |               | 5: EPeIntStat | R     | 0: None | 1: EP e Interrupt Occurred  |       |