### Network Camera Controller with JPEG Encoder

#### DESCRIPTIONS

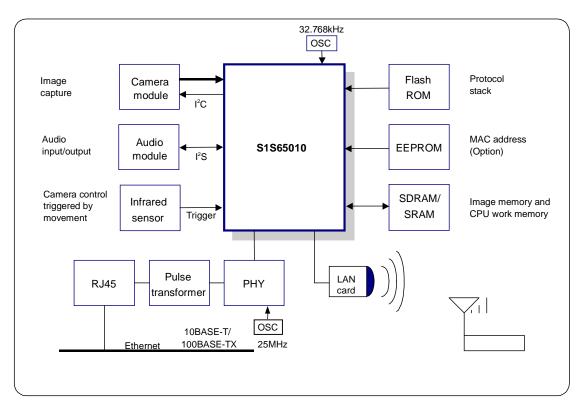

S1S65010 is an optimum network camera controller IC for configuring Internet cameras. In addition to network/protocol process function, it also has camera interface and JPEG encoder function. Connecting a Flash ROM stored with a camera module, PHY for Ethernet and firmware to the S1S65010 enables simple configuration of the Internet camera. Image capturing from cameras and JPEG encoding is executed at the receipt of shutter command from a client. When the S1S65010 is operated as an HTTP server on the LAN, it sends image files to the client upon request. Capturing images and sending them to the designated client can be done full time, or at a constant frequency using internal timer, or at a trigger on an interrupt pin using external sensors or other device. Images can be sent as an attachment to the

S1S65010, equipped with GPIO and I2C bus, can configure cameras and control external devices such as a motor via these ports through the network. A sample software is supplied with this product.

#### **■ FEATURES**

- Enables the function of the internet camera without PC

- Compatible with S1S65000 pins. Software upper compatible with S1S65000.

- Realizes 30fps@VGA frame rate as a network camera.

- Works with a variety of camera modules up to 2 mega pixels (approx. 2 million pixels).

- Supports I<sup>2</sup>S for voice/audio data.

- Compresses images in JPEG format with hardware JPEG encoder (complies with ISO 10918)

- Can configure various control settings via the network

- Can send Images via e-mail

- Can save power consumption by using wake-up mode that changes status of start, shoot and pause on a regular

- Has a Compact Flash interface for a CF memory card or a wireless LAN interface (802.11b/g).

- One-chip solution, which can reduce system cost.

- ARM720T Rev 4.3 is built-in (with 8KB cache) 50MHz

#### **■** BUILT-IN FUNCTIONS

- 32Bit RISC ARM720T (50MHz)

- 32Bit-long codes and efficient 16bit-long codes (Thumb Code) can be selected for use

- 31 general-purpose 32 bit registers

- A multiplier is included in the CPU.

78KB Embedded RAM for CPU/JPEG/Ethernet Work

#### Camera input/JPEG encoder:

- 8 bit parallel interface YUV4-2-2 input

- Resolution up to approx. 1600 × 1200 (UXGA, SXGA, XGA, VGA, QVGA, CIF, QCIF)

- Supports ITU-R BT656 format

- Hardware JPEG encoder

- Max. 30 fps @VGA, 30 fps @CIF

- Maximum pixel clock frequency for camera data input: less than 2/3 of CPU clock

- Hardware JPEG encoder

- Resize function

- **Dedicated Line Buffer**

- Variable volume FIFO for JPEG encoder output

- · An enhanced DMA

#### Network:

- Ethernet Mac controller supporting 10/100 BASE Full duplex and Half duplex mode

- Media Independent Interface (IEEE 802.3 Clause 22 compliant)

- An enhanced DMA

#### **External Memory Controller:**

- 16 bit data bus

- Supports 2 to 128 MB SDRAM

- Supports static memory (Flash EEPROM/SRAM)

- (Maximum capacity : 16MB)

3 Chip Select pins (Typically for SDRAM, Flash ROM and another chip).

#### **CF Card Interface:**

- CF+ Specification Rev.1.4 compliant.

- Usable as an interface for wireless LAN, PHS card, etc

- Supports True IDE mode

#### Standby function:

- The HALT function to stop the CPU clock when CPU operation is not required.

- Programmable I/O clock stop function for major I/O block clocks.

#### **Timer, Watchdog Timer:**

- 16-Bit timer × 3 channels

- Re-load/Cyclic or One Shot Operation Mode

- Supports toggle outputs from timer underflow or port outputs.

- Interrupt output or re-settable watchdog timer.

#### Serial Interface:

- UART: 16550 Software compatible × 1channel

- UART Lite: 16550 Software downward compatible (limited function) × 1channel

- SPI: Clock synchronous type × 1 channel

- · I2C master interface (camera Interface and

- general-purpose use)  $\ l^2S$  interface  $\times$  2 channels (audio support,  $l^2S$ standard compliant)

#### Interrupt Controller:

- Supports 32 IRQs and 2 FIQs.

- Real Time Clock:

- Supports day, hour, minute and second.

- The internal timer tap from 1/128 to 1/2 can be used as the interrupt source

Supports alarm function and interrupt.

#### **GPIO:**

General-purpose I/O port (up to 57 ports) Directions programmable for all ports.

Some ports are shared with other I/O functions.

#### **Power Supply:**

- 3.3V (I/O power supply)

- 1.8V (Core power supply)

- 1.8V (Analog power supply for PLL)

- 2.4V (Min.) 3.6V (Max.) (Camera I/O power supply)

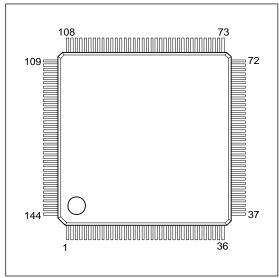

#### Package:

TQFP 144 Pin (TQFP24) 16 × 16 × 1 mm 0.4mm Pin pitch

#### **■ SUPPORTING PROTOCOLS**

ARP, ICMP, IP, TCP, UDP, HTTPd, SMTP, DHCP, FTP, DNS resolver, telnet Necessary protocols can be added or updated by rewriting Flash ROM. Addition or update by the customer is also possible. Protocols are prepared as EPSON's sample software or partner's products.

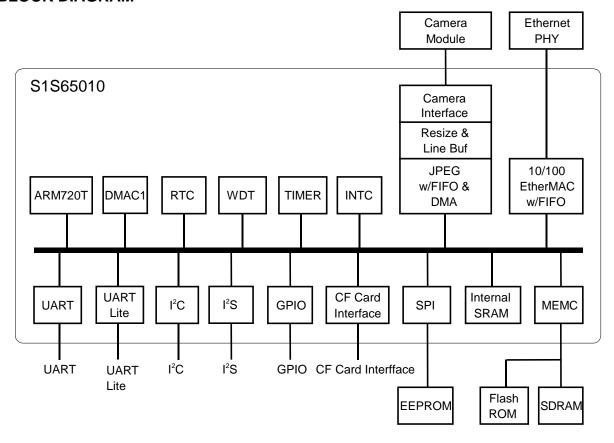

#### ■ BLOCK DIAGRAM

### **■ PIN ASSIGNMENT**

| Pin No. | Pin Name | Pin No. | Pin Name  |  |  |  |

|---------|----------|---------|-----------|--|--|--|

| 1       | MA14     | 37      | MD12      |  |  |  |

| 2       | MA15     | 38      | MD13      |  |  |  |

| 3       | MA16     | 39      | MD14      |  |  |  |

| 4       | MA17     | 40      | MD15      |  |  |  |

| 5       | MA18     | 41      | MDQML     |  |  |  |

| 6       | VSS      | 42      | MDQMH     |  |  |  |

| 7       | MA19     | 43      | HVDD1     |  |  |  |

| 8       | MCS2#    | 44      | VSS       |  |  |  |

| 9       | MCS1#    | 45      | MII_CRS   |  |  |  |

| 10      | MCS0#    | 46      | MII_COL   |  |  |  |

| 11      | LVDD     | 47      | MII_TXD3  |  |  |  |

| 12      | MOE#     | 48      | MII_TXD2  |  |  |  |

| 13      | MWE0#    | 49      | MII_TXD1  |  |  |  |

| 14      | MWE1#    | 50      | LVDD      |  |  |  |

| 15      | HVDD1    | 51      | MII_TXD0  |  |  |  |

| 16      | MCLKEN   | 52      | MII_TXEN  |  |  |  |

| 17      | MCLK     | 53      | MII_TXCLK |  |  |  |

| 18      | VSS      | 54      | MII_RXER  |  |  |  |

| 19      | MRAS#    | 55      | VSS       |  |  |  |

| 20      | MCAS#    | 56      | HVDD1     |  |  |  |

| 21      | MD0      | 57      | MII_RXCLK |  |  |  |

| 22      | MD1      | 58      | MII_RXDV  |  |  |  |

| 23      | MD2      | 59      | MII_RXD0  |  |  |  |

| 24      | MD3      | 60      | MII_RXD1  |  |  |  |

| 25      | VSS      | 61      | LVDD      |  |  |  |

| 26      | LVDD     | 62      | MII_RXD2  |  |  |  |

| 27      | MD4      | 63      | MII_RXD3  |  |  |  |

| 28      | MD5      | 64      | MII_MDC   |  |  |  |

| 29      | MD6      | 65      | MII_MDIO  |  |  |  |

| 30      | MD7      | 66      | VSS       |  |  |  |

| 31      | HVDD1    | 67      | CLKI      |  |  |  |

| 32      | MD8      | 68      | PLLVSS    |  |  |  |

| 33      | MD9      | 69      | VCP       |  |  |  |

| 34      | MD10     | 70      | PLLVDD    |  |  |  |

| 35      | MD11     | 71      | RESET#    |  |  |  |

| 36      | VSS      | 72      | TESTEN    |  |  |  |

| 73         TRST#         109         CMDATA5           74         TCK         110         CMDATA6           75         TMS         111         CMDATA7           76         TDI         112         VSS           77         TDO         113         LVDD           78         VSS         114         GPIOD0           79         GPIOA0         115         GPIOD1           80         GPIOA1         116         CFCE2#           81         GPIOA2         117         CFCE1#           82         GPIOA3         118         CFIORD#           83         GPIOA4         119         CFIOWR#           84         GPIOA5         120         CFIREQ           85         GPIOA6         121         CFRST           86         GPIOA7         122         VSS           87         HVDD1         123         HVDD1           88         VSS         124         CFWAIT#           89         GPIOB0         125         CFSTSCHG#           90         GPIOB1         126         CFDEN#           91         GPIOB2         127         CFDDIR                                                                 | Pin No. | Pin Name | Pin No. | Pin Name  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------|---------|-----------|

| 74         TCK         110         CMDATA6           75         TMS         111         CMDATA7           76         TDI         112         VSS           77         TDO         113         LVDD           78         VSS         114         GPIOD0           79         GPIOA0         115         GPIOD1           80         GPIOA1         116         CFCE2#           81         GPIOA2         117         CFCE1#           82         GPIOA3         118         CFIORD#           83         GPIOA4         119         CFIOWR#           84         GPIOA5         120         CFIREQ           85         GPIOA6         121         CFRST           86         GPIOA7         122         VSS           87         HVDD1         123         HVDD1           88         VSS         124         CFWAIT#           89         GPIOB0         125         CFSTSCHG#           90         GPIOB1         126         CFDEN#           91         GPIOB2         127         CFDDIR           92         GPIOB3         128         MA0                                                                    |         |          |         |           |

| 75         TMS         111         CMDATA7           76         TDI         112         VSS           77         TDO         113         LVDD           78         VSS         114         GPIOD0           79         GPIOA0         115         GPIOD1           80         GPIOA1         116         CFCE2#           81         GPIOA2         117         CFCE1#           82         GPIOA3         118         CFIORD#           83         GPIOA4         119         CFIOWR#           84         GPIOA5         120         CFIREQ           85         GPIOA6         121         CFRST           86         GPIOA7         122         VSS           87         HVDD1         123         HVDD1           88         VSS         124         CFWAIT#           89         GPIOB0         125         CFSTSCHG#           90         GPIOB1         126         CFDEN#           91         GPIOB2         127         CFDDIR           92         GPIOB3         128         MA0           93         LVDD         129         MA1 <t< td=""><td></td><td></td><td></td><td></td></t<>                   |         |          |         |           |

| 76         TDI         112         VSS           77         TDO         113         LVDD           78         VSS         114         GPIOD0           79         GPIOA0         115         GPIOD1           80         GPIOA1         116         CFCE2#           81         GPIOA2         117         CFCE1#           82         GPIOA3         118         CFIORD#           83         GPIOA4         119         CFIOWR#           84         GPIOA5         120         CFIREQ           85         GPIOA6         121         CFRST           86         GPIOA7         122         VSS           87         HVDD1         123         HVDD1           88         VSS         124         CFWAIT#           89         GPIOB0         125         CFSTSCHG#           90         GPIOB1         126         CFDEN#           91         GPIOB2         127         CFDDIR           92         GPIOB3         128         MA0           93         LVDD         129         MA1           94         GPIOB4         130         MA2 <td< td=""><td>75</td><td>TMS</td><td>111</td><td>CMDATA7</td></td<>   | 75      | TMS      | 111     | CMDATA7   |

| 77         TDO         113         LVDD           78         VSS         114         GPIODO           79         GPIOA0         115         GPIODD           80         GPIOA1         116         CFCE2#           81         GPIOA2         117         CFCE1#           82         GPIOA3         118         CFIORD#           83         GPIOA4         119         CFIOWR#           84         GPIOA5         120         CFIREQ           85         GPIOA6         121         CFRST           86         GPIOA7         122         VSS           87         HVDD1         123         HVDD1           88         VSS         124         CFWAIT#           89         GPIOB0         125         CFSTSCHG#           90         GPIOB1         126         CFDEN#           91         GPIOB2         127         CFDDIR           92         GPIOB3         128         MA0           93         LVDD         129         MA1           94         GPIOB4         130         MA2           95         GPIOB5         131         MA3                                                                     | 76      | TDI      | 112     |           |

| 78         VSS         114         GPIOD0           79         GPIOA0         115         GPIOD1           80         GPIOA1         116         CFCE2#           81         GPIOA2         117         CFCE1#           82         GPIOA3         118         CFIORD#           83         GPIOA4         119         CFIOWR#           84         GPIOA5         120         CFIREQ           85         GPIOA6         121         CFRST           86         GPIOA7         122         VSS           87         HVDD1         123         HVDD1           88         VSS         124         CFWAIT#           89         GPIOB0         125         CFSTSCHG#           90         GPIOB1         126         CFDEN#           91         GPIOB2         127         CFDDIR           92         GPIOB3         128         MA0           93         LVDD         129         MA1           94         GPIOB4         130         MA2           95         GPIOB5         131         MA3           96         GPIOB7         133         LVDD                                                                  | 77      | TDO      | 113     | LVDD      |

| 80         GPIOA1         116         CFCE2#           81         GPIOA2         117         CFCE1#           82         GPIOA3         118         CFIORD#           83         GPIOA4         119         CFIOWR#           84         GPIOA5         120         CFIREQ           85         GPIOA6         121         CFRST           86         GPIOA7         122         VSS           87         HVDD1         123         HVDD1           88         VSS         124         CFWAIT#           89         GPIOB0         125         CFSTSCHG#           90         GPIOB1         126         CFDEN#           91         GPIOB2         127         CFDDIR           92         GPIOB3         128         MA0           93         LVDD         129         MA1           94         GPIOB4         130         MA2           95         GPIOB5         131         MA3           96         GPIOB6         132         VSS           97         GPIOB7         133         LVDD           98         VSS         134         MA4 <td< td=""><td>78</td><td></td><td>114</td><td>GPIOD0</td></td<>       | 78      |          | 114     | GPIOD0    |

| 81         GPIOA2         117         CFCE1#           82         GPIOA3         118         CFIORD#           83         GPIOA4         119         CFIOWR#           84         GPIOA5         120         CFIREQ           85         GPIOA6         121         CFRST           86         GPIOA7         122         VSS           87         HVDD1         123         HVDD1           88         VSS         124         CFWAIT#           89         GPIOB0         125         CFSTSCHG#           90         GPIOB1         126         CFDEN#           91         GPIOB2         127         CFDDIR           92         GPIOB3         128         MA0           93         LVDD         129         MA1           94         GPIOB4         130         MA2           95         GPIOB5         131         MA3           96         GPIOB6         132         VSS           97         GPIOB7         133         LVDD           98         VSS         134         MA4           99         CMHREF         136         MA6           10                                                              | 79      | GPIOA0   | 115     | GPIOD1    |

| 82         GPIOA3         118         CFIORD#           83         GPIOA4         119         CFIOWR#           84         GPIOA5         120         CFIREQ           85         GPIOA6         121         CFRST           86         GPIOA7         122         VSS           87         HVDD1         123         HVDD1           88         VSS         124         CFWAIT#           89         GPIOB0         125         CFSTSCHG#           90         GPIOB1         126         CFDEN#           91         GPIOB2         127         CFDDIR           92         GPIOB3         128         MA0           93         LVDD         129         MA1           94         GPIOB4         130         MA2           95         GPIOB5         131         MA3           96         GPIOB6         132         VSS           97         GPIOB7         133         LVDD           98         VSS         134         MA4           99         CMHREF         135         MA5           100         CMVREF         136         MA6           101<                                                              | 80      | GPIOA1   | 116     | CFCE2#    |

| 83         GPIOA4         119         CFIOWR#           84         GPIOA5         120         CFIREQ           85         GPIOA6         121         CFRST           86         GPIOA7         122         VSS           87         HVDD1         123         HVDD1           88         VSS         124         CFWAIT#           89         GPIOB0         125         CFSTSCHG#           90         GPIOB1         126         CFDEN#           91         GPIOB2         127         CFDDIR           92         GPIOB3         128         MA0           93         LVDD         129         MA1           94         GPIOB4         130         MA2           95         GPIOB5         131         MA3           96         GPIOB6         132         VSS           97         GPIOB7         133         LVDD           98         VSS         134         MA4           99         CMHREF         135         MA5           100         CMVREF         136         MA6           101         CMCLKOUT         138         MA8           103 </td <td>81</td> <td>GPIOA2</td> <td>117</td> <td>CFCE1#</td>  | 81      | GPIOA2   | 117     | CFCE1#    |

| 84         GPIOA5         120         CFIREQ           85         GPIOA6         121         CFRST           86         GPIOA7         122         VSS           87         HVDD1         123         HVDD1           88         VSS         124         CFWAIT#           89         GPIOB0         125         CFSTSCHG#           90         GPIOB1         126         CFDEN#           91         GPIOB2         127         CFDDIR           92         GPIOB3         128         MA0           93         LVDD         129         MA1           94         GPIOB4         130         MA2           95         GPIOB5         131         MA3           96         GPIOB6         132         VSS           97         GPIOB7         133         LVDD           98         VSS         134         MA4           99         CMHREF         135         MA5           100         CMVREF         136         MA6           101         CMCLKOUT         138         MA8           103         CMDATA0         139         HVDD1           104 </td <td>82</td> <td>GPIOA3</td> <td>118</td> <td>CFIORD#</td> | 82      | GPIOA3   | 118     | CFIORD#   |

| 85         GPIOA6         121         CFRST           86         GPIOA7         122         VSS           87         HVDD1         123         HVDD1           88         VSS         124         CFWAIT#           89         GPIOB0         125         CFSTSCHG#           90         GPIOB1         126         CFDEN#           91         GPIOB2         127         CFDDIR           92         GPIOB3         128         MA0           93         LVDD         129         MA1           94         GPIOB4         130         MA2           95         GPIOB5         131         MA3           96         GPIOB6         132         VSS           97         GPIOB7         133         LVDD           98         VSS         134         MA4           99         CMHREF         135         MA5           100         CMVREF         136         MA6           101         CMCLKOUT         138         MA8           103         CMDATA0         139         HVDD1           104         CMDATA1         140         MA9           105 <td>83</td> <td>GPIOA4</td> <td>119</td> <td>CFIOWR#</td>       | 83      | GPIOA4   | 119     | CFIOWR#   |

| 86         GPIOA7         122         VSS           87         HVDD1         123         HVDD1           88         VSS         124         CFWAIT#           89         GPIOB0         125         CFSTSCHG#           90         GPIOB1         126         CFDEN#           91         GPIOB2         127         CFDDIR           92         GPIOB3         128         MA0           93         LVDD         129         MA1           94         GPIOB4         130         MA2           95         GPIOB5         131         MA3           96         GPIOB6         132         VSS           97         GPIOB7         133         LVDD           98         VSS         134         MA4           99         CMHREF         135         MA5           100         CMVREF         136         MA6           101         CMCLKOUT         138         MA8           103         CMDATA0         139         HVDD1           104         CMDATA1         140         MA9           105         HVDD2         141         MA10                                                                                | 84      | GPIOA5   | 120     | CFIREQ    |

| 87         HVDD1         123         HVDD1           88         VSS         124         CFWAIT#           89         GPIOB0         125         CFSTSCHG#           90         GPIOB1         126         CFDEN#           91         GPIOB2         127         CFDDIR           92         GPIOB3         128         MA0           93         LVDD         129         MA1           94         GPIOB4         130         MA2           95         GPIOB5         131         MA3           96         GPIOB6         132         VSS           97         GPIOB7         133         LVDD           98         VSS         134         MA4           99         CMHREF         135         MA5           100         CMVREF         136         MA6           101         CMCLKIN         137         MA7           102         CMCLKOUT         138         MA8           103         CMDATA0         139         HVDD1           104         CMDATA1         140         MA9           105         HVDD2         141         MA10                                                                              | 85      | GPIOA6   | 121     | CFRST     |

| 88         VSS         124         CFWAIT#           89         GPIOB0         125         CFSTSCHG#           90         GPIOB1         126         CFDEN#           91         GPIOB2         127         CFDDIR           92         GPIOB3         128         MA0           93         LVDD         129         MA1           94         GPIOB4         130         MA2           95         GPIOB5         131         MA3           96         GPIOB6         132         VSS           97         GPIOB7         133         LVDD           98         VSS         134         MA4           99         CMHREF         135         MA5           100         CMVREF         136         MA6           101         CMCLKIN         137         MA7           102         CMCLKOUT         138         MA8           103         CMDATA0         139         HVDD1           104         CMDATA1         140         MA9           105         HVDD2         141         MA10                                                                                                                                   | 86      | GPIOA7   | 122     | VSS       |

| 89         GPIOB0         125         CFSTSCHG#           90         GPIOB1         126         CFDEN#           91         GPIOB2         127         CFDDIR           92         GPIOB3         128         MA0           93         LVDD         129         MA1           94         GPIOB4         130         MA2           95         GPIOB5         131         MA3           96         GPIOB6         132         VSS           97         GPIOB7         133         LVDD           98         VSS         134         MA4           99         CMHREF         135         MA5           100         CMVREF         136         MA6           101         CMCLKIN         137         MA7           102         CMCLKOUT         138         MA8           103         CMDATA0         139         HVDD1           104         CMDATA1         140         MA9           105         HVDD2         141         MA10                                                                                                                                                                                        | 87      | HVDD1    | 123     | HVDD1     |

| 90         GPIOB1         126         CFDEN#           91         GPIOB2         127         CFDDIR           92         GPIOB3         128         MA0           93         LVDD         129         MA1           94         GPIOB4         130         MA2           95         GPIOB5         131         MA3           96         GPIOB6         132         VSS           97         GPIOB7         133         LVDD           98         VSS         134         MA4           99         CMHREF         135         MA5           100         CMVREF         136         MA6           101         CMCLKIN         137         MA7           102         CMCLKOUT         138         MA8           103         CMDATA0         139         HVDD1           104         CMDATA1         140         MA9           105         HVDD2         141         MA10                                                                                                                                                                                                                                                  | 88      | VSS      | 124     | CFWAIT#   |

| 91         GPIOB2         127         CFDDIR           92         GPIOB3         128         MA0           93         LVDD         129         MA1           94         GPIOB4         130         MA2           95         GPIOB5         131         MA3           96         GPIOB6         132         VSS           97         GPIOB7         133         LVDD           98         VSS         134         MA4           99         CMHREF         135         MA5           100         CMVREF         136         MA6           101         CMCLKIN         137         MA7           102         CMCLKOUT         138         MA8           103         CMDATA0         139         HVDD1           104         CMDATA1         140         MA9           105         HVDD2         141         MA10                                                                                                                                                                                                                                                                                                         | 89      | GPIOB0   | 125     | CFSTSCHG# |

| 92         GPIOB3         128         MA0           93         LVDD         129         MA1           94         GPIOB4         130         MA2           95         GPIOB5         131         MA3           96         GPIOB6         132         VSS           97         GPIOB7         133         LVDD           98         VSS         134         MA4           99         CMHREF         135         MA5           100         CMVREF         136         MA6           101         CMCLKIN         137         MA7           102         CMCLKOUT         138         MA8           103         CMDATA0         139         HVDD1           104         CMDATA1         140         MA9           105         HVDD2         141         MA10                                                                                                                                                                                                                                                                                                                                                                | 90      |          | 126     | CFDEN#    |

| 93         LVDD         129         MA1           94         GPIOB4         130         MA2           95         GPIOB5         131         MA3           96         GPIOB6         132         VSS           97         GPIOB7         133         LVDD           98         VSS         134         MA4           99         CMHREF         135         MA5           100         CMVREF         136         MA6           101         CMCLKIN         137         MA7           102         CMCLKOUT         138         MA8           103         CMDATA0         139         HVDD1           104         CMDATA1         140         MA9           105         HVDD2         141         MA10                                                                                                                                                                                                                                                                                                                                                                                                                    | 91      |          | 127     | CFDDIR    |

| 94         GPIOB4         130         MA2           95         GPIOB5         131         MA3           96         GPIOB6         132         VSS           97         GPIOB7         133         LVDD           98         VSS         134         MA4           99         CMHREF         135         MA5           100         CMVREF         136         MA6           101         CMCLKIN         137         MA7           102         CMCLKOUT         138         MA8           103         CMDATA0         139         HVDD1           104         CMDATA1         140         MA9           105         HVDD2         141         MA10                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 92      | GPIOB3   | 128     | MA0       |

| 95 GPIOB5 131 MA3 96 GPIOB6 132 VSS 97 GPIOB7 133 LVDD 98 VSS 134 MA4 99 CMHREF 135 MA5 100 CMVREF 136 MA6 101 CMCLKIN 137 MA7 102 CMCLKOUT 138 MA8 103 CMDATA0 139 HVDD1 104 CMDATA1 140 MA9 105 HVDD2 141 MA10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 93      | LVDD     | 129     | MA1       |

| 96         GPIOB6         132         VSS           97         GPIOB7         133         LVDD           98         VSS         134         MA4           99         CMHREF         135         MA5           100         CMVREF         136         MA6           101         CMCLKIN         137         MA7           102         CMCLKOUT         138         MA8           103         CMDATA0         139         HVDD1           104         CMDATA1         140         MA9           105         HVDD2         141         MA10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 94      | GPIOB4   | 130     | MA2       |

| 97         GPIOB7         133         LVDD           98         VSS         134         MA4           99         CMHREF         135         MA5           100         CMVREF         136         MA6           101         CMCLKIN         137         MA7           102         CMCLKOUT         138         MA8           103         CMDATA0         139         HVDD1           104         CMDATA1         140         MA9           105         HVDD2         141         MA10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 95      | GPIOB5   |         | _         |

| 98         VSS         134         MA4           99         CMHREF         135         MA5           100         CMVREF         136         MA6           101         CMCLKIN         137         MA7           102         CMCLKOUT         138         MA8           103         CMDATA0         139         HVDD1           104         CMDATA1         140         MA9           105         HVDD2         141         MA10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 96      | GPIOB6   |         | VSS       |

| 99 CMHREF 135 MA5 100 CMVREF 136 MA6 101 CMCLKIN 137 MA7 102 CMCLKOUT 138 MA8 103 CMDATA0 139 HVDD1 104 CMDATA1 140 MA9 105 HVDD2 141 MA10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 97      | GPIOB7   | 133     | LVDD      |

| 100         CMVREF         136         MA6           101         CMCLKIN         137         MA7           102         CMCLKOUT         138         MA8           103         CMDATA0         139         HVDD1           104         CMDATA1         140         MA9           105         HVDD2         141         MA10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |          | 134     | MA4       |

| 101         CMCLKIN         137         MA7           102         CMCLKOUT         138         MA8           103         CMDATA0         139         HVDD1           104         CMDATA1         140         MA9           105         HVDD2         141         MA10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |          |         | _         |

| 102         CMCLKOUT         138         MA8           103         CMDATA0         139         HVDD1           104         CMDATA1         140         MA9           105         HVDD2         141         MA10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 100     | •        | 136     | MA6       |

| 103         CMDATA0         139         HVDD1           104         CMDATA1         140         MA9           105         HVDD2         141         MA10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 101     | CMCLKIN  | 137     | MA7       |

| 104         CMDATA1         140         MA9           105         HVDD2         141         MA10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 102     | CMCLKOUT | 138     | MA8       |

| 105 HVDD2 141 MA10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         | •        | 139     |           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         | _        | 140     | _         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |          |         |           |

| 106 CMDATA2 142 MA11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |          |         |           |

| 107 CMDATA3 143 MA12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |          |         |           |

| 108 CMDATA4 144 MA13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 108     | CMDATA4  | 144     | MA13      |

Note: # at the right end of a pin name indicates an Low active signal.

#### **■ PIN DESCRIPTION**

#: # at the right end of a pin name indicates an active low signal.

I: Input pin

O: Output pin

IO: Bi-directional pin

P: Power Supply

**Cell Type Description**

| Cell Type | Description                                                                   | Applicable pin example        |

|-----------|-------------------------------------------------------------------------------|-------------------------------|

| ICS       | LVCMOS Schmitt input                                                          | TCK, CLKI, RESET#             |

| ICD1      | LVCMOS input with pull down resistor (50kΩ @3.3V)                             | TESTEN                        |

| ICU1      | LVCMOS input with pull up resistor (50kΩ@3.3V)                                | TMS, TDI                      |

| ICSU1     | LVCMOS Schmitt input with pull up resistor                                    | TRST#                         |

| BLNC4     | Low noise LVCMOS IO buffer (±4mA)                                             | MII                           |

| BLNC4U1   | Low noise LVCMOS IO buffer with pull-up resistor (50kΩ@3.3V) (±4mA)           | CF Interface                  |

| BLNC4D2   | Low noise LVCMOS IO buffer with pull-down resistor (100kΩ@3.3V) (±4mA)        | MD [15:0]                     |

| BLNS4     | Low noise LVCMOS Schmitt IO buffer (±4mA)                                     | GPIOA, GPIOB, GPIOD [1:0]     |

| BLNS4D1   | Low noise LVCMOS Schmitt IO buffer with pull-down resistor (50kΩ@3.0V) (±4mA) | Camera Interface              |

| OLN4      | Low noise output buffer (±4mA)                                                | MEMC Interface (excluding MD) |

| OTLN4     | Low noise Tri-state output buffer (±4mA)                                      | TDO                           |

| OLTR      | Low Voltage Transparent Output                                                | VCP                           |

#### **Pin Description**

| Pin Name     | Туре  | Cell<br>Type | Pin No.                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|--------------|-------|--------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| (MA [23:22]) | (I/O) | (BLNS4)      | (97, 96)                            | See GPIOB[7:6] for more detail of these pins                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| (MA [21:20]) | (I/O) | (BLNS4)      | (114-115)                           | See GPIOD[1:0] for more detail of these pins                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| MA [19:12]   | 0     | OLN4         | 7, 1-5,<br>143-144                  | Address outputs [19:12] Out of these, MA[15:14] become BA[1:0] as a bank address, when using SDRAM.                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| MA 11        | 0     | OLN4         | 142                                 | This pin has the following functions:  • MA11: Address output 11 (Default pin function)  • CFREG# output  During the CompactFlash (CF) cycles, this signal behaves as REG# signal selecting attribute or I/O space of the CF card.                                                                                                                                                                                                                                               |  |  |  |

| MA [10:0]    | 0     | OLN4         | 128-131,<br>134-138,<br>140-141     | These pins have the following functions:  • MA[10:0]: Address outputs [10:0] (Default pin function)  • CFADDR[10:0] outputs  During the CF cycles, these signals become the CF interface address signals [10:0].                                                                                                                                                                                                                                                                 |  |  |  |

| MD [15:0]    | I/O   | BLNC4D2      | 21-24,<br>27-30,<br>32-35,<br>37-40 | These pins have the following functions: • 16-bit Data bus for memory (Default pin function) • During the CF cycles, these pins become 16 bit data. • MODESEL[15:0]  At the power ON reset (RESET# is changed from LOW to HIGH), these pins are sampled to determine the internal operation mode. See "SYSTEM CONFIGURATION by MODESEL PIN" for more details. To determine the operation mode, a pull-up resistor may be required externally. (Resistor value:4.7k - 10kΩ range) |  |  |  |

| MCS [2:0]#   | 0     | OLN4         | 8-10                                | Chip select signals for memory (SDRAM and static memories) (Low active) MCS2# is for SDRAM                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| MOE#         | 0     | OLN4         | 12                                  | This pin has the following functions:(Low active)  • MOE#: Read strobe signal for memory read cycle (Default pin function)  • CFOE# output  During the CF cycle, this signal becomes output enable signal for CF common memory or attribute space access.                                                                                                                                                                                                                        |  |  |  |

| Pin Name       | Туре | Cell<br>Type | Pin No.         | Description                                                                                                                                                                                                                                                         |  |  |  |

|----------------|------|--------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MWE0#          | 0    | OLN4         | 13              | This pin has the following functions:(Low active)  • MWE0#: Write Enable signal for memory (for static memory) (Default pin function)  • CFWE# output  During the CF cycle, this signal becomes write enable signal for CF common memory or attribute space access. |  |  |  |

| MWE1#          | 0    | OLN4         | 14              | Write Enable signal for memory (for SDRAM) (Low active)                                                                                                                                                                                                             |  |  |  |

| MCLK           | 0    | OLN4         | 17              | Clock output signal for SDRAM  Outputs the same frequency as the Internal Operating Frequency (CPUCLK).                                                                                                                                                             |  |  |  |

| MCLKEN         | 0    | OLN4         | 16              | Clock enable signal for SDRAM                                                                                                                                                                                                                                       |  |  |  |

| MRAS#          | 0    | OLN4         | 19              | RAS signal for SDRAM (Low active)                                                                                                                                                                                                                                   |  |  |  |

| MCAS#          | 0    | OLN4         | 20              | CAS signal for SDRAM (Low active)                                                                                                                                                                                                                                   |  |  |  |

| MDQML<br>MDQMH | 0    | OLN4         | 41-42           | These pins have the following functions:  • Byte enable signal (for static memory)  • DQM signal for SDRAM  MDQML and MDQMH correspond to lower byte and higher byte respectively.                                                                                  |  |  |  |

| MII_TXCLK      | I/O  | BLNC4        | 53              | This pin has the following functions:  • MILTXCLK: Clock TXCLK input for sending data from Media Independent Interface Ethernet PHY (hereafter referred to as MII PHY) (Default pin function; Select "Function 1")  • GPIOF7 input/output                           |  |  |  |

| MII_TXEN       | I/O  | BLNC4        | 52              | This pin has the following functions:  • MII_TXEN: Send output enable TXEN output to MII PHY (Default pin function; Select "Function 1")  • GPIOF6 input/output                                                                                                     |  |  |  |

| MII_TXD3       | I/O  | BLNC4        | 47              | This pin has the following functions:  • MII_TXD3: Send data TXD3 output to MII PHY (Default pin function; Select "Function 1")  • GPIOF2 input/output                                                                                                              |  |  |  |

| MII_TXD2       | I/O  | BLNC4        | 48              | This pin has the following functions:  • MII_TXD2: Send data TXD2 output to MII PHY  (Default pin function; Select "Function 1")  • GPIOF3 input/output                                                                                                             |  |  |  |

| MII_TXD1       | I/O  | BLNC4        | 49              | This pin has the following functions:  • MII_TXD1: Send data TXD1 output to MII PHY  (Default pin function; Select "Function 1")  • GPIOF4 input/output                                                                                                             |  |  |  |

| MII_TXD0       | I/O  | BLNC4        | 51              | This pin has the following functions:  • MII_TXD0: Send data TXD0 output to MII PHY  (Default pin function; Select "Function 1")  • GPIOF5 input/output                                                                                                             |  |  |  |

| MII_RXCLK      | I/O  | BLNC4        | 57              | This pin has the following functions:  • MII_RXCLK: Receive data clock RXCLK input from MII PHY (Default pin function; Select "Function 1")  • GPIOG1 input/output                                                                                                  |  |  |  |

| MII_COL        | I/O  | BLNC4        | 46              | This pin has the following functions:  • MII_COL: Collision COL detection input from MII PHY (Default pin function; Select "Function 1")  • GPIOF1 input/output                                                                                                     |  |  |  |

| MII_CRS        | I/O  | BLNC4        | 45              | This pin has the following functions:  • MII_CRS: Carrier sense CRS input from MII PHY  (Default pin function; Select "Function 1")  • GPIOF0 input/output                                                                                                          |  |  |  |

| MII_RXDV       | I/O  | BLNC4        | 58              | This pin has the following functions:  • MII_RXDV: Receive data valid RXDV input from MII PHY (Default pin function; Select "Function 1")  • GPIOG2 input/output                                                                                                    |  |  |  |

| MII_RXD[3:0]   | I/O  | BLNC4        | 59-60,<br>62-63 | These pins have the following functions:  • MII_RXD[3:0]: Receive data RXD [3:0] input from MII PHY (Default pin function; Select "Function 1")  • GPIOG[6:3] input/output                                                                                          |  |  |  |

| Pin Name    | Туре | Cell<br>Type | Pin No.             | Description                                                                                                                                                                                                                                                                                                                                       |

|-------------|------|--------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MII_RXER    | I/O  | BLNC4        | 54                  | This pin has the following functions:  • MII_RXER: Receive error RXER for MII PHY (Default pin function; Select "Function 1")  • GPIOG0 input/output                                                                                                                                                                                              |

| MII_MDC     | I/O  | BLNC4        | 64                  | This pin has the following functions:  • MII_MDC: Management interface clock MDC output for MII PHY (Default pin function; Select "Function 1")  • GPIOG7 input/output                                                                                                                                                                            |

| MII_MDIO    | I/O  | BLNC4        | 65                  | This pin has the following functions:  • MII_MDIO: Management interface data MDIO input/output for MII PHY (Default pin function; Select "Function 1")  • GPIOH0 input/output                                                                                                                                                                     |

| CMDATA[7:0] | I/O  | BLNS4D1      | 103-104,<br>106-111 | These pins have the following functions:  • CMDATA[7:0]: YUV data from camera  After reset, theses pins become GPIOC[7:0] input. To use as the CMDATA[7:0] pin, select "Function 1" in the Bit[15:0] of the GPIOC pin function register.  • GPIOC[7:0] input/output (Default pin function)                                                        |

| CMVREF      | I/O  | BLNS4D1      | 100                 | This pin has the following functions:  • CMVREF: Vertical sync input from camera  After reset, this pin becomes GPIOD4 input. To use as the CMVREF pin, select "Function 1" in the Bit[9:8] of the GPIOD pin function register.  • GPIOD4 input/output (Default pin function)                                                                     |

| CMHREF      | I/O  | BLNS4D1      | 99                  | This pin has the following functions:  • CMHREF: Horizontal sync input from camera  After reset, this pin becomes GPIOD5 input. To use as the CMHREF pin, select "Function 1" in the Bit [11:10] of the GPIOD pin function register.  • GPIOD5 input/output (Default pin function)                                                                |

| CMCLKOUT    | I/O  | BLNS4D1      | 102                 | This pin has the following functions:  • CMCLKOUT: Basic clock output to camera  After reset, this pin becomes GPIOD6 input. To use as the CMCLKOUT pin, select "Function 1" in the Bit [13:12] of the GPIOD pin function register.  • GPIOD6 input/output (Default pin function)                                                                 |

| CMCLKIN     | I/O  | BLNS4D1      | 101                 | This pin has the following functions:  • CMCLKIN: Pixel clock input from camera  After reset, this pin becomes GPIOD7 input. To use as the CMCLKIN pin, select "Function 1" in the Bit [15:14] of the GPIOD pin function register.  • GPIOD7 input/output (Default pin function)                                                                  |

| CFCE2#      | I/O  | BLNC4U1      | 116                 | This pin has the following functions:  • CFCE2#: Card Enable 2 CE2# for CompactFlash card Interface (hereafter referred to as CF) (Low active)  After reset, this pin becomes GPIOD2 input. To use as the CFCE2# pin, select "Function 1" in the Bit [5:4] of the GPIOD pin function register.  • GPIOD2 input/output (Default pin function)      |

| CFCE1#      | I/O  | BLNC4U1      | 117                 | This pin has the following functions:  • CFCE1#: Card Enable 1 CE1# for CF (Low active)  After reset, this pin becomes GPIOD3 input. To use as the CFCE1# pin, select "Function 1" in the Bit [7:6] of the GPIOD pin function register.  • GPIOD3 input/output (Default pin function)                                                             |

| CFIORD#     | I/O  | BLNC4U1      | 118                 | This pin has the following functions:  • CFIORD#: IO Read strobe signal for CF (Low active)  After reset, this pin becomes GPIOE0 input. To use as the CFIORD# pin, select "Function 1" in the Bit [1:0] of the GPIOE pin function register.  • GPIOE0 input/output (Default pin function)  • I2S0_SD: Serial Data for I2S0 (Select "Function 2") |

| Pin Name  | Туре | Cell<br>Type | Pin No. | Description                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------|------|--------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CFIOWR#   | I/O  | BLNC4U1      | 119     | This pin has the following functions:  • CFIOWR#: IO Write strobe signal for CF (Low active)  After reset, this pin becomes GPIOE1 input. To use as the CFIOWR# pin, select "Function 1" in the Bit [3:2] of the GPIOE pin function register.  • GPIOE1 input/output (Default pin function) • I2S0_SCK: Serial clock for I2S0 (Select "Function 2")                                                                     |

| CFWAIT#   | I/O  | BLNC4U1      | 124     | This pin has the following functions:  • CFWAIT#: Wait request input from CF (Low active)  After reset, this pin becomes GPIOE2 input. To use as the CFWAIT# pin, select "Function 1" in the Bit [5:4] of the GPIOE pin function register.  • MWAIT#: Wait signal for Memory controller (Low active) Uses the same pin with CFWAIT# signal (Select "Function 1") • GPIOE2 input/output (Default pin function)           |

| CFRST     | I/O  | BLNC4U1      | 121     | This pin has the following functions:  • CFRST: Reset signal to CF card  The signal is HIGH when the card is reset and LOW when the card is under normal operation.  After reset, this pin becomes GPIOE3 input. To use as the CFRST pin, select "Function 1" in the Bit [7:6] of the GPIOE pin function register.  • GPIOE3 input/output (Default pin function)  • 12S0_WS: Word select for I2SO (Select "Function 2") |

| CFIREQ    | I/O  | BLNC4U1      | 120     | This pin has the following functions:  • CFIREQ: Interrupt request signal from CF card  After reset, this pin becomes GPIOE4 input. To use as the CFIREQ pin, select "Function 1" in the Bit [9:8] of the GPIOE pin function register.  • GPIOE4 input/output (Default pin function)                                                                                                                                    |

| CFSTSCHG# | I/O  | BLNC4U1      | 125     | This pin has the following functions:  • CFSTSCHG#: Status change signal from CF card (Low active)  After reset, this pin becomes GPIOE5 input. To use as the CFSTSCHG# pin, select "Function 1" in the Bit [11:10] of the GPIOE pin function register.  • GPIOE5 input/output (Default pin function)  • I2S1_SD: Serial Data for I2S1 (Select "Function 2")                                                            |

| CFDEN#    | I/O  | BLNC4U1      | 126     | This pin has the following functions:  • CFDEN#: CF Data Bus enable signal of CF card for external buffer (Low active)  After reset, this pin becomes GPIOE6 input. To use as the CFDEN# pin, select "Function 1" in the Bit [13:12] of the GPIOE pin function register.  • GPIOE6 input/output (Default pin function)  • I2S1_SCK: Serial clock for I2S1 (Select "Function 2")                                         |

| CFDDIR    | I/O  | BLNC4U1      | 127     | This pin has the following functions:  • CFDDIR: Data Bus Direction signal for CF When CF data is read, this pin becomes low. After reset, this pin becomes GPIOE7 input. To use as the CFDDIR pin, select "Function 1" in the Bit [15:14] of the GPIOE pin function register.  • GPIOE7 input/output (Default pin function) • I2S1_WS: Word select for I2S1 (Select "Function 2")                                      |

| GPIOA0    | I/O  | BLNS4        | 79      | This pin has the following functions:  • GPIOA0 input/output (Default pin function)  • TXD0: UART Send data output (Select "Function 1")                                                                                                                                                                                                                                                                                |

| GPIOA1    | I/O  | BLNS4        | 80      | This pin has the following functions:  • GPIOA1 input/output (Default pin function)  • RXD0: UART Receive data input (Select "Function 1")                                                                                                                                                                                                                                                                              |

| GPIOA2    | I/O  | BLNS4        | 81      | This pin has the following functions:  • GPIOA2 input/output (Default pin function)  • SPI_SS: Chip select for SPI (Select "Function 1")  • TXD1: UART Lite Send data output (Select "Function 2")                                                                                                                                                                                                                      |

| Pin Name | Туре | Cell<br>Type | Pin No. | Description                                                                                                                                                                                                             |

|----------|------|--------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOA3   | I/O  | BLNS4        | 82      | This pin has the following functions:  • GPIOA3 input/output (Default pin function)  • SPI_SCLK: Serial clock for SPI (Select "Function 1")  • RXD1: UART Lite Receive data input (Select "Function 2")                 |

| GPIOA4   | I/O  | BLNS4        | 83      | This pin has the following functions:  • GPIOA4 input/output (Default pin function)  • SPI_MISO: Master In/Slave Out for SPI (Select "Function 1")                                                                      |

| GPIOA5   | I/O  | BLNS4        | 84      | This pin has the following functions:  • GPIOA5 input/output (Default pin function)  • SPI_MOSI: Master Out/Slave In for SPI (Select "Function 1")                                                                      |

| GPIOA6   | I/O  | BLNS4        | 85      | This pin has the following functions:  • GPIOA6 input/output (Default pin function)  • SCL: Clock for I <sup>2</sup> C input/output (Select "Function 1")                                                               |

| GPIOA7   | I/O  | BLNS4        | 86      | This pin has the following functions:  • GPIOA7 input/output (Default pin function)  • SDA: Data for I <sup>2</sup> C input/output (Select "Function 1")                                                                |

| GPIOB0   | I/O  | BLNS4        | 89      | This pin has the following functions:  • GPIOB0 input/output (Default pin function)  • IINT0 input  • I2S0_WS: Word select for I2S0 (Select "Function 2")                                                               |

| GPIOB1   | I/O  | BLNS4        | 90      | This pin has the following functions:     GPIOB1 input/output (Default pin function)     INT1 input     RTS0#: UART Send request output (Select "Function 1")     I2S0_SCK: Serial clock for I2S0 (Select "Function 2") |

| GPIOB2   | I/O  | BLNS4        | 91      | This pin has the following functions:     GPIOB2 input/output (Default pin function)     INT2 input     CTS0#: UART Sendable input (Select "Function 1")     I2S0_SD: Serial Data for I2S0 (Select "Function 2")        |

| GPIOB3   | I/O  | BLNS4        | 92      | This pin has the following functions:  • GPIOB3 input/output (Default pin function)  • INT3 input  • Timer0 output (Select "Function 1")  • I2S1_SD: Serial Data for I2S1 (Select "Function 2")                         |

| GPIOB4   | I/O  | BLNS4        | 94      | This pin has the following functions:     GPIOB4 input/output (Default pin function)     INT4 input     Timer1 output (Select "Function 1")                                                                             |

| GPIOB5   | I/O  | BLNS4        | 95      | This pin has the following functions:  • GPIOB5 input/output (Default pin function)  • INT5 input  • Timer2 output (Select "Function 1")                                                                                |

| GPIOB6   | I/O  | BLNS4        | 96      | This pin has the following functions:     GPIOB6 input/output (Default pin function)     INT6 input     MA22: Address output pin 22 (Select "Function 1")     I2S1_SCK: Serial clock for I2S1 (Select "Function 2")     |

| GPIOB7   | I/O  | BLNS4        | 97      | This pin has the following functions:                                                                                                                                                                                   |