# S1S65010 Technical Manual

### NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of Economy, Trade and Industry or other approval from another government agency.

**ARM** is a registered trademark of ARM.

CompactFlash is a registered trademark of Sandisk.

All other product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

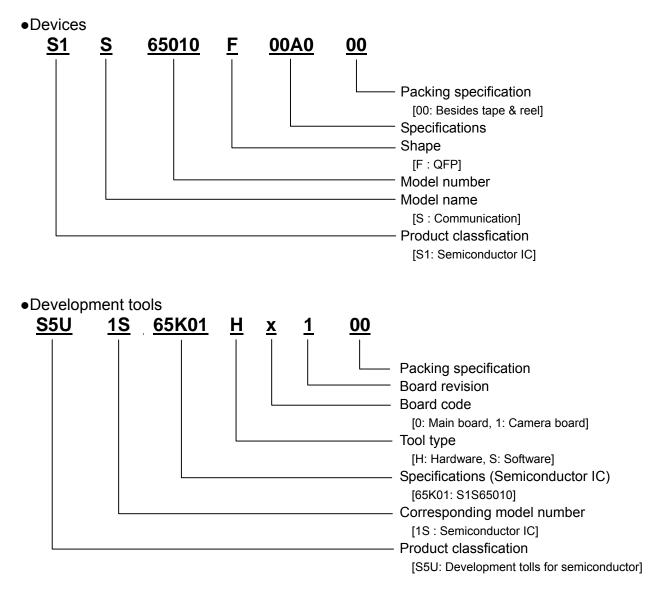

# Configuration of product number

# **Notes on Register Descriptions**

Keep the following in mind when reading the register descriptions in this document.

Register descriptions in this document use the following abbreviations.

| R/W | : | Read/write                                                                                                        |

|-----|---|-------------------------------------------------------------------------------------------------------------------|

| RO  | : | Read only                                                                                                         |

| WO  | : | Write only                                                                                                        |

| RSV | : | Reserved bit or register field<br>In the absence of any indication to the contrary, always write 0 to these bits. |

| n/a | : | Not available<br>In the absence of any indication to the contrary, always write 0 to these bits.                  |

In the absence of any indication to the contrary, always write 0 reserved bits. Writing 1 to a reserved bit can have unintended consequences.

Bits labeled "n/a" have no effect on hardware operation.

Some registers are accessible only under specific conditions. Read/write access is otherwise not allowed.

# **Table of Contents**

| 1. OVERVIEW                                                 | 1  |

|-------------------------------------------------------------|----|

| 1.1 Features                                                | 1  |

| 1.2 Internal Functional Blocks                              | 1  |

| 1.3 Supported Protocols                                     | 3  |

| 2. BLOCK DIAGRAM                                            | 4  |

| 3. PINS                                                     | 5  |

| 3.1 Pin Descriptions                                        | 6  |

| 3.2 Multiplexed Function of GPIO Pins                       | 14 |

| 3.3 Pin Configurations During and After a Reset             | 15 |

| 4. FUNCTIONAL DESCRIPTION                                   | 16 |

| 4.1 System Configuration                                    |    |

| 4.2 Memory Maps                                             |    |

| 4.2.1 AHB1 Memory Map                                       |    |

| 4.2.2 AHB2 Memory Map                                       |    |

| 4.3 I/O Map                                                 |    |

| 4.4 Interrupt Controller                                    |    |

| 4.5 Internal Functional Blocks                              |    |

| 5. CPU                                                      |    |

| 5.1 Overview                                                |    |

| 5.2 Block Diagram                                           | 22 |

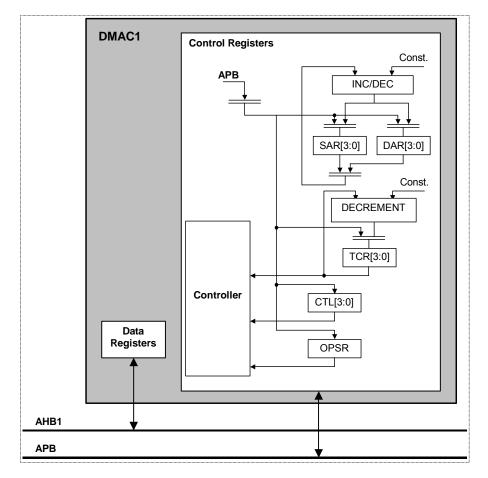

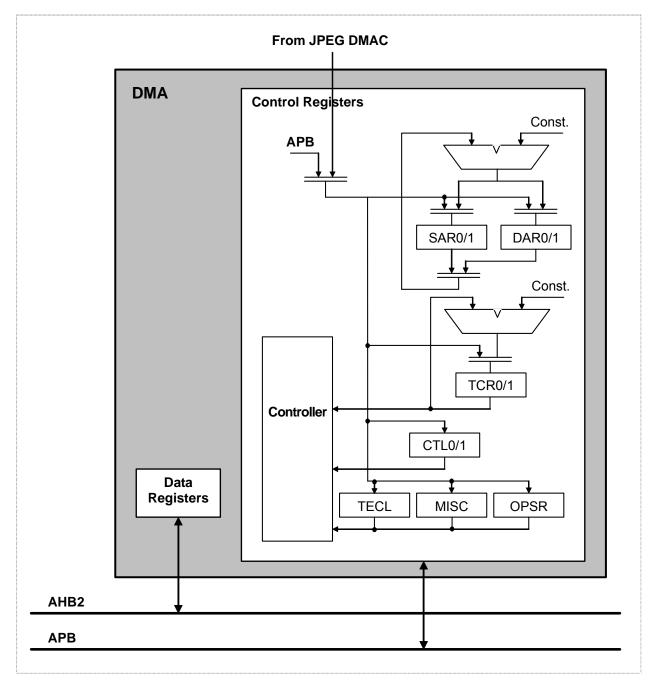

| 6. DMA CONTROLLER 1 (DMAC1)                                 | 23 |

| 6.1 Overview                                                | 23 |

| 6.2 Block Diagram                                           | 23 |

| 6.3 External Pins                                           | 23 |

| 6.4 Registers                                               |    |

| 6.4.1 Register List                                         |    |

| 6.4.2 Detailed Register Descriptions                        |    |

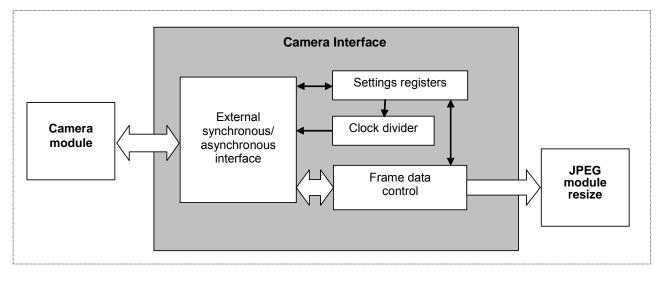

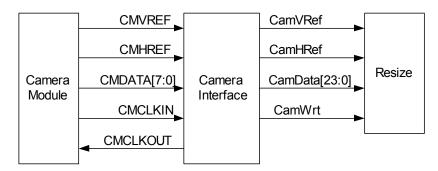

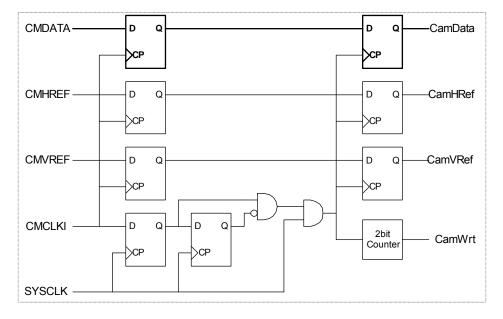

| 7. CAMERA INTERFACE (CAM)                                   |    |

| 7.1 Overview                                                |    |

| 7.2 Block Diagram                                           |    |

| 7.3 External Pins                                           |    |

| 7.4 Registers                                               |    |

| 7.4.1 Register List<br>7.4.2 Detailed Register Descriptions |    |

| 7.5 Description of Operation                                |    |

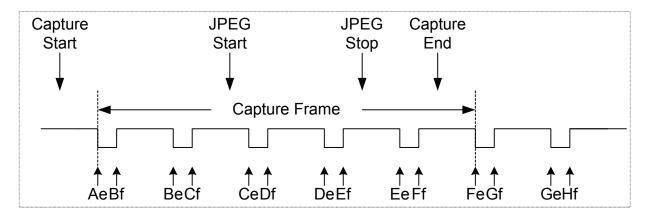

| 7.5.1 Frame Capture Interrupt Requests                      |    |

| 8. JPEG CONTROLLER (JPG)                                    | 46 |

| 8.1 Overview                                                | 46 |

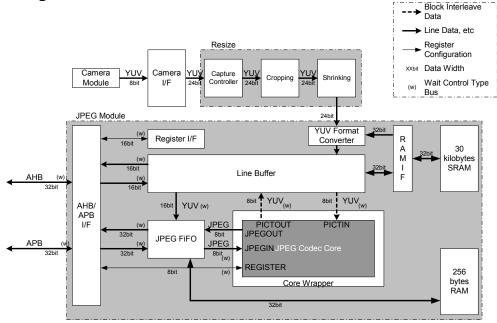

| 8.2 Block Diagram                                           | 46 |

| 8.3 External Pins                                           | 46 |

| 8.4 Registers                                               |    |

| 8.4.1 Register List                                         |    |

| 8.4.2 Resizer Operation Registers (RSZ)             |     |

|-----------------------------------------------------|-----|

| 8.4.3 JPEG Module Registers (JCTL)                  |     |

| 8.4.4 JPEG FIFO Setting Registers (JFIFO)           |     |

| 8.4.5 JPEG Line Buffer Setting Registers (JLB)      |     |

| 8.4.6 JPEG Codec Registers (JCODEC)                 |     |

| 8.5 Description of Operation                        | 76  |

| 8.5.1 Capture Control                               |     |

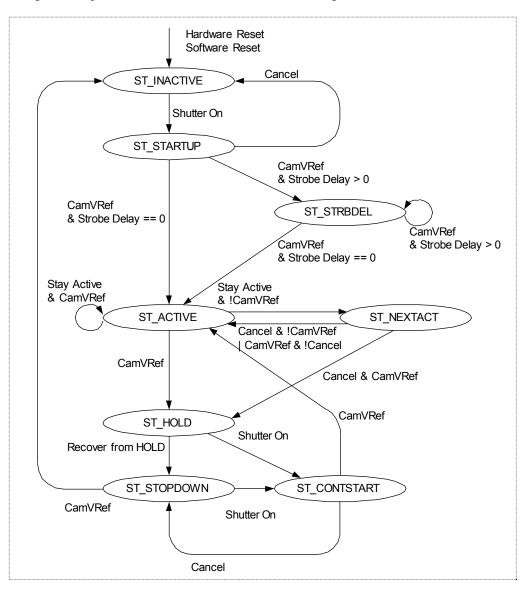

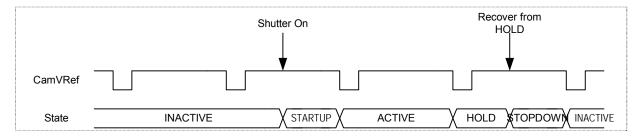

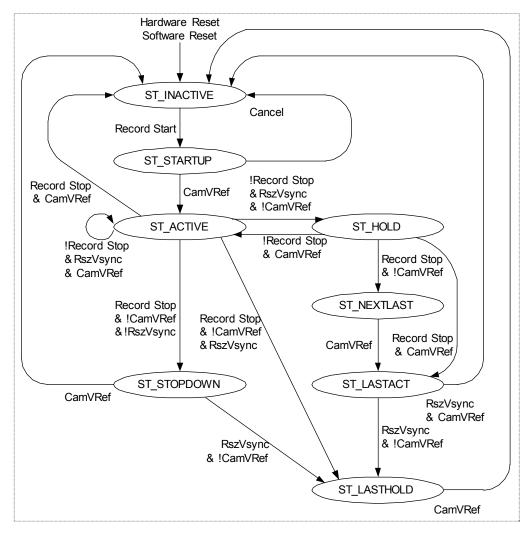

| 8.5.1.1 State Machine for Camera Image JPEG Encode  |     |

| 8.5.1.2 State Machine for YUV Data Capture          |     |

| 8.5.2 Capture Resizer                               |     |

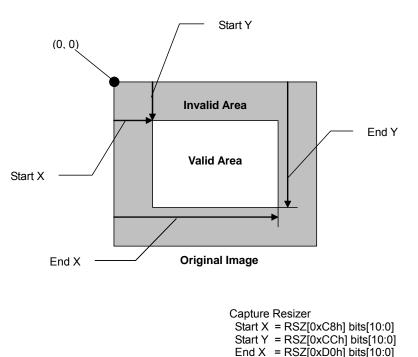

| 8.5.2.1 Trimming                                    |     |

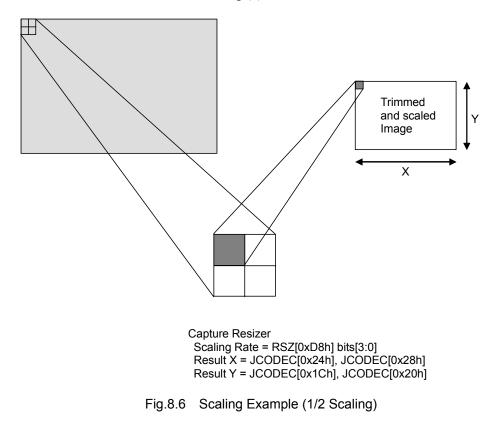

| 8.5.2.2 Scaling                                     |     |

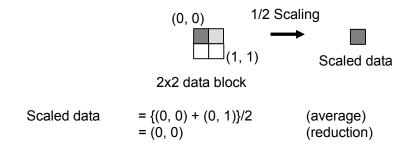

| 8.5.2.2.1 1/2 Scaling                               |     |

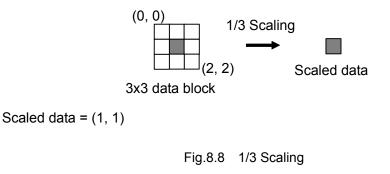

| 8.5.2.2.2 1/3 Scaling                               |     |

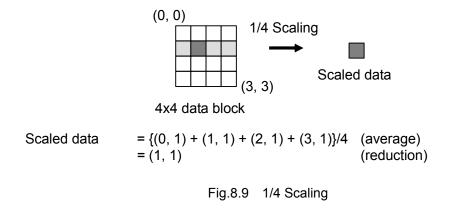

| 8.5.2.2.3 1/4 Scaling                               |     |

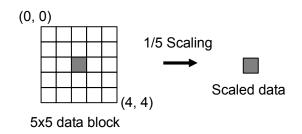

| 8.5.2.2.4 1/5 Scaling                               |     |

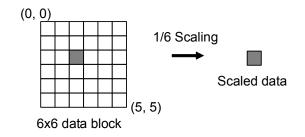

| 8.5.2.2.5 1/6 Scaling                               |     |

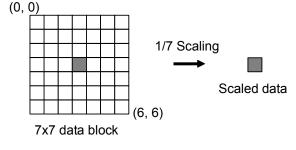

| 8.5.2.2.6 1/7 Scaling                               |     |

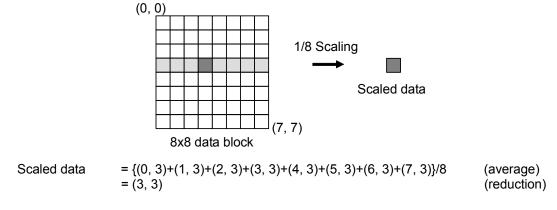

| 8.5.2.2.7 1/8 Scaling                               |     |

| 8.5.2.3 Usage Restrictions                          |     |

| 8.5.3 Image Processing Data Flow                    |     |

| 8.5.3.1 Camera Image JPEG Encode                    |     |

| 8.5.3.2 YUV Data Capture                            |     |

| 8.5.3.3 YUV Data JPEG Encode                        |     |

| 8.5.3.4 YUV Data JPEG Decode                        |     |

| 8.5.4 JPEG Codec Functions                          |     |

| 8.5.4.1 Invalid JPEG Files                          |     |

| 8.5.4.2 Usage Restrictions for JPEG Codec Registers |     |

| 8.5.5 Functions other than JPEG Codec               |     |

| 8.5.5.1 JPEG FIFO                                   |     |

| 8.5.5.2 JPEG Line Buffer                            |     |

| 8.5.5.3 YUV Data Format Converter                   |     |

| 8.5.5.4 JPEG Module Interrupt Requests              |     |

| 8.5.5.5 JPEG 180° Rotation Encode                   |     |

| 8.5.5.6 YUV Data Formats                            |     |

| 8.5.5.7 JPEG Module Software Reset                  |     |

| 8.5.5.8 JPEG Marker Fast Output Mode                |     |

| 8.5.6 Sample Sequences                              |     |

| 8.5.6.1 Camera Image JPEG Encode (Single Frame)     |     |

| 8.5.6.2 Shutting Down                               |     |

| 9. JPEG_DMAC (JDMA)                                 |     |

| 9.1 Overview                                        |     |

|                                                     |     |

| 9.2 Block Diagram                                   |     |

| 9.3 External Pins                                   | 101 |

| 9.4 Registers                                       |     |

| 9.4.1 Register List                                 |     |

| 9.4.2 Detailed Register Descriptions                |     |

|                                                     |     |

| 10. DMA CONTROLLER 2 (DMAC2)                        |     |

| 10.1 Overview                                       |     |

| 10.2 Block Diagram                                  |     |

| 10.3 External Pins                                  |     |

|                                                     |     |

| 10.4 Registers                                      |     |

| 10.4.1 Register List.                               |     |

| 10.4.2 Detailed Register Descriptions               |     |

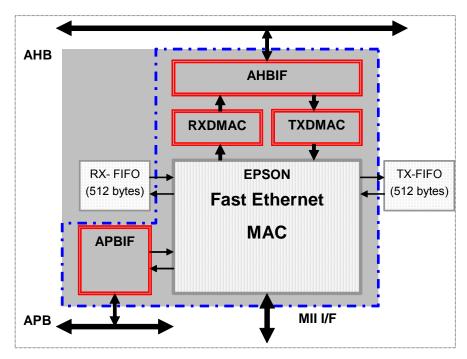

| 11. ETHERNET MAC & E-DMA (ETH)                                                                                                                                                                                                                                                                                                                                                                                           | 114                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                    |

| 11.1.1 Features                                                                                                                                                                                                                                                                                                                                                                                                          | 114                                                                                                                                                                                |

| 11.2 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                    |

| 11.3 External Pins                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                    |

| 11.4 Registers                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                    |

| 11.4.1 Register List                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                    |

| 11.4.2 Detailed Register Descriptions                                                                                                                                                                                                                                                                                                                                                                                    | 117                                                                                                                                                                                |

| 11.5 Description of Operation                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                    |

| 11.5.1 MAC Functions                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                    |

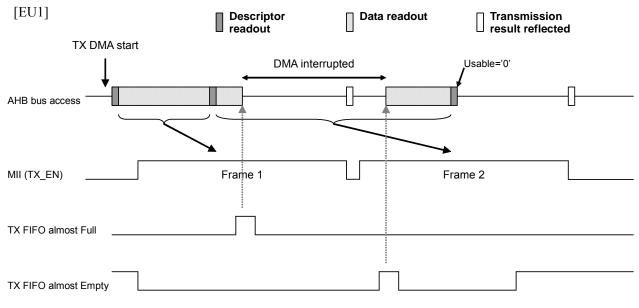

| 11.5.1.1 Transmit                                                                                                                                                                                                                                                                                                                                                                                                        | 129                                                                                                                                                                                |

| 11.5.1.2 Receive                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                    |

| 11.5.1.3 Flow Control                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                    |

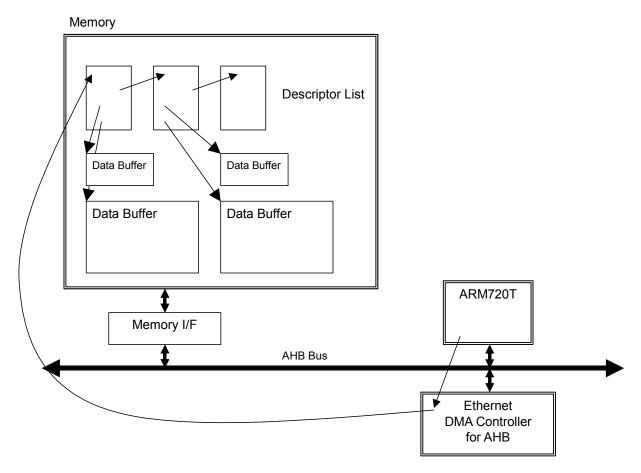

| 11.5.2 DMA Controller                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                    |

| 11.5.2.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                    |

| 11.5.2.2 Descriptor Tables<br>11.5.2.3 Transmit DMA Description of Operation                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                    |

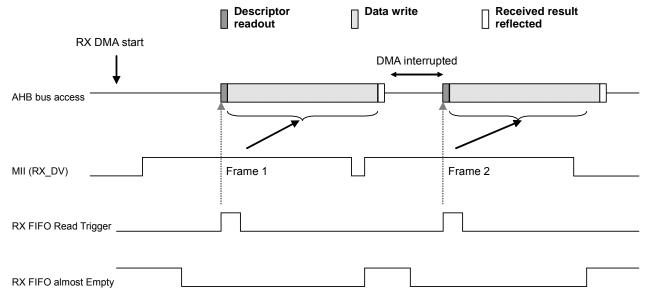

| 11.5.2.4 Receive DMA Description of Operation                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                    |

| 11.5.2.5 DMA and MAC Operating Mode Settings                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                    |

| 11.5.3 Address Filter                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                    |

| 11.5.4 MIIM                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                    |

| 11.5.4.1 Write Operation                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                    |

| 11.5.4.2 Read Operation                                                                                                                                                                                                                                                                                                                                                                                                  | 140                                                                                                                                                                                |

| 11.5.5 Receive Buffer Management Function                                                                                                                                                                                                                                                                                                                                                                                | 140                                                                                                                                                                                |

| 11.6 Limitations on the Use of the Ethernet MAC and E-DMA (ETH)                                                                                                                                                                                                                                                                                                                                                          | 141                                                                                                                                                                                |

| 12. APB BRIDGE (APB)                                                                                                                                                                                                                                                                                                                                                                                                     | 142                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                    |

| 12.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                            | 1/2                                                                                                                                                                                |

| 12.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                    |

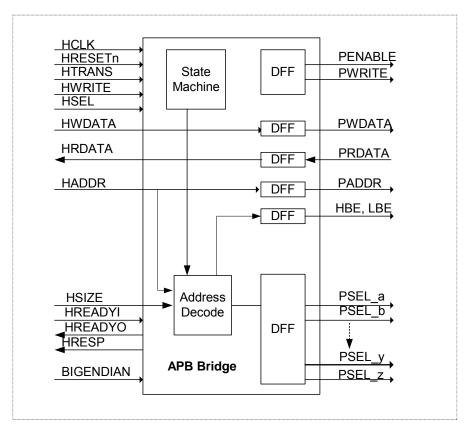

| 12.2 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                       | 142                                                                                                                                                                                |

| 12.2 Block Diagram<br>12.3 External Pins                                                                                                                                                                                                                                                                                                                                                                                 | 142<br>143                                                                                                                                                                         |

| 12.2 Block Diagram<br>12.3 External Pins<br>12.4 Registers                                                                                                                                                                                                                                                                                                                                                               | 142<br>143<br>143                                                                                                                                                                  |

| <ul> <li>12.2 Block Diagram</li> <li>12.3 External Pins</li> <li>12.4 Registers</li> <li>12.4.1 Register List</li> </ul>                                                                                                                                                                                                                                                                                                 | 142<br>143<br>143<br>                                                                                                                                                              |

| 12.2 Block Diagram<br>12.3 External Pins<br>12.4 Registers                                                                                                                                                                                                                                                                                                                                                               | 142<br>143<br>143<br>                                                                                                                                                              |

| 12.2 Block Diagram         12.3 External Pins         12.4 Registers         12.4.1 Register List         12.4.2 Detailed Register Descriptions                                                                                                                                                                                                                                                                          |                                                                                                                                                                                    |

| 12.2 Block Diagram         12.3 External Pins         12.4 Registers         12.4.1 Register List         12.4.2 Detailed Register Descriptions         13. SYSTEM CONTROLLER (SYS)                                                                                                                                                                                                                                      |                                                                                                                                                                                    |

| 12.2 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                    |

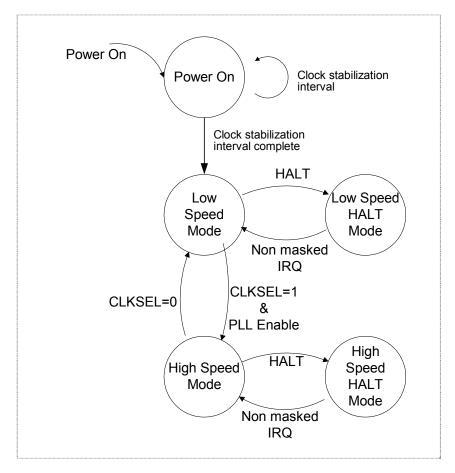

| 12.2 Block Diagram.         12.3 External Pins         12.4 Registers         12.4.1 Register List.         12.4.2 Detailed Register Descriptions         13. SYSTEM CONTROLLER (SYS)         13.1 Overview         13.2 Operation States                                                                                                                                                                                |                                                                                                                                                                                    |

| 12.2 Block Diagram.         12.3 External Pins         12.4 Registers         12.4.1 Register List.         12.4.2 Detailed Register Descriptions         13. SYSTEM CONTROLLER (SYS)         13.1 Overview         13.2 Operation States         13.2.1 POWER ON state                                                                                                                                                  |                                                                                                                                                                                    |

| 12.2 Block Diagram.         12.3 External Pins         12.4 Registers         12.4.1 Register List.         12.4.2 Detailed Register Descriptions         13. SYSTEM CONTROLLER (SYS)         13.1 Overview         13.2 Operation States         13.2.1 POWER ON state         13.2.2 LOW SPEED mode (32kHz mode)                                                                                                       |                                                                                                                                                                                    |

| 12.2 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                       | 142<br>143<br>143<br>143<br>143<br>143<br>143<br>145<br>145<br>145<br>145<br>146<br>146<br>146                                                                                     |

| 12.2 Block Diagram.         12.3 External Pins         12.4 Registers         12.4.1 Register List.         12.4.2 Detailed Register Descriptions         13. SYSTEM CONTROLLER (SYS)         13.1 Overview         13.2 Operation States         13.2.1 POWER ON state         13.2.2 LOW SPEED mode (32kHz mode)                                                                                                       | 142<br>143<br>143<br>143<br>143<br>143<br>143<br>145<br>145<br>145<br>145<br>146<br>146<br>146<br>146                                                                              |

| 12.2 Block Diagram.         12.3 External Pins         12.4 Registers         12.4.1 Register List.         12.4.2 Detailed Register Descriptions         13. SYSTEM CONTROLLER (SYS)         13.1 Overview         13.2 Operation States         13.2.1 POWER ON state         13.2.2 LOW SPEED mode (32kHz mode)         13.2.3 LOW SPEED HALT mode         13.2.4 HIGH SPEED mode         13.2.5 HIGH SPEED HALT mode | 142<br>143<br>143<br>143<br>143<br>143<br>143<br>145<br>145<br>145<br>145<br>146<br>146<br>146<br>146<br>146                                                                       |

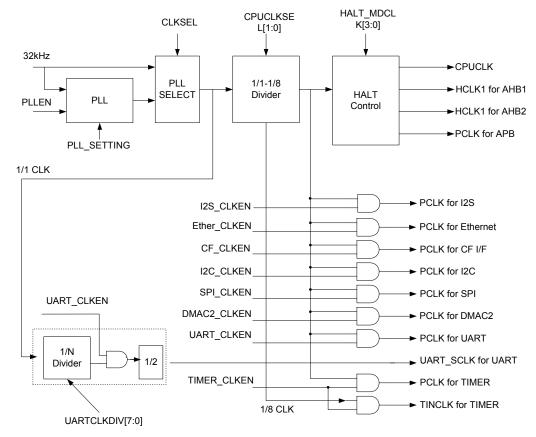

| 12.2 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                       | 142<br>143<br>143<br>143<br>143<br>143<br>143<br>145<br>145<br>145<br>145<br>146<br>146<br>146<br>146<br>146<br>146<br>146                                                         |

| 12.2 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                       | 142<br>143<br>143<br>143<br>143<br>143<br>143<br>145<br>145<br>145<br>145<br>146<br>146<br>146<br>146<br>146<br>146<br>146<br>146                                                  |

| 12.2 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                       | 142<br>143<br>143<br>143<br>143<br>143<br>143<br>145<br>145<br>145<br>145<br>146<br>146<br>146<br>146<br>146<br>146<br>146<br>147                                                  |

| 12.2 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                       | 142<br>143<br>143<br>143<br>143<br>143<br>143<br>145<br>145<br>145<br>145<br>146<br>146<br>146<br>146<br>146<br>146<br>146<br>146<br>146<br>147                                    |

| <ul> <li>12.2 Block Diagram</li></ul>                                                                                                                                                                                                                                                                                                                                                                                    | 142<br>143<br>143<br>143<br>143<br>143<br>145<br>145<br>145<br>145<br>145<br>146<br>146<br>146<br>146<br>146<br>146<br>146<br>146<br>147<br>147                                    |

| 12.2 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                       | 142<br>143<br>143<br>143<br>143<br>143<br>143<br>145<br>145<br>145<br>145<br>146<br>146<br>146<br>146<br>146<br>146<br>146<br>146<br>147<br>147<br>147<br>147                      |

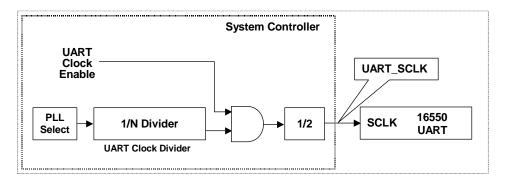

| 12.2 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                       | 142<br>143<br>143<br>143<br>143<br>143<br>143<br>145<br>145<br>145<br>145<br>146<br>146<br>146<br>146<br>146<br>146<br>146<br>146<br>146<br>147<br>147<br>147<br>147<br>155<br>156 |

| 12.2 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                       | 142<br>143<br>143<br>143<br>143<br>143<br>143<br>145<br>145<br>145<br>145<br>146<br>146<br>146<br>146<br>146<br>146<br>146<br>146                                                  |

| <ul> <li>12.2 Block Diagram</li> <li>12.3 External Pins</li></ul>                                                                                                                                                                                                                                                                                                                                                        | 142<br>143<br>143<br>143<br>143<br>143<br>143<br>143<br>145<br>145<br>145<br>146<br>146<br>146<br>146<br>146<br>146<br>146<br>146                                                  |

| 12.2 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                       | 142<br>143<br>143<br>143<br>143<br>143<br>143<br>145<br>145<br>145<br>145<br>146<br>146<br>146<br>146<br>146<br>146<br>146<br>146                                                  |

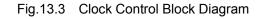

| 14. MEMORY CONTROLLER (MEMC)1                                     | 159 |

|-------------------------------------------------------------------|-----|

| 14.1 Overview                                                     |     |

| 14.1.1 SRAM Controller                                            |     |

| 14.1.2 SDRAM Controller                                           | 159 |

| 14.1.3 External Bus Interface Module                              |     |

| 14.2 Block Diagram                                                |     |

| 14.3 External Pins                                                |     |

| 14.4 Memory Controller                                            |     |

| 14.4.1 Device Count                                               |     |

| 14.4.2 Memory Types                                               |     |

| 14.4.5 External Memory Bus Width                                  |     |

| 14.5 SRAM Control                                                 |     |

| 14.5.1 Device Selection                                           | -   |

| 14.5.2 Timing Settings                                            |     |

| 14.5.3 Write Protection                                           |     |

| 14.6 SDRAM Control                                                | 162 |

| 14.6.1 Device Selection                                           |     |

| 14.6.2 Mode Register Settings                                     |     |

| 14.6.3 Burst Support.                                             |     |

| 14.6.4 Auto Precharge Settings<br>14.6.5 Power Saving             |     |

| 14.6.6 Stopping the Memory Clock                                  |     |

| 14.6.7 Power Save Mode Support                                    |     |

| 14.6.8 Auto Refresh Control                                       | 163 |

| 14.6.9 Self Refresh Control                                       |     |

| 14.6.10 Status Register                                           | 163 |

| 14.7 Registers                                                    |     |

| 14.7.1 Register List                                              |     |

| 14.7.2 Detailed Register Descriptions                             |     |

| 14.8 Limitations on the Use of the Memory Controller (MEMC)       |     |

| 14.9 Configuration Register for Device[2:0] Setting Example       | 176 |

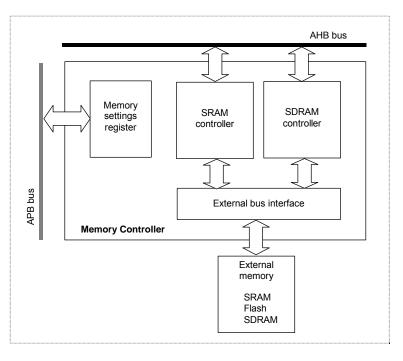

| 15. INTERRUPT CONTROLLER (INT)1                                   | 177 |

| 15.1 Overview                                                     | 177 |

| 15.2 Block Diagram                                                | 178 |

| 15.3 Fast (FIQ) Interrupt Requests                                | 178 |

| 15.4 Normal (IRQ) Interrupt Requests                              |     |

| 15.5 External Pins                                                |     |

| 15.6 Registers                                                    | -   |

| 15.6.1 Register List                                              |     |

| 15.6.2 Detailed Register Descriptions                             |     |

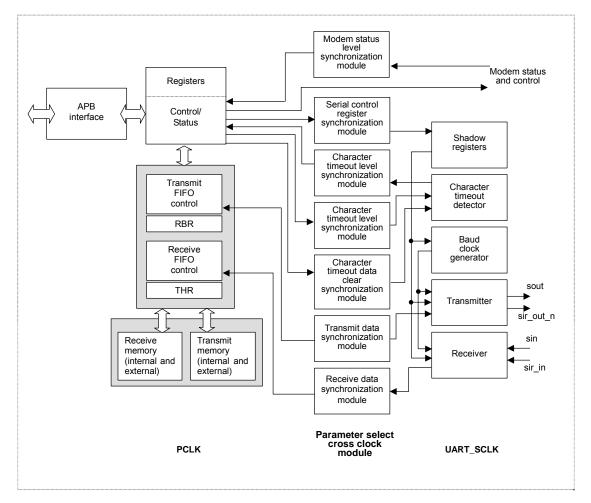

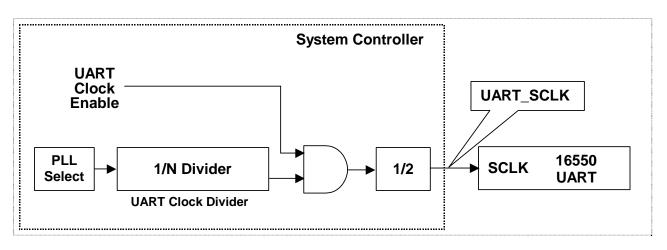

| 16. UART1                                                         | 185 |

| 16.1 Overview                                                     |     |

|                                                                   |     |

| 16.2 Block Diagram                                                |     |

| 16.3 External Pins                                                |     |

| 16.4 Registers                                                    |     |

| 16.4.1 Register List<br>16.4.2 Important Notes on Register Access |     |

| 16.4.3 Detailed Register Descriptions                             |     |

| 16.4.4 Sample Baud Rate Settings                                  |     |

| 16.5 Usage Limitations                                            | 200 |

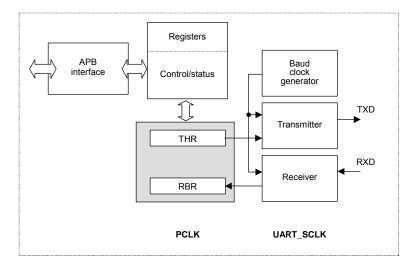

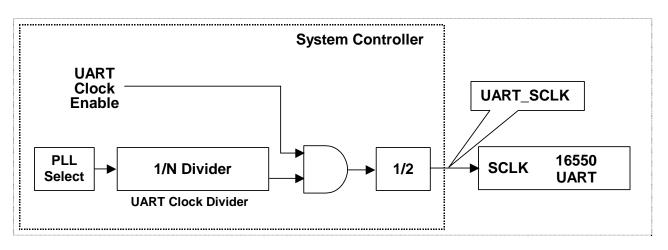

| 17. UART LITE                                                             | 201 |

|---------------------------------------------------------------------------|-----|

| 17.1 Overview                                                             |     |

| 17.2 Block Diagram                                                        | 201 |

| 17.3 External Pins                                                        | 201 |

| 17.4 Registers                                                            | 202 |

| 17.4.1 Register List                                                      |     |

| 17.4.2 Important Notes on Register Access                                 |     |

| 17.4.3 Detailed Register Descriptions<br>17.4.4 Sample Baud Rate Settings |     |

| 17.5 Usage Limitations                                                    |     |

| 18. I <sup>2</sup> C SINGLE MASTER CORE MODULE (I2C)                      |     |

| 18.1 Overview                                                             |     |

| 18.1.1 Master Mode                                                        |     |

| 18.1.2 Slave Mode                                                         |     |

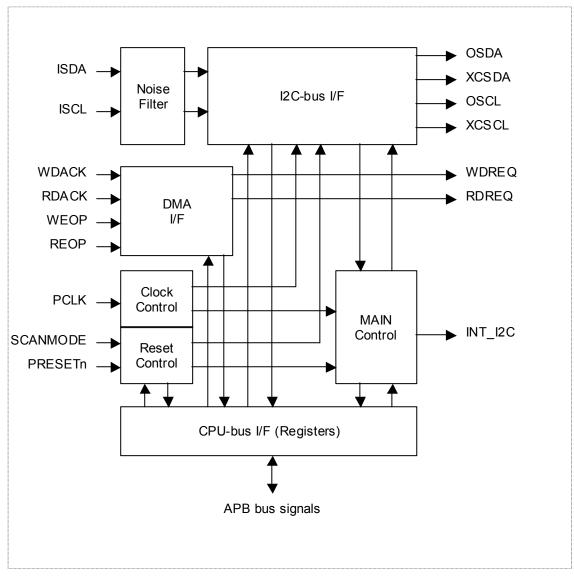

| 18.2 Block Diagram                                                        | 210 |

| 18.3 External Pins                                                        | 210 |

| 18.4 Registers                                                            |     |

| 18.4.1 Register List                                                      |     |

| 18.4.2 Detailed Register Descriptions                                     |     |

| 18.5 Description of Operation (Sample Bus Control Commands)               |     |

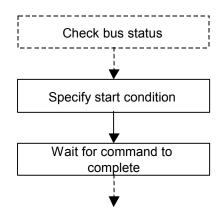

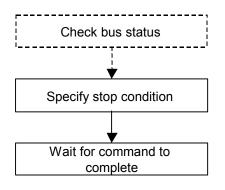

| 18.5.1 Sample Start (S) Flowchart<br>18.5.2 Sample Stop (P) Flowchart     |     |

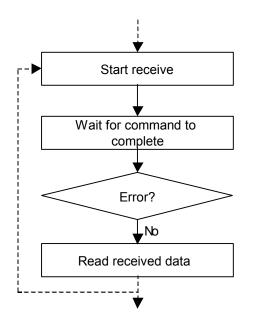

| 18.5.3 Sample Receive (R) Flowchart                                       |     |

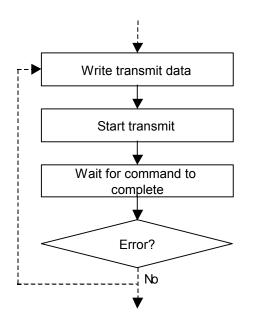

| 18.5.4 Sample Transfer (T) Flowchart                                      |     |

| 18.5.5 Sample Sequence for Write to Slave Device                          |     |

| 18.5.6 Sample Sequence for Read from Slave Device                         |     |

| 18.6 Usage Limitations                                                    | 223 |

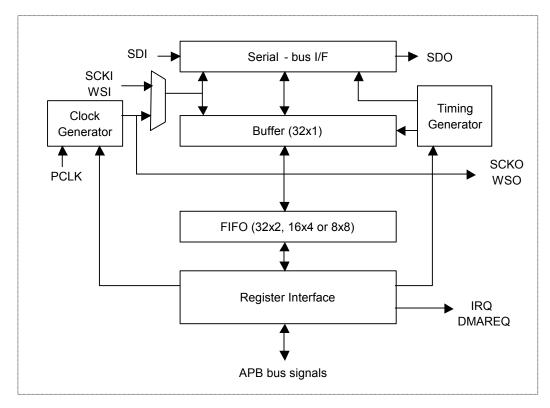

| 19. I <sup>2</sup> S (I2S)                                                | 224 |

| 19.1 Overview                                                             |     |

| 19.1.1 Features                                                           |     |

| 19.2 Block Diagram                                                        | 224 |

| 19.3 External Pins                                                        | 225 |

| 19.4 Registers                                                            |     |

| 19.4.1 Register List.                                                     |     |

| 19.4.2 Detailed Register Descriptions                                     |     |

| <b>19.5 Functional Description</b>                                        |     |

| 19.5.2 Data Width and Number of FIFO Stages                               |     |

| 19.5.3 DMA Transfers                                                      |     |

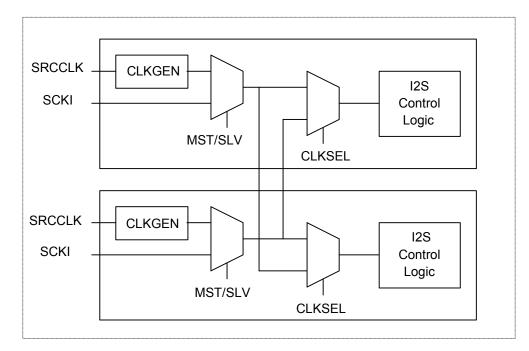

| 19.5.4 Sharing Clock Signals                                              |     |

| 19.5.5 Conversion from Monaural to Stereo                                 |     |

| 19.6 Sample Settings                                                      | 235 |

| 20. SERIAL PERIPHERAL INTERFACE (SPI)                                     | 236 |

| 20.1 Overview                                                             |     |

| 20.1.1 Master Mode                                                        |     |

| 20.1.2 Slave Mode                                                         |     |

| 20.2 Block Diagram                                                        |     |

| 20.3 External Pins                                                        |     |

| 20.4 Clock and Data Transfer Timing                                       |     |

| 20.5 Registers                                                            | 241 |

| 20.5.1 Register List                                                                         |     |

|----------------------------------------------------------------------------------------------|-----|

| 20.5.2 Detailed Register Description                                                         | 241 |

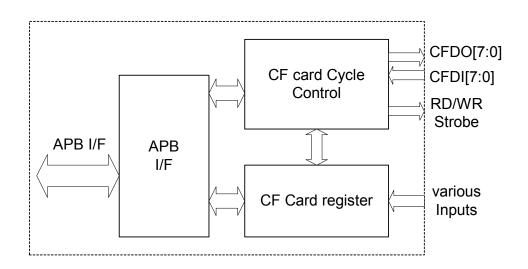

| 21. COMPACT FLASH INTERFACE (CF)                                                             |     |

| 21.1 Overview                                                                                |     |

| 21.2 Block Diagram                                                                           |     |

| 21.3 Compact Flash (CF) Card Interface Memory Map                                            |     |

| 21.4 External Pins                                                                           |     |

| 21.5 Registers                                                                               |     |

| 21.5.1 Register List                                                                         |     |

| 21.5.2 Detailed Register Descriptions                                                        |     |

| 21.6 Usage Limitations                                                                       | 253 |

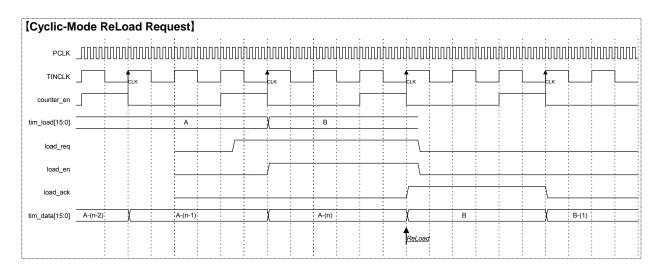

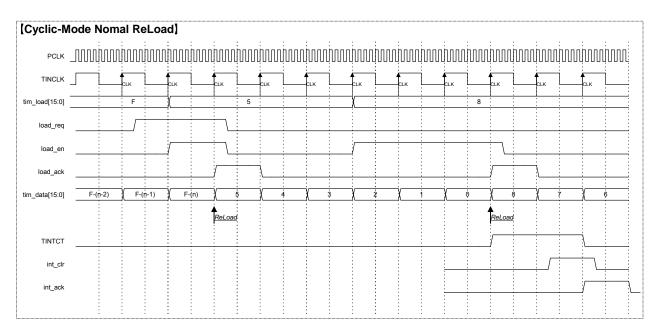

| 22. TIMERS (TIM)                                                                             | 254 |

| 22.1 Overview                                                                                | 254 |

| 22.2 Block Diagram                                                                           | 254 |

| 22.3 External Pins                                                                           | 255 |

| 22.4 Registers                                                                               | 255 |

| 22.4.1 Register List                                                                         |     |

| 22.4.2 Detailed Register Descriptions                                                        |     |

| 22.5 Loading (and Reloading) Timer Counters                                                  |     |

| 22.5.1 Timer/Counter Modes                                                                   |     |

| 22.6 Sample: Timer Clock Settings (1 kHz, 1 MHz)<br>22.6.1 Setting for Divider and prescaler |     |

| 22.0.1 Setting for Divider and prescaler                                                     |     |

| 22.7 1 Cyclic Mode, Immediate Load Request                                                   |     |

| 22.7.2 Cyclic Mode, Normal Reload                                                            |     |

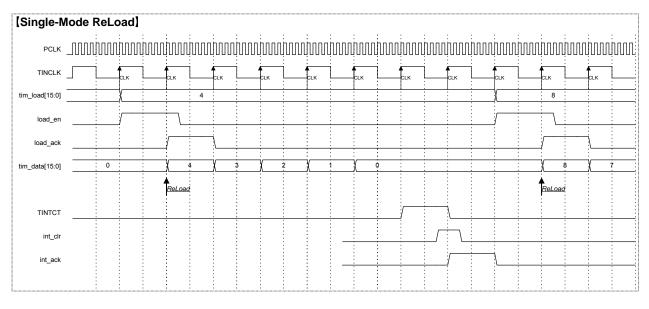

| 22.7.3 Single Mode, Normal Reload                                                            |     |

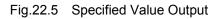

| 22.7.4 Port Output                                                                           |     |

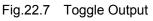

| 23. REAL-TIME CLOCK (RTC)                                                                    |     |

| 23.1 Overview                                                                                |     |

| 23.2 Block Diagram                                                                           |     |

| 23.3 External Pins                                                                           |     |

| 23.4 Registers                                                                               |     |

| 23.4.1 Register List.                                                                        |     |

| 23.4.2 Detailed Register Descriptions                                                        |     |

| 23.5 Configuring Real-Time Clock Registers<br>23.5.1 After Power On Reset                    |     |

| 23.5.2 Stopping and Restarting                                                               |     |

| 23.5.3 Reconfiguring On the Fly                                                              |     |

| 23.5.4 System Reset During Operation                                                         |     |

| 23.5.5 Important Notes on Programming                                                        |     |

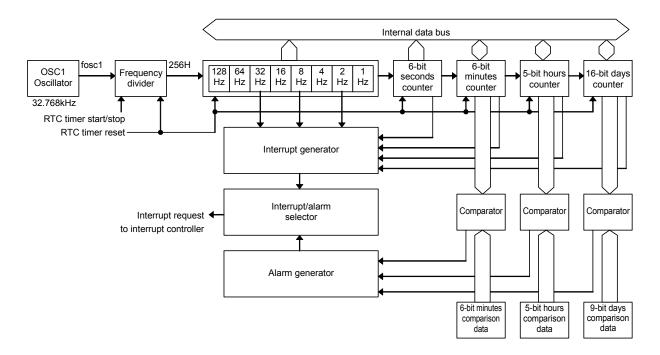

| 24. WATCHDOG TIMER (WDT)                                                                     |     |

| 24.1 Overview                                                                                |     |

| 24.2 Block Diagram                                                                           |     |

| 24.3 External Pins                                                                           |     |

| 24.4 Registers                                                                               |     |

| 24.4.1 Register List                                                                         |     |

| 24.4.2 Detailed Register Descriptions                                                        |     |

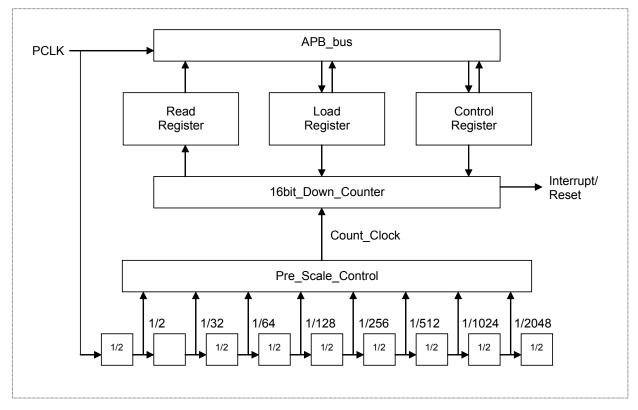

| 25. GENERAL PURPOSE I/O (GPIO)                                                               |     |

| 25.1 Overview                                                                                |     |

| 25.2 External Pins                                                            | 279 |

|-------------------------------------------------------------------------------|-----|

| 25.3 Registers                                                                |     |

| 25.3.1 Register List                                                          |     |

| 25.3.2 Detailed Register Descriptions                                         |     |

| 25.3.2.1 Data and Function Registers                                          |     |

| 25.3.2.2 GPIOB Registers                                                      |     |

| 25.3.2.3 GPIOC Registers                                                      |     |

| 25.3.2.4 GPIOD Registers                                                      |     |

| 25.3.2.5 GPIOE Registers                                                      |     |

| 25.3.2.6 GPIOF Registers                                                      |     |

| 25.3.2.7 GPIOG Registers                                                      |     |

| 25.3.2.8 GPIOH Registers                                                      |     |

| 25.3.2.9 GPIOA/GPIOB Interrupt Request Registers                              |     |

| 25.4 GPIOA/GPIOB Interrupt Request Logic                                      |     |

| 26. ABSOLUTE MAXIMUM RATINGS                                                  | 290 |

| 26.1 Absolute Maximum Ratings                                                 |     |

| 26.2 Recommend Operation Conditions                                           |     |

| •                                                                             |     |

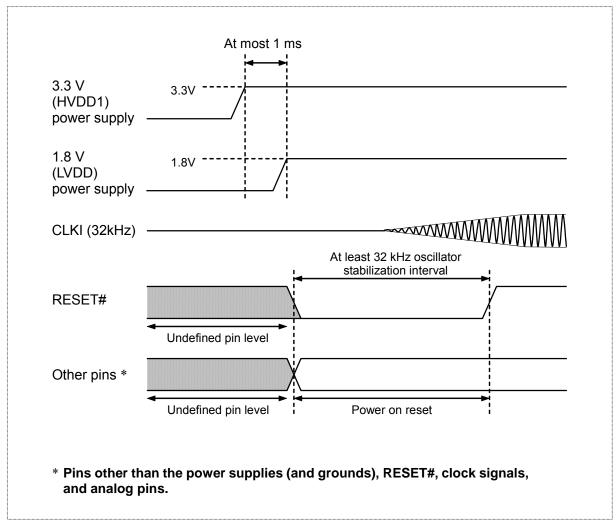

| 26.3 Power Supply Timing                                                      |     |

| 26.4 Shut Down Timing                                                         |     |

| 27. ELECTRICAL CHARACTERISTICS                                                | 292 |

| 27.1 DC Characteristics                                                       |     |

| 27.2 AC Characteristics                                                       |     |

| 27.2.1 AC Characteristics Measuring Conditions                                |     |

| 27.2.2 AC Characteristics Timing                                              |     |

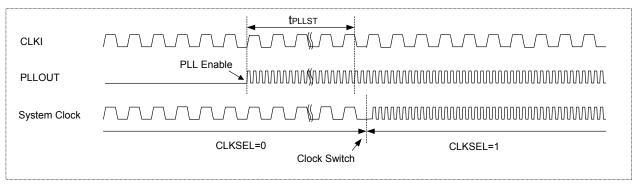

| 27.2.2.1 Clock Timing                                                         |     |

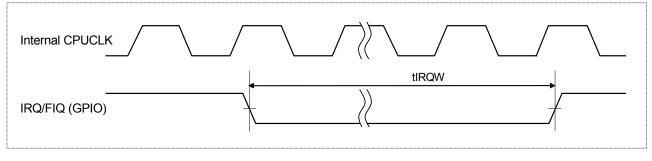

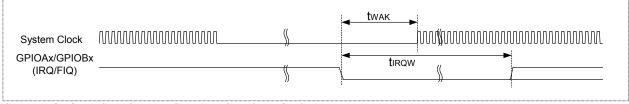

| 27.2.2.2 CPU Control Signal Timing                                            |     |

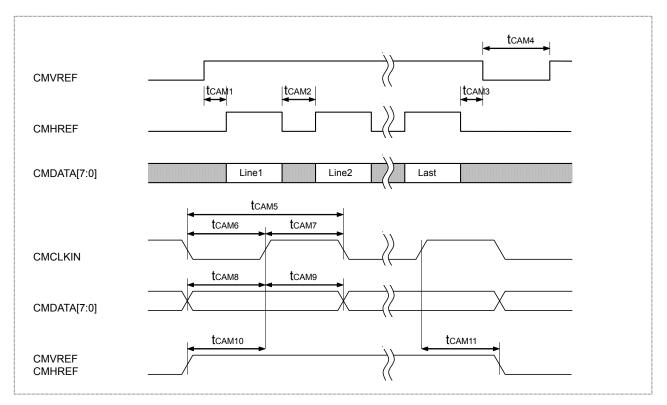

| 27.2.2.3 Camera Interface (CAM) Timing                                        |     |

| 27.2.2.4 Media Independent Interface Ethernet PHY (MII PHY) Timing            |     |

| 27.2.2.5 Memory Controller (MEMC) Timing                                      |     |

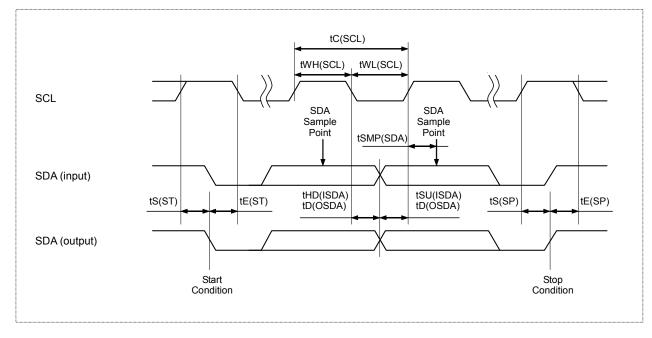

| 27.2.2.6 I <sup>2</sup> C Single Master Core Module (I <sup>2</sup> C) Timing |     |

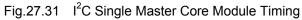

| 27.2.2.7 I <sup>2</sup> S Timing                                              |     |

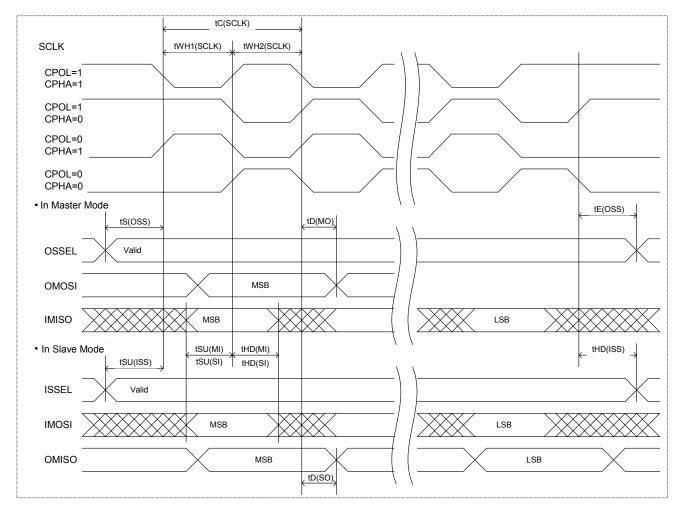

| 27.2.2.8 Serial Peripheral Interface (SPI) Timing                             |     |

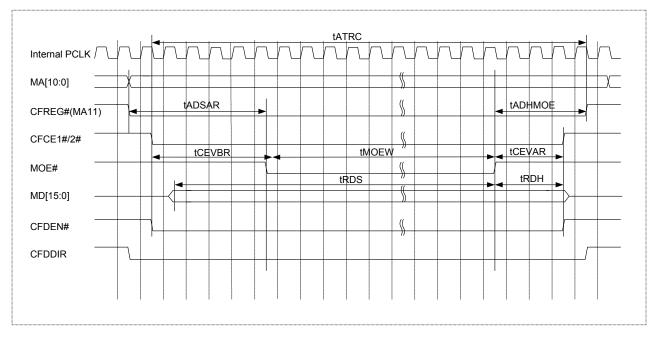

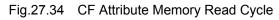

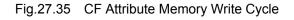

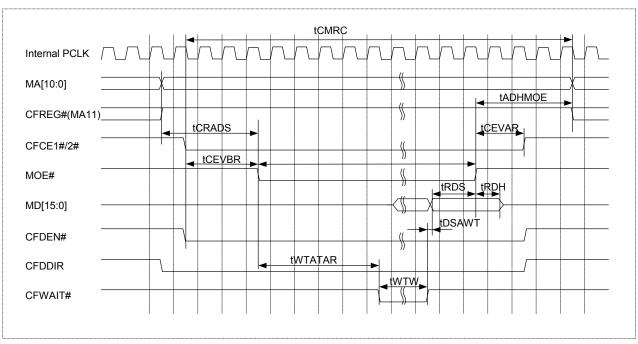

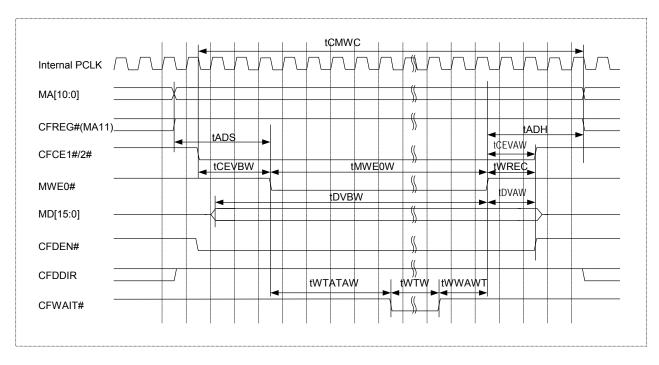

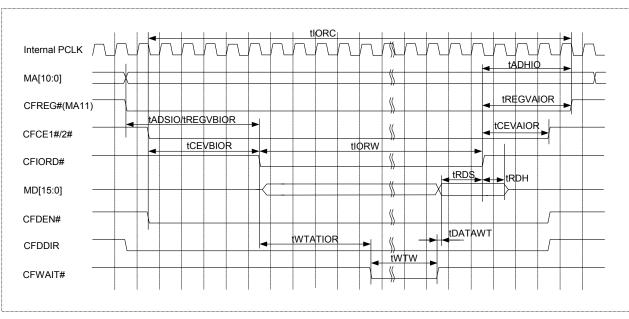

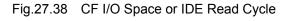

| 27.2.2.9 Compact Flash Interface (CF) Timing                                  |     |

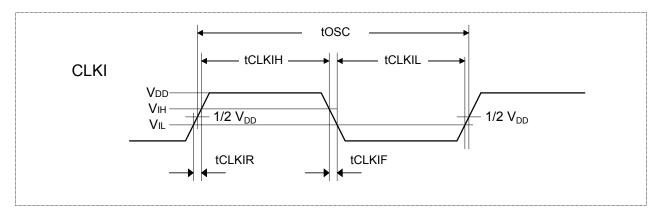

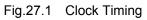

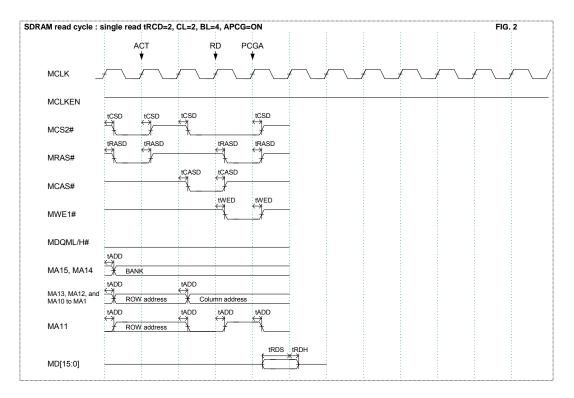

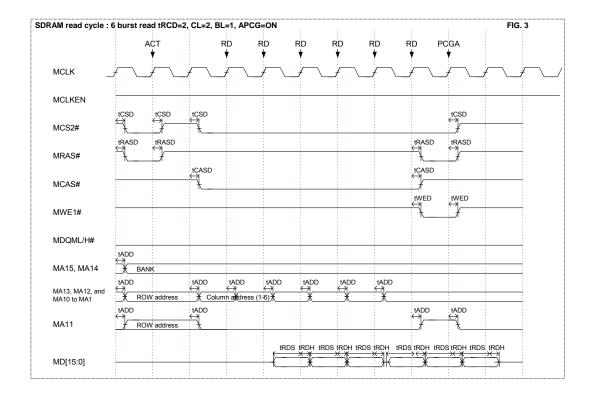

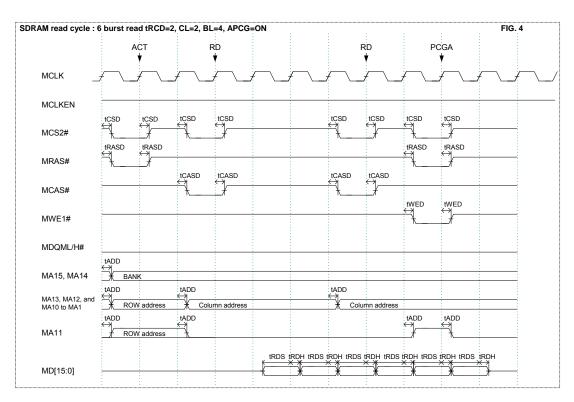

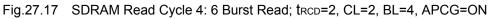

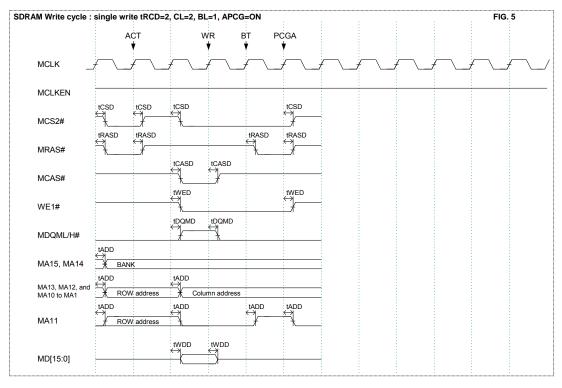

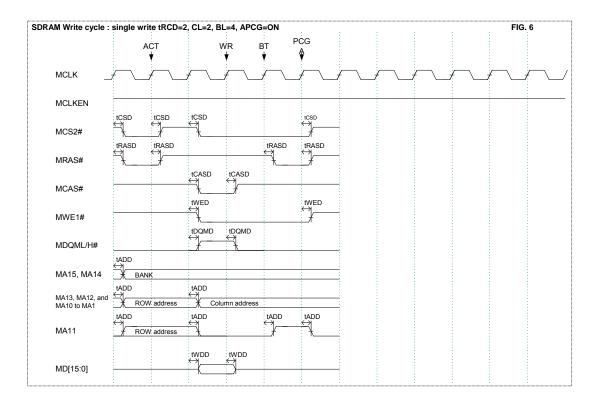

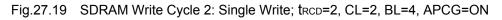

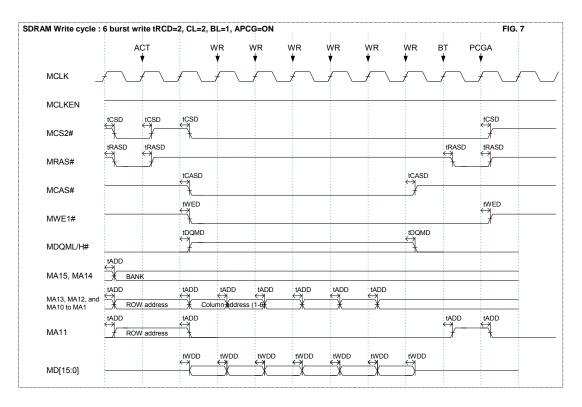

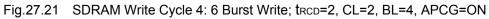

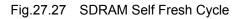

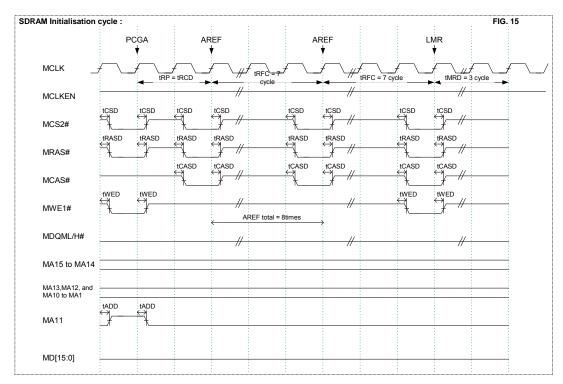

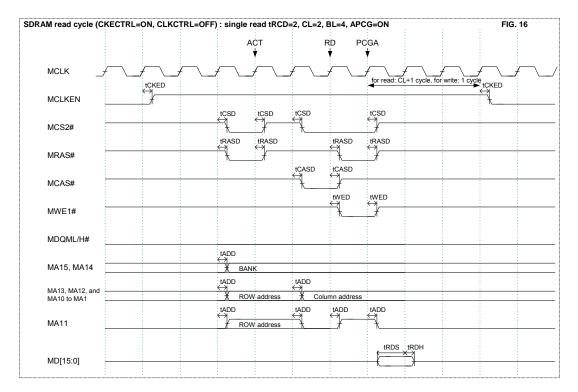

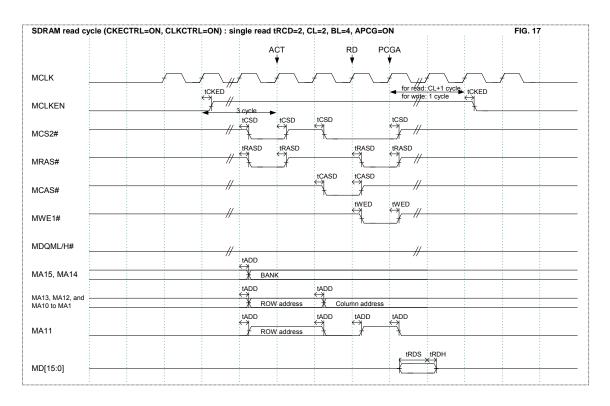

| 27.2.3 Timing Charts                                                          | 299 |

| 27.2.3.1 Clock Timing                                                         |     |

| 27.2.3.2 CPU Control Signal Timing                                            | 300 |

| 27.2.3.3 Camera Interface Timing                                              |     |

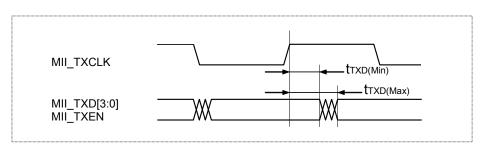

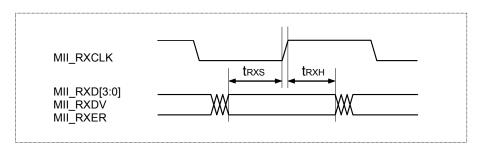

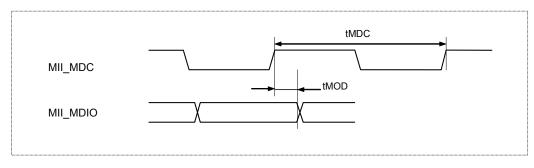

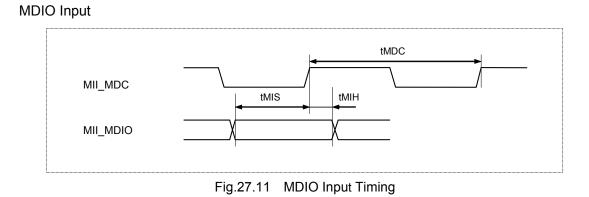

| 27.2.3.4 Media Independent Interface Ethernet PHY (MII PHY) Timing            | 303 |

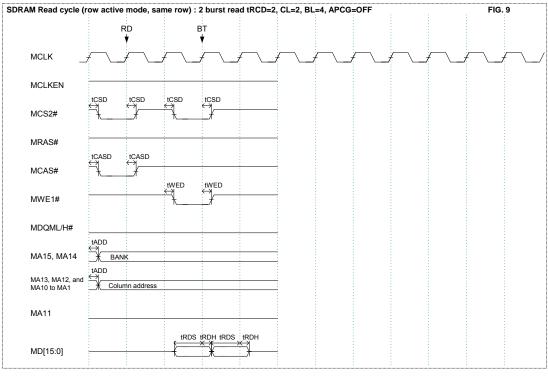

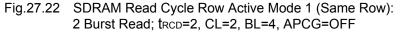

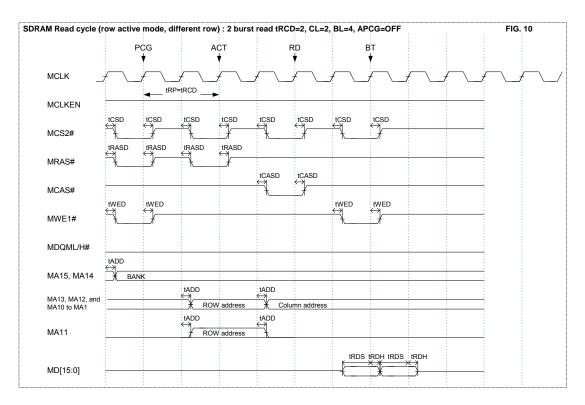

| 27.2.3.5 Memory Interface Controller                                          | 304 |

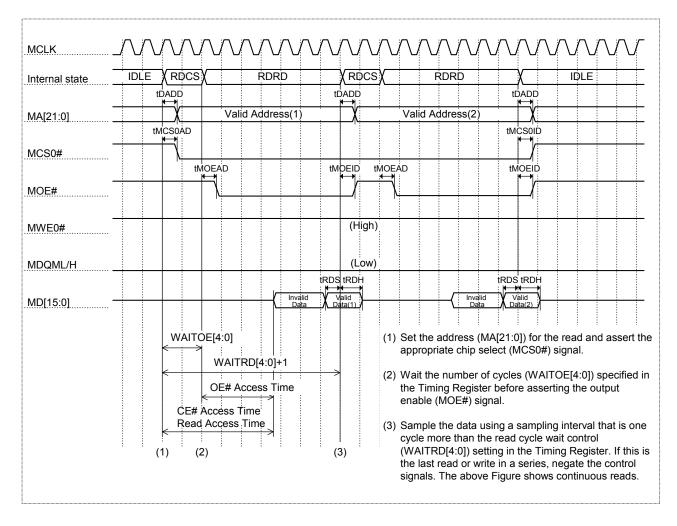

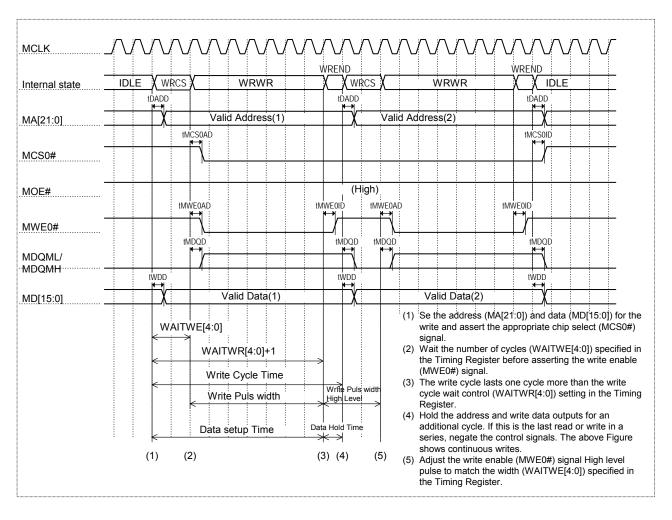

| 27.2.3.5.1 Static Memory Controller Timing (Flash EEPROM, SRAM, etc.)         |     |

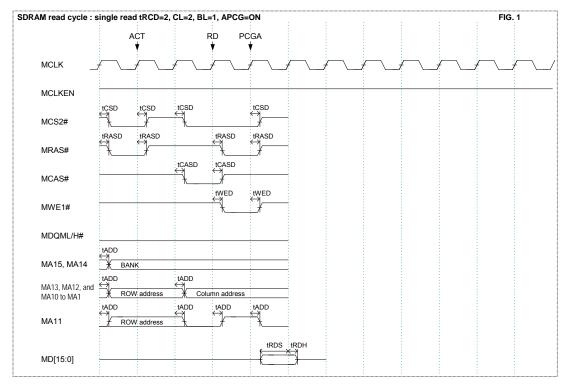

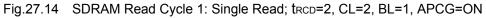

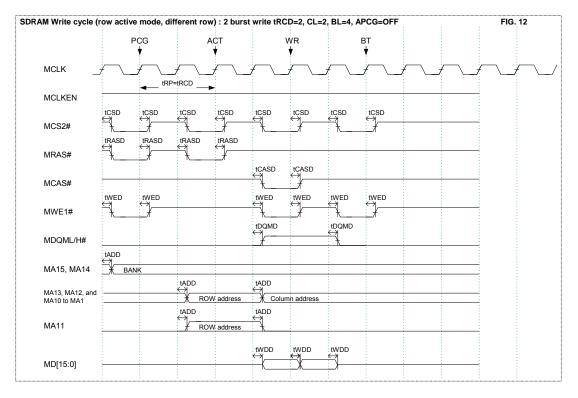

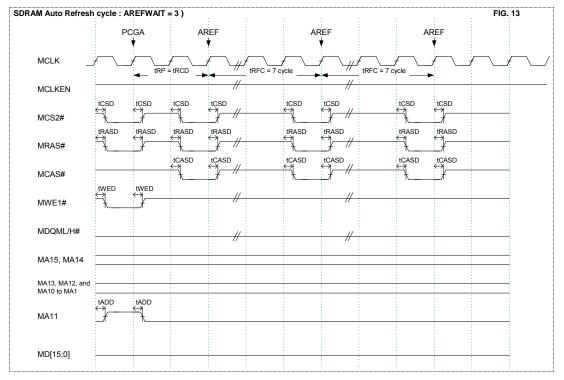

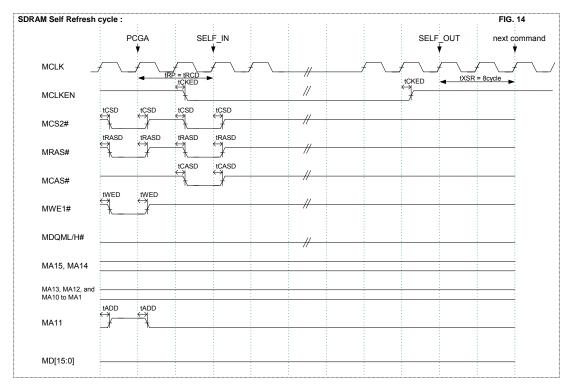

| 27.2.3.5.2 SDRAM Controller AC Timing                                         |     |

| 27.2.3.6 I <sup>2</sup> C Single Master Core Module Timing                    |     |

| 27.2.3.7 I <sup>2</sup> S Timing                                              |     |

| 27.2.3.8 Serial Peripheral Interface (SPI) Timing                             |     |

| 27.2.3.9 Compact Flash Interface (CF) Timing                                  |     |

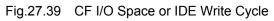

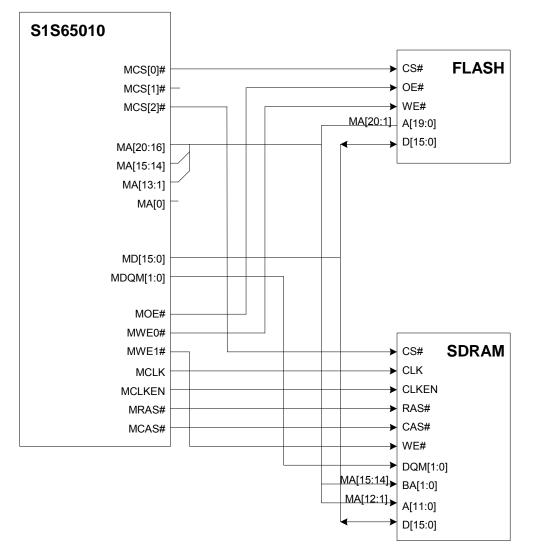

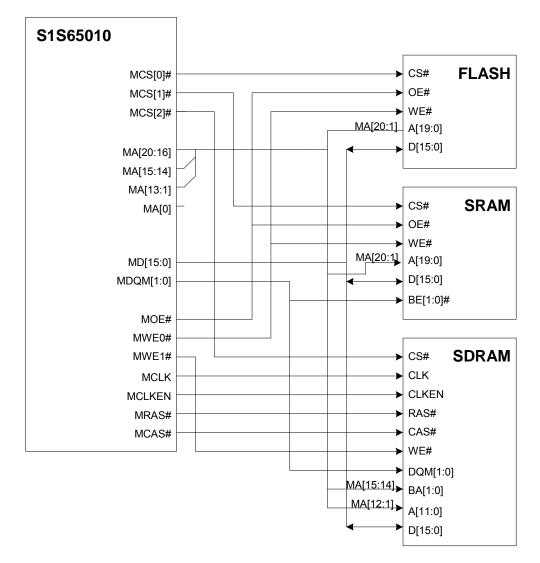

| 28. REFERENCE: SAMPLE EXTERNAL CONNECTIONS                                    | 320 |

| 28.1 Sample Memory Connections                                                |     |

| 28.2 Sample Compact Flash Connections: 16-Bit Bus                             | 322 |

| 28.3 Sample Serial Peripheral Interface (SPI) Connections                     |     |

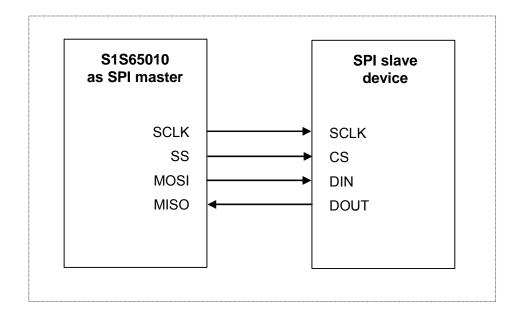

| 28.3.1 As Master                                                              |     |

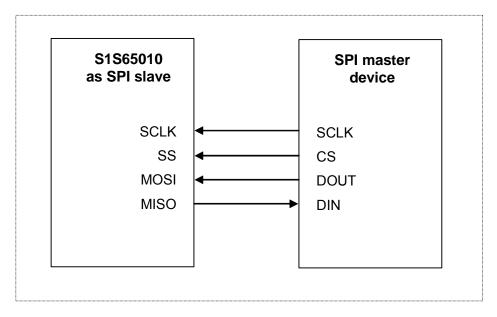

| 28.3.2 As Slave                                                               |     |

| 28.4 Sample I <sup>2</sup> S Connections                                      |     |

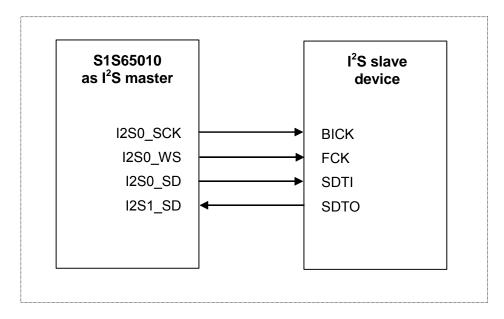

| 28.4.1 As Master                                                              |     |

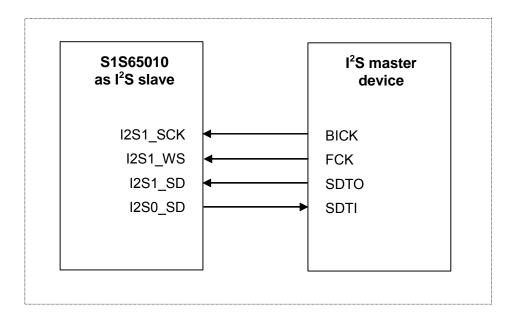

| 28.4.2 As Slave                                            | 324 |

|------------------------------------------------------------|-----|

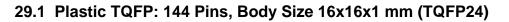

| 29. EXTERNAL DIMENSIONS                                    | 325 |

| 29.1 Plastic TQFP: 144 Pins, Body Size 16x16x1 mm (TQFP24) | 325 |

| 30. REVISION HISTORY                                       | 326 |

| 31. Appendix 1. S1S65010 Internal Register List            | 333 |

# **1. OVERVIEW**

This S1S65010 network camera controller is ideal for applications involving Internet cameras. It incorporates networking and protocol processing support, a camera interface, and a JPEG encoder, so constructing an Internet camera is as simple as connecting a camera module, an external Ethernet PHY device, and a Flash EEPROM containing the firmware.

Shutter commands from clients trigger image capture from the camera and JPEG encoding. Configuring this device as an HTTP server on a LAN, for example, allows clients to request image files. Image capture and transfer to the specified client can be continuous, at a fixed interval controlled by a built-in timer, or in response to a trigger from an interrupt request pin connected to an external sensor or other device. Image transfers can also take the form e-mail attachments.

This device improves upon the S1S65000 with higher frame rates (30 fps at VGA resolution), a higher maximum resolution (UXGA), two  $I^2S$  interfaces/modules for voice/audio data, and other new or enhanced functionality for constructing better Internet cameras.

This device allows network devices access to the GPIO ports and  $I^2C$  bus for use in specifying camera settings and controlling motors and other external equipment. This product ships with the necessary device drivers.

### 1.1 Features

- Internet camera operating totally independently of personal computers

- Pin compatibility and upward software compatibility with S1S65000

- Frame rate of 30 fps at VGA resolution

- Support for a broad range of camera modules, right up to 2-megapixel (about 2 million pixels)

- Audio support by I<sup>2</sup>S

- Compression to JPEG format with hardware JPEG encoder (ISO 10918 compliant)

- Settings control over network

- E-mail delivery of images files

- Power saving by wake-up mode which reperats start, shooting and pause periodically

- Wireless LAN (802.11b) connectivity using Compact Flash (CF) interface

- Single-chip solution for lower system costs

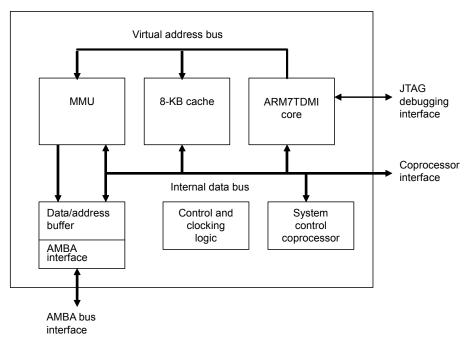

- Built-in ARM720T Rev 4.3 CPU with 8 KB cache and running at up to 50 MHz

### **1.2 Internal Functional Blocks**

#### CPU:

- 32-bit RISC ARM720T (maximum clock: 50 MHz)

- Free switching between full 32-bit instruction set and more efficient 16-bit Thumb code

- 31 general-purpose 32-bit registers

- Built-in multiplier

#### RAM:

• 78 KB of embedded RAM as workspace shared by CPU, JPEG, and Ethernet blocks

### Camera Input and JPEG Encoder:

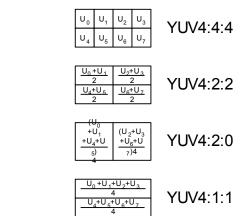

- 8-bit parallel interface using YUV 4-2-2 format

- Image sizes up to UXGA (1600 × 1200): UXGA, SXGA, XGA, VGA, QVGA, CIF, and QCIF

- Support ITU-R BT656 form

- Hardware JPEG encoder

- Max 30 fps at VGA resolution; 30 fps also at CIF resolution

- The pixel clock frequency for the camera data input is less than 2/3 of the CPU clocks.

### JPEG Block:

- Hardware JPEG encoder

- Resize (subscreen extraction) function

- Dedicated line buffer

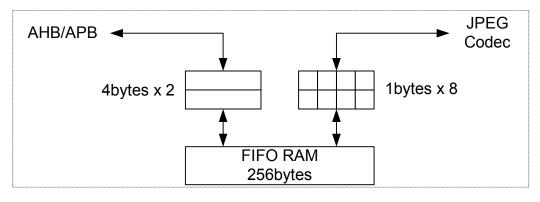

- Built-in variable-capacity FIFO for JPEG encoder output

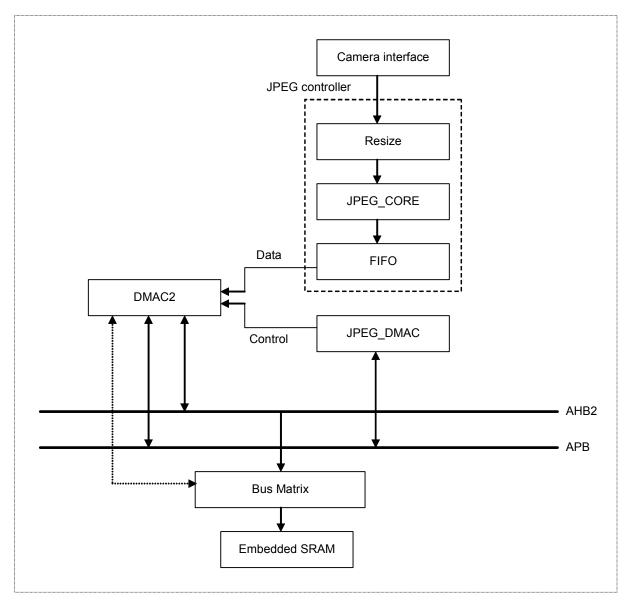

- Built-in Enhanced DMA

#### **Networking:**

- 10/100 Base Ethernet MAC controller supporting both full duplex and half duplex operation

- IEEE 802.3 Clause 22 compliant media independent interface (MII)

- Built-in Enhanced DMA

### **External Memory Controller:**

- 16-bit data bus

- Support for 2 to 128 MB of SDRAM

- Support for up to 16 MB of static memory (Flash EEPROM or SRAM)

- Support for three chapter select signals (SDRAM, Flash, plus one other)

### **CF Card Interface:**

- Compliant with CF+ Specifications Rev 1.4

- Adaptable for use as interface to wireless LAN, PHS card, and other devices

- Support for true IDE mode

### **Standby Operation:**

- HALT mode suspending the clock signal to the CPU when the latter is not needed

- I/O clock control suspending the clock signals to major I/O blocks

### Timer and Watchdog Timer:

- Three 16-bit timers

- Choice of reload/cyclic or one-shot operation

- Support for toggle or port output upon underflow output

- Watchdog timer triggering interrupt request or reset signal

### Serial Interfaces:

- UART: Software compatible with the 16550 interface

- UART Lite: Limited subset of 16550 software interface

- SPI: Clock synchronous interface

- I<sup>2</sup>C master interface for camera interface and general-purpose applications

- Two I<sup>2</sup>S interfaces/modules for audio data, compliant with the Philips I<sup>2</sup>S standard

#### Interrupt Controller:

• Support for two fast (FIQ) and 32 normal (IRQ) interrupt requests

#### Real-Time Clock:

- Supports days, hours, minutes, and seconds

- Internal timer taps (1/128 to 1/2) for use as interrupt request sources

- Support for alarms and interrupt requests

### GPIO:

- General-purpose I/O ports (maximum 57)

- Programmable I/O direction for all port pins

- Alternate I/O functions available for some port pins

#### **Power Supplies:**

- 3.3 V I/O power supply

- 1.8 V Core power supply

- 1.8 V PLL analog power supply

- 2.4 V to 3.6 V Camera I/O power supply

### Package:

• 144-pin TQFP (TQFP24),  $16 \times 16 \times 1$  mm, 0.4 mm pin pitch

# **1.3 Supported Protocols**

ARP, ICMP, IP, TCP, UDP, HTTPd, SMTP, DHCP, FTP, DNS resolver, telnet

Necessary protocols can be added or updated by rewriting Flash ROM. Addition or update by the customer is also possible.

Protocols are prepared as EPSON's sample software or partner's products.

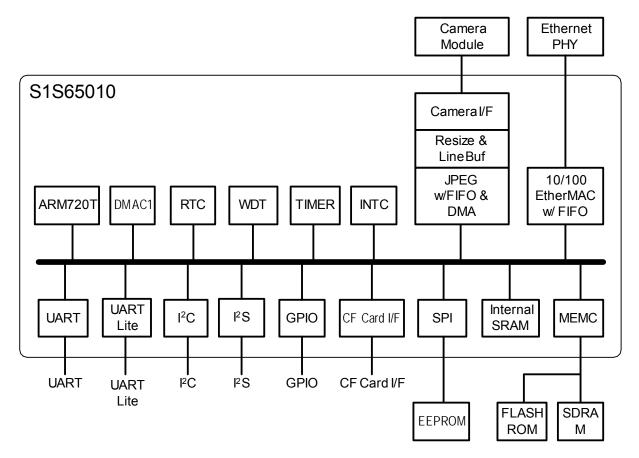

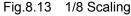

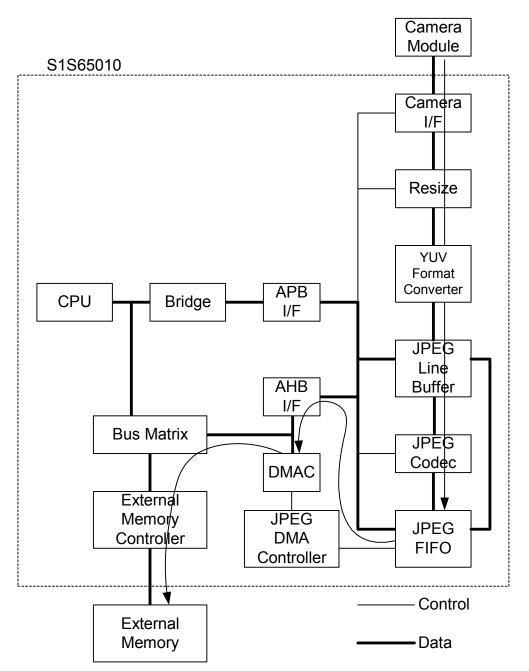

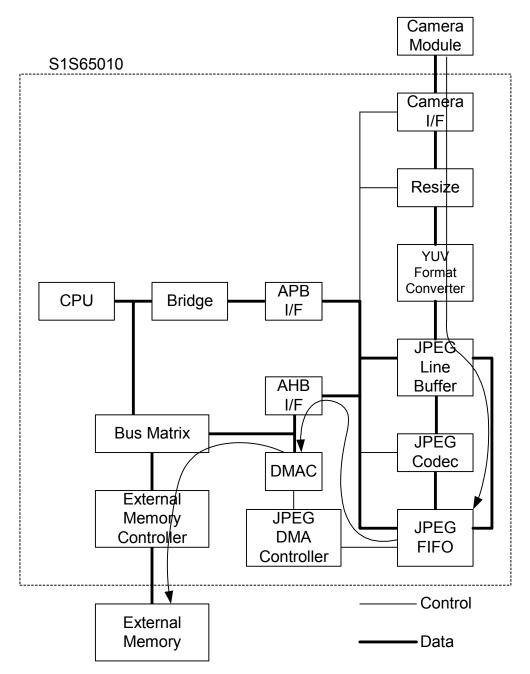

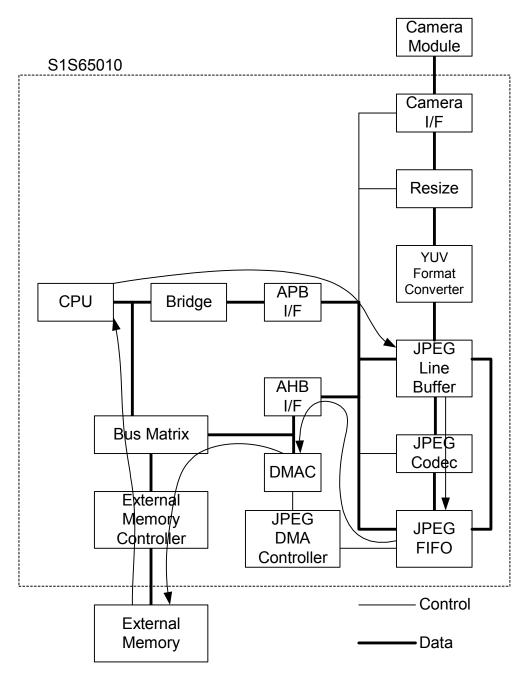

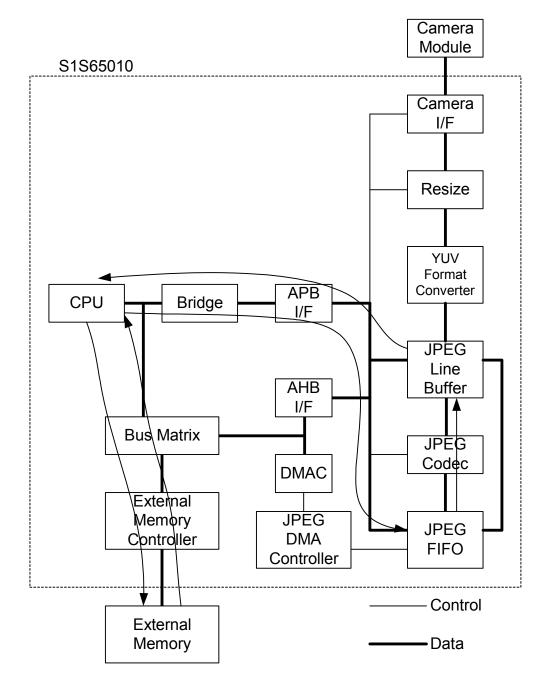

# 2. BLOCK DIAGRAM

Fig.2.1 S1S65010 Block Diagram

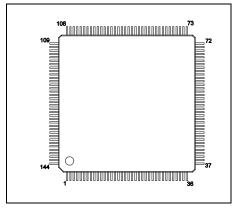

# 3. PINS

Fig.3.1 Pin Layout (Top View)

| Pin No. | Pin Name | Pin No. | Pin Name  | Pin No. | Pin Name | Pin No. | Pin Name  |

|---------|----------|---------|-----------|---------|----------|---------|-----------|

| 1       | MA14     | 37      | MD12      | 73      | TRST#    | 109     | CMDATA5   |

| 2       | MA15     | 38      | MD13      | 74      | TCK      | 110     | CMDATA6   |

| 3       | MA16     | 39      | MD14      | 75      | TMS      | 111     | CMDATA7   |

| 4       | MA17     | 40      | MD15      | 76      | TDI      | 112     | VSS       |

| 5       | MA18     | 41      | MDQML     | 77      | TDO      | 113     | LVDD      |

| 6       | VSS      | 42      | MDQMH     | 78      | VSS      | 114     | GPIOD0    |

| 7       | MA19     | 43      | HVDD1     | 79      | GPIOA0   | 115     | GPIOD1    |

| 8       | MCS2#    | 44      | VSS       | 80      | GPIOA1   | 116     | CFCE2#    |

| 9       | MCS1#    | 45      | MII_CRS   | 81      | GPIOA2   | 117     | CFCE1#    |

| 10      | MCS0#    | 46      | MII_COL   | 82      | GPIOA3   | 118     | CFIORD#   |

| 11      | LVDD     | 47      | MII_TXD3  | 83      | GPIOA4   | 119     | CFIOWR#   |

| 12      | MOE#     | 48      | MII_TXD2  | 84      | GPIOA5   | 120     | CFIREQ    |

| 13      | MWE0#    | 49      | MII_TXD1  | 85      | GPIOA6   | 121     | CFRST     |

| 14      | MWE1#    | 50      | LVDD      | 86      | GPIOA7   | 122     | VSS       |

| 15      | HVDD1    | 51      | MII_TXD0  | 87      | HVDD1    | 123     | HVDD1     |

| 16      | MCLKEN   | 52      | MII_TXEN  | 88      | VSS      | 124     | CFWAIT#   |

| 17      | MCLK     | 53      | MII_TXCLK | 89      | GPIOB0   | 125     | CFSTSCHG# |

| 18      | VSS      | 54      | MII_RXER  | 90      | GPIOB1   | 126     | CFDEN#    |

| 19      | MRAS#    | 55      | VSS       | 91      | GPIOB2   | 127     | CFDDIR    |

| 20      | MCAS#    | 56      | HVDD1     | 92      | GPIOB3   | 128     | MA0       |

| 21      | MD0      | 57      | MII_RXCLK | 93      | LVDD     | 129     | MA1       |

| 22      | MD1      | 58      | MII_RXDV  | 94      | GPIOB4   | 130     | MA2       |

| 23      | MD2      | 59      | MII_RXD0  | 95      | GPIOB5   | 131     | MA3       |

| 24      | MD3      | 60      | MII_RXD1  | 96      | GPIOB6   | 132     | VSS       |

| 25      | VSS      | 61      | LVDD      | 97      | GPIOB7   | 133     | LVDD      |

| 26      | LVDD     | 62      | MII_RXD2  | 98      | VSS      | 134     | MA4       |

| 27      | MD4      | 63      | MII_RXD3  | 99      | CMHREF   | 135     | MA5       |

| 28      | MD5      | 64      | MII_MDC   | 100     | CMVREF   | 136     | MA6       |

| 29      | MD6      | 65      | MII_MDIO  | 101     | CMCLKIN  | 137     | MA7       |

| 30      | MD7      | 66      | VSS       | 102     | CMCLKOUT | 138     | MA8       |

| 31      | HVDD1    | 67      | CLKI      | 103     | CMDATA0  | 139     | HVDD1     |

| 32      | MD8      | 68      | PLLVSS    | 104     | CMDATA1  | 140     | MA9       |

| 33      | MD9      | 69      | VCP       | 105     | HVDD2    | 141     | MA10      |

| 34      | MD10     | 70      | PLLVDD    | 106     | CMDATA2  | 142     | MA11      |

| 35      | MD11     | 71      | RESET#    | 107     | CMDATA3  | 143     | MA12      |

| 36      | VSS      | 72      | TESTEN    | 108     | CMDATA4  | 144     | MA13      |

Note: A sharp (#) to the right of the pin name indicates an active low signal.

# 3.1 Pin Descriptions

- #: This symbol to the right of the pin name indicates a low active signal.

- Instruction of the symbol to the

Input pin

O: Output pin

I/O: Bidirectional pin

P: Power supply pin

| Table 3.1 | Cell Types |

|-----------|------------|

|-----------|------------|

| Cell Type | Description                                                     | Pin Examples                    |

|-----------|-----------------------------------------------------------------|---------------------------------|

| ICS       | LVCMOS Schmitt input                                            | TCK, CLKI, RESET#               |

| ICD1      | LVCMOS input with pull-down resistor (50k $\Omega$ @3.3V)       | TESTEN                          |

| ICU1      | LVCMOS input with pull-up resistor (50k $\Omega$ @3.3V)         | TMS, TDI                        |

| ICSU1     | LVCMOS Schmitt input with pull-up resistor (50k $\Omega$ @3.3V) | TRST#                           |

| BLNC4     | Low noise LVCMOS IO buffer (±4mA)                               | MII                             |

| BLNC4U1   | Low noise LVCMOS IO buffer with pull-up resistor                | CF interface                    |

| BLINC401  | (50kΩ@3.3V) (±4mA)                                              |                                 |

| BLNC4D2   | Low noise LVCMOS IO buffer with pull-down resistor              | MD [15:0]                       |

| DLINC4DZ  | (100kΩ@3.3V) (±4mA)                                             |                                 |

| BLNS4     | Low noise LVCMOS Schmitt IO buffer (±4mA)                       | GPIOA, GPIOB, GPIOD [1:0]       |

| BLNS4D1   | Low noise LVCMOS Schmitt IO buffer with pull-down               | Camera interface                |

| DLING4DT  | resistor (50kΩ@3.3V) (±4mA)                                     |                                 |

| OLN4      | Low noise output buffer (±4mA)                                  | MEMC interface (except MD pins) |

| OTLN4     | Low noise Tri-state output buffer (±4mA)                        | TDO                             |

| OLTR      | Low Voltage Transparent Output                                  | VCP                             |

| Pin Name       | Туре  | Cell Type | Pin No.                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|----------------|-------|-----------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| (MA [23:22])   | (I/O) | (BLNS4)   | (97-96)                             | For further details on these pins, see the GPIOB[7:6]                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| (11) ([20:22]) | (1,0) |           | (07 00)                             | description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| (MA [21:20])   | (I/O) | (BLNS4)   | (114-115)                           | For further details on these pins, see the GPIOD[1:0] description.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| MA [19:12]     | 0     | OLN4      | 7, 1-5,<br>143-144                  | Address outputs 19 to 12<br>SDRAM uses MA[15:14] as the bank address (BA[1:0]).                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| MA 11          | 0     | OLN4      | 142                                 | <ul> <li>This pin has more than one function.</li> <li>MA11:<br/>Address output 11 (default pin function after reset)</li> <li>CFREG#:<br/>Compact Flash (CF) interface REG signal specifying CF interface attribute and selecting I/O space</li> </ul>                                                                                                                                                                                                                                                               |  |  |  |

| MA [10:0]      | о     | OLN4      | 128-131,<br>134-138,<br>140-141     | <ul> <li>These pins have more than one function.</li> <li>MA[10:0]:<br/>Address outputs 10 to 0 (default pin function after reset)</li> <li>CFADDR[10:0]:<br/>CF interface address outputs 10 to 0</li> </ul>                                                                                                                                                                                                                                                                                                         |  |  |  |

| MD [15:0]      | I/O   | BLNC4D2   | 21-24,<br>27-30,<br>32-35,<br>37-40 | <ul> <li>These pins have more than one function.</li> <li>16-bit Data bus to memory (default pin function after reset)</li> <li>16-bit Data bus to CF interface</li> <li>MODESEL[15:0]:<br/>These input levels determine the internal operation mode.<br/>Sampling is at the end of a power on reset, when RESET# returns to High level from Low level. External pull-up resistances (approximately 4.7 to 10 kΩ) may therefore be necessary. For further details, see Section 4.1 "System Configuration."</li> </ul> |  |  |  |

| MCS [2:0]#     | 0     | OLN4      | 8-10                                | Chip select signals for memory (SDRAM or static)<br>MCS2# is for SDRAM.                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| MOE#           | 0     | OLN4      | 12                                  | <ul> <li>MCS2# IS for SDRAM.</li> <li>This pin has more than one function.</li> <li>MOE#:<br/>Memory output strobe signal (default pin function aff<br/>reset)</li> <li>CFOE#:<br/>CF interface output enable signal for attribute an<br/>common memory space</li> </ul>                                                                                                                                                                                                                                              |  |  |  |

| MWE0#          | 0     | OLN4      | 13                                  | <ul> <li>This pin has more than one function.</li> <li>MWE0#:<br/>Memory write enable signal for static memory (default pin function after reset)</li> <li>CFWE#:<br/>CF interface write enable signal for attribute and common memory space</li> </ul>                                                                                                                                                                                                                                                               |  |  |  |