# CMOS 32-BIT SINGLE CHIP MICROCOMPUTER **S1C33000** Core CPU Manual

**SEIKO EPSON CORPORATION**

#### NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency.

CMOS 32-BIT SINGLE CHIP MICROCOMPUTER S1C33000 Core CPU Manual

This manual explains the functions and instructions of the S1C33000 32-bit RISC CPU which is used as the core of the S1C33 Family 32-bit single chip microcomputers. Refer to the "Technical Manual" of each S1C33 Family model for details of the hardware including the on-chip peripheral circuits.

## Conventions

This manual describes data sizes and numbers as follows:

#### Data size

8 bits: Byte, B 16 bits: Half word, H 32 bits: Word, W

#### Numbers

Hexadecimal numbers: 0x0000000, 0xFF etc. Binary numbers: 0b0000, 0b1111 etc. Others are decimal numbers. However, "0b" may be omitted if the number can be distinguished as a binary number.

#### Instructions

Description of the instructions and examples uses small letters (a to z). Capital letters can be used for actual descriptions. See Section 4.1, "Symbol Meanings", for symbols used as operands of the instructions and used in the function descriptions.

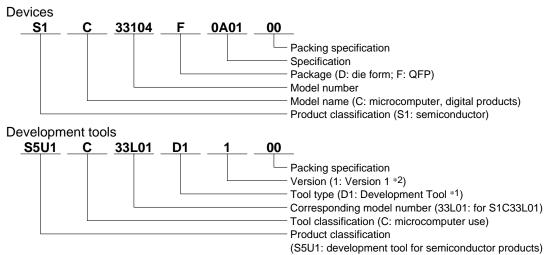

## The information of the product number change

Starting April 1, 2001, the product number will be changed as listed below. To order from April 1, 2001 please use the new product number. For further information, please contact Epson sales representative.

## Configuration of product number

\*1: For details about tool types, see the tables below. (In some manuals, tool types are represented by one digit.)

\*2: Actual versions are not written in the manuals.

#### Comparison table between | Comparison table between new and previous new and previous number number of development tools

| S1C33 Family processors |                      |     | Development too | ols for the S1C | 33 Family    |               |

|-------------------------|----------------------|-----|-----------------|-----------------|--------------|---------------|

| Previous No.            | New No.              |     | Previous No.    | New No.         | Previous No. | New No.       |

| E0C33A104               | S1C33104             |     | ICE33           | S5U1C33104H     | DMT33LIF     | S5U1C330L1D1  |

| E0C33202                | S1C33202             |     | EM33-4M         | S5U1C33104E     | DMT33SMT     | S5U1C330S1D1  |

| E0C33204                | S1C33204             |     | PRC33001        | S5U1C33104P1    | DMT33LCD26   | S5U1C330L2D1  |

| E0C33208                | S1C33208             |     | POD33001        | S5U1C33104P2    | DMT33LCD37   | S5U1C330L3D1  |

| E0C33209                | S1C33209             |     | ICD33           | S5U1C33000H     | EPOD33001    | S5U1C33208E1  |

| E0C332T01               | S1C33T01             |     | DMT33004        | S5U1C33104D1    | EPOD33001LV  | S5U1C33208E2  |

| E0C332L01               | S1C33L01             |     | DMT33004PD      | S5U1C33104D2    | EPOD33208    | S5U1C33208E3  |

| E0C332L02               | S1C33L02             |     | DMT33005        | S5U1C33208D1    | EPOD33208LV  | S5U1C33208E4  |

| E0C332S08               | S1C33S01             |     | DMT33005PD      | S5U1C33208D1    | EPOD332L01LV | S5U1C33L01E1  |

| E0C332129               | S1C33221             |     |                 |                 |              |               |

| E0C33264<br>E0C332F128  | S1C33222<br>S1C33240 |     | DMT33006LV      | S5U1C33L01D1    | EPOD332T01   | S5U1C33T01E1  |

| E0C332F126              | 51033240             |     | DMT33006PDLV    | S5U1C33L01D2    | EPOD332T01LV | S5U1C33T01E2  |

|                         |                      |     | DMT33007        | S5U1C33208D3    | EPOD33209    | S5U1C33209E1  |

| Previous No.            | New N                | •   | DMT33007PD      | S5U1C33208D4    | EPOD33209LV  | S5U1C33209E2  |

| CC33                    | S5U1C330             |     | DMT33008LV      | S5U1C33T01D1    | EPOD332128   | S5U1C33220E1  |

| CF33                    | S5U1C330             |     | DMT33008PDLV    | S5U1C33T01D2    | EPOD332128LV | S5U1C33220E2  |

| COSIM33                 | S5U1C330             |     | DMT332S08LV     | S5U1C33S01D1    | EPOD332S08LV | S5U1C33S01E1  |

| GRAPHIC33               | S5U1C330             |     | DMT332S08PDLV   | S5U1C33S01D2    | MEM33201     | S5U1C33001M1  |

| НММЗЗ                   | S5U1C330             | H1S | DMT33209LV      | S5U1C33209D1    | MEM33201LV   | S5U1C33001M2  |

| JPEG33                  | S5U1C330             | J1S | DMT33209PDLV    | S5U1C33209D2    | MEM33202     | S5U1C33002M1  |

| MON33                   | S5U1C330             | M2S | DMT332F128LV    | S5U1C33240D1    | MEM33202LV   | S5U1C33002M2  |

| MELODY33                | S5U1C330             | M1S | DMT33MON        | S5U1C330M1D1    | MEM33203     | S5U1C33003M1  |

| PEN33                   | S5U1C330             | P1S | DMT33MONLV      | S5U1C330M2D1    | MEM33203LV   | S5U1C33003M2  |

| ROS33                   | S5U1C330             | R1S | DMT33AMP        | S5U1C330A1D1    | MEM33DIP42   | S5U1C330D1M1  |

| SOUND33                 | S5U1C330             |     | DMT33AMP2       | S5U1C330A2D1    | MEM33TSOP48  | S5U1C330T1M1  |

| SMT33                   | S5U1C330             |     | DMT33AMP3       | S5U1C330A3D1    | EPOD176CABLE | S5U1C33T00E31 |

| TS33                    | S5U1C330             | -   | DMT33AMP4       | S5U1C330A3D1    | EPOD100CABLE | S5U1C33S00E31 |

| USB33                   | S5U1C330             |     | DMT33CF         | S5U1C330C1D1    | EPOD33SRAM5V | S5U1C33000S   |

| VOX33                   | S5U1C330             | -   |                 |                 |              |               |

| VRE33                   | S5U1C330             | V2S | DMT33CPLD400KLV | S5U1C330C2D1    | EPOD33SRAM3V | S5U1C33001S   |

## **CONTENTS**

| CHAPTER 1 | OUT | TLINE                                                                              | 1  |

|-----------|-----|------------------------------------------------------------------------------------|----|

|           | 1.1 | Features                                                                           | 1  |

|           | 1.2 | Block Diagram                                                                      | 2  |

|           | 1.3 | I/O Signal Specification                                                           |    |

|           |     |                                                                                    | -  |

| CHAPTER 2 | Arc | CHITECTURE                                                                         | 4  |

|           | 2.1 | Register Set                                                                       | 4  |

|           |     | 2.1.1 General-purpose registers (R0 to R15)                                        | 4  |

|           |     | 2.1.2 Program counter (PC)                                                         | 4  |

|           |     | 2.1.3 Processor status register (PSR)                                              | 5  |

|           |     | 2.1.4 Stack pointer                                                                | 6  |

|           |     | 2.1.5 Arithmetic operation register (ALR, AHR)                                     | 7  |

|           |     | 2.1.6 Register notation and register number                                        | 8  |

|           | 2.2 | Data Type                                                                          |    |

|           | 2.3 | Address Space                                                                      |    |

|           | 2.4 | Boot Address                                                                       |    |

|           | 2.5 | Instruction Set                                                                    |    |

|           | 2.5 | 2.5.1 Type of instructions                                                         |    |

|           |     | 2.5.2 Addressing mode                                                              |    |

|           |     | 2.5.2 <i>Autressing mode</i><br>2.5.3 <i>Immediate extension (EXT) instruction</i> |    |

|           |     | 2.5.4 Data transfer instructions                                                   |    |

|           |     | 2.5.5 Logic operation instructions                                                 |    |

|           |     | 2.5.6 Arithmetic operation instructions                                            |    |

|           |     | 2.5.7 Multiplication and division instructions                                     |    |

|           |     | 2.5.8 Multiplication and accumulation instruction                                  |    |

|           |     | 2.5.9 Shift and rotation instructions                                              |    |

|           |     | 2.5.10 Bit operation instructions                                                  |    |

|           |     | 2.5.11 Push and pop instructions                                                   |    |

|           |     | 2.5.12 Branch instructions and delayed instructions                                |    |

|           |     | 2.5.13 System control instructions                                                 |    |

|           |     | 2.5.14 Scan instructions                                                           |    |

|           |     | 2.5.15 Swap and mirror instructions                                                |    |

|           |     | <i>r</i>                                                                           |    |

| CHAPTER 3 | CPU | U OPERATION AND PROCESSING STATUS                                                  | 33 |

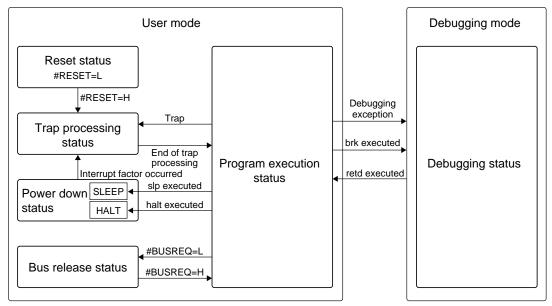

|           | 3.1 | Processing Status of CPU                                                           | 33 |

|           | 3.2 | Program Execution Status                                                           | 34 |

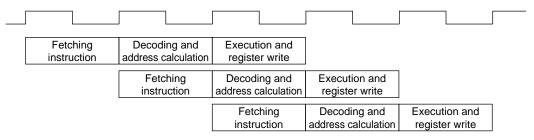

|           |     | 3.2.1 Fetching and executing program                                               | 34 |

|           |     | 3.2.2 Number of instruction execution cycles                                       | 34 |

|           | 3.3 | Trap (Interrupts and Exceptions)                                                   | 35 |

|           |     | 3.3.1 Trap table                                                                   |    |

|           |     | 3.3.2 Trap processing                                                              |    |

|           |     | 3.3.3 Reset                                                                        |    |

|           |     | 3.3.4 Zero division exception                                                      |    |

|           |     | 3.3.5 Address error exception                                                      |    |

|           |     | 3.3.6 NMI (Non-maskable interrupt)                                                 |    |

|           |     | 3.3.7 Software exception                                                           |    |

|           |     | 3.3.8 Maskable external interrupts                                                 |    |

|           |     | т                                                                                  |    |

|           | 3.4                      | Power Down Mode         40           3.4.1 HALT mode         40           3.4.2 SLEEP mode         40                                                                                                                                                                                  |    |

|-----------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|           | 3.5                      | Bus Release Status                                                                                                                                                                                                                                                                     |    |

|           | 3.6                      | Debugging Mode423.6.1 Functions of debugging mode423.6.2 Configuration of Area 2423.6.3 Transition from user mode to debugging mode433.6.4 Registers for debugging433.6.5 Traps in debugging mode453.6.6 Simultaneous occurrence of debugging exceptions45                             |    |

| CHAPTER 4 | DE                       | TAILED EXPLANATION OF INSTRUCTIONS40                                                                                                                                                                                                                                                   | 5  |

|           | <i>4.1</i><br><i>4.2</i> | Symbol Meanings       46         4.1.1 Registers       46         4.1.2 Immediate       46         4.1.3 Memories       46         4.1.4 Bits and bit fields       47         4.1.5 Flags       47         4.1.6 Functions and others       47         Instruction Code Class       48 |    |

|           |                          |                                                                                                                                                                                                                                                                                        |    |

| Appendix  | 4.3<br>S1C               | Reference for Individual Instruction                                                                                                                                                                                                                                                   | -1 |

| S1C33000 Quick Reference                    |

|---------------------------------------------|

| Memory Map and Trap Table Appendix-1        |

| RegistersAppendix-1                         |

| Symbols Appendix-2                          |

| Data Transfer Instructions Appendix-3       |

| Logic Operation Instructions Appendix-4     |

| Arithmetic Operation InstructionsAppendix-4 |

| Shift and Rotation Instructions Appendix-5  |

| Bit Operation InstructionsAppendix-5        |

| Immediate Extension InstructionAppendix-5   |

| Push and Pop InstructionsAppendix-5         |

| Branch Instructions Appendix-6              |

| Multiplication and Accumulation Instruction |

| System Control Instructions Appendix-7      |

| Other Instructions Appendix-7               |

| Immediate Extension List (1)Appendix-8      |

| Immediate Extension List (2)Appendix-9      |

| Instruction Index                           |

# CHAPTER 1 OUTLINE

The S1C33000 is a Seiko Epson original 32-bit RISC-type core CPU for the S1C33 Family microprocessors. This CPU was developed for high-performance embedded applications such as peripheral equipment for personal computers, portable equipment and other products which need high-speed data processing with low power consumption.

The S1C33000 employs pipeline processing and load-store architecture that attains a MIPS value exceeding the operating frequency. The instruction set is optimized for developing in C language, and it is possible to generate compact object codes with the C compiler. Furthermore, the S1C33000 can implement a multiplier and has a multiplication and accumulation instruction (MAC) as an option, it makes it possible to realize on-chip DSP functions.

The S1C33 Family microcomputers consist of the S1C33000 as the core and on-chip peripheral circuits such as ROM, RAM and other high-performance circuits. The S1C33000 core CPU and S1C33 Family microprocessors can realize most user demand functions in one chip.

## 1.1 Features

## CPU type:

- Seiko Epson original 32-bit RISC CPU

- 32-bit internal data processing

## **Operating frequency:**

• DC to 33 MHz (differs depending on the S1C33 Family model)

## Instruction set:

- Code size: 16 bits per instruction (fixed)

- Number of instructions: 105 instructions are available.

- Principal instructions can be executed in one cycle.

- An immediate extending instruction is available for immediate extension of instruction codes up to 32 bits.

## Multiplication and accumulation instruction:

• 64-bit multiplication and accumulation operation (MAC instruction) is available. (16 bits × 16 bits + 64 bits)

## **Register set:**

- Sixteen 32-bit general-purpose registers

- Three 32-bit special registers

- Two 32-bit arithmetic operation registers for multiplier

#### Memory space and external bus:

- A linear space including code, data and I/O areas.

- A maximum 256MB (28 bits) memory space is accessible.

- Supports 8 and 16-bit external devices.

- Can output 19 area select signals that allow to not expand any glue logic circuit.

- DRAM and other types of memories can be driven directly (differs depending on the S1C33 Family model).

- Harvard architecture

- Little endian format

#### Interrupts:

- Supports Reset, NMI and 128 external interrupts.

- Four software exceptions and two execution error exceptions.

- The CPU can directly branch the program flow to the trap handler routine by reading the vector from the trap table.

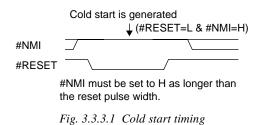

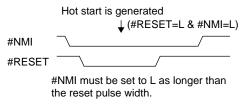

## Reset:

- Cold reset (for resetting all conditions)

- Hot reset (reset except for bus and port status)

## Power down mode:

- Halt mode (core CPU stops)

- Sleep mode (core CPU and high-speed oscillation circuit stop)

## 1.2 Block Diagram

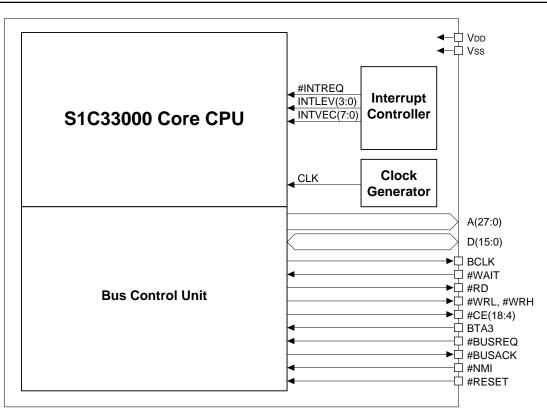

Fig. 1.2.1 S1C33000 block diagram

The diagram is an overview only for principal blocks and signals, it does not indicate the actual circuit configuration.

The actual S1C33 Family processors consist of the above blocks as the main unit and on-chip peripheral circuits.

# 1.3 I/O Signal Specification

Table 1.3.1 lists the principal input/output signals related to the operation of the S1C33000 core.

| Signal name       | I/O | Description                                                                                                  |

|-------------------|-----|--------------------------------------------------------------------------------------------------------------|

| VDD               | Ι   | Power supply + (supply voltage is different depending on the model)                                          |

| Vss               | Ι   | Power supply - (GND)                                                                                         |

| CLK               | Ι   | Input clock (clock frequency is different depending on the model)                                            |

| (Internal signal) |     |                                                                                                              |

| BCLK              | 0   | Bus clock                                                                                                    |

| DOLK              | 0   | A bus cycle clock is output.                                                                                 |

| D(15:0)           | I/O | Data bus                                                                                                     |

| D(15.0)           | 1/0 | D[15:0] is a 16-bit bidirectional data bus.                                                                  |

| A (27.0)          | 0   | Address bus                                                                                                  |

| A(27:0)           | 0   |                                                                                                              |

|                   | Ŧ   | A[27:0] is a 28-bit address bus.                                                                             |

| #WAIT             | Ι   | Wait cycle request signal                                                                                    |

|                   |     | This signal is output from low-speed devices to the CPU. The CPU extends the current bus cycle while         |

|                   |     | this signal is active and waits until the device finishes the bus operation.                                 |

| #RD               | 0   | Read signal                                                                                                  |

|                   |     | This signal is output when the CPU reads data from the data bus. The selected device outputs data to         |

|                   |     | the data bus while this signal is active.                                                                    |

| #WRL              | 0   | Write signals                                                                                                |

| #WRH              |     | This signal is output when the CPU writes data to the device connected to the data bus. The selected         |

|                   |     | device inputs data from the data bus while this signal is active.                                            |

|                   |     | #WRL is the low-order byte write signal and #WRH is the high-order byte write signal.                        |

|                   |     | The S1C33000 also supports bus strobe signals (#WR/#BSL/#BSH).                                               |

| #CE(18:4)         | 0   | Chip enable signals                                                                                          |

|                   | -   | These are chip select signals corresponding to each of the 19 memory areas and are assigned when the         |

|                   |     | CPU accesses the device of each area.                                                                        |

| #RESET            | Ι   | Initial reset signal                                                                                         |

| #RESE I           | 1   | The CPU is reset when this signal goes low level.                                                            |

|                   |     | #RESET=0 & #NMI=1: Cold reset                                                                                |

|                   |     |                                                                                                              |

| DTL 2             |     | #RESET=0 & #NMI=0: Hot reset                                                                                 |

| BTA3              | Ι   | Boot address setting signal                                                                                  |

|                   |     | Specifies a boot address.                                                                                    |

|                   |     | BTA3=1: Booting from internal ROM (Area 3).                                                                  |

|                   |     | BTA3=0: Booting from external ROM (Area 10).                                                                 |

| #NMI              | Ι   | NMI request signal                                                                                           |

|                   |     | This is the non-maskable interrupt request signal. This signal puts the CPU in trap processing status.       |

|                   |     | The signal is also used for specifying the initial reset condition.                                          |

| #INTREQ           | Ι   | Interrupt request signal                                                                                     |

| (Internal signal) |     | This is the maskable interrupt request signal from external devices to the CPU.                              |

|                   |     | Usually, the on-chip interrupt controller outputs this signal in the S1C33 Family microprocessors.           |

|                   |     | When this signal is assigned and interrupt conditions are met, the CPU goes into trap processing             |

|                   |     | status.                                                                                                      |

| INTLEV(3:0)       | Ι   | Interrupt level                                                                                              |

| (Internal signal) |     | The interrupt level of the peripheral circuit that has requested the interrupt is input. The contents of the |

| (internal signal) |     | signals are set to the IL field in the processor status register (PSR) when the CPU accepts the interrupt.   |

|                   |     | After that, interrupts that have lower levels than the set level are disabled.                               |

| INTVEC(7:0)       | I   |                                                                                                              |

|                   | 1   | Interrupt vector number                                                                                      |

| (Internal signal) |     | The vector number of the peripheral circuit that has requested the interrupt is input. The CPU reads the     |

|                   |     | specified vector from the trap table to branch the program to the interrupt service routine when the         |

| "DUGDEO           |     | CPU accepts the interrupt.                                                                                   |

| #BUSREQ           | Ι   | Bus request signal                                                                                           |

|                   | -   | This is the bus request signal output from the external bus master devices.                                  |

| #BUSACK           | 0   | Bus acknowledge signal                                                                                       |

|                   |     | Indicates that the CPU has accepted the bus request by the external bus master. The CPU changes the          |

|                   |     | bus status in high-impedance to release the bus to the external bus master while this signal is active.      |

|                   |     | The bus control returns to the CPU when the external bus master finishes the bus operation and               |

|                   |     | negates the #BUSREQ signal.                                                                                  |

# prefixed the signal names indicate that the signal is low active.

Refer to the "Technical Manual" of each S1C33 Family model for the actual input/output signals and terminals.

Table 1.3.1 S1C33000 I/O signals

# CHAPTER 2 ARCHITECTURE

# 2.1 Register Set

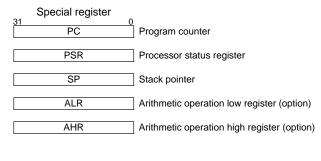

The S1C33000 has sixteen 32-bit general-purpose registers and five 32-bit special registers.

| General-purpose register |

|--------------------------|

| R15                      |

| R14                      |

| R13                      |

| R12                      |

| R11                      |

| R10                      |

| R9                       |

| R8                       |

| R7                       |

| R6                       |

| R5                       |

| R4                       |

| R3                       |

| R2                       |

| R1                       |

| R0                       |

Fig. 2.1.1 Register set

## 2.1.1 General-purpose registers (R0 to R15)

16 registers R0 to R15 are 32-bit general-purpose registers that can be used for any purpose, such as data operations, data transfers and addressing memories. The register data is always handled as a 32-bit data or an address. Data less than 32 bits is sign-expanded or zero-expanded when it is loaded to the register. When using register data as an address, the high-order 4 bits are invalidated because the address bus is 28 bit size. However, effective address size differs depending on the memory configuration of each model. The general-purpose registers must be initialized before using if necessary, because the register data is undefined at initial reset.

## 2.1.2 Program counter (PC)

The program counter (hereinafter described as the PC) is a 32-bit counter that maintains the address of the instruction being executed. In the S1C33000 instruction set, all instructions are 16-bit fixed size. Therefore, the LSB (bit 0) of the PC is always fixed at 0. Furthermore, high-order 4 bits are invalidated because the address bus is 28-bit size. However, effective address size differs depending on the memory configuration of each model.

Programs cannot directly access the PC. Only the following cases change the PC.

## (1) At initial reset

Initial reset loads the boot address to the PC and the program starts executing from the address. The boot address is stored in either 0x0080000 in the internal ROM or 0x0C00000 in the external ROM according to the BTA3 terminal setting.

## (2) When an instruction is executed

The PC is incremented (+2) every time the CPU executes an instruction and always indicates the address being executed.

## (3) When program branches

When the program branches the process flow such as a jump, subroutine call/return or trap processing for interrupts and exceptions, the CPU loads the destination address to the PC.

In subroutine calls and trap processing that need a return operation, the contents of the PC are saved in the stack and it returns to the PC when the return instruction is executed.

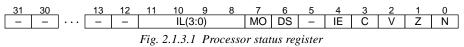

## 2.1.3 Processor status register (PSR)

The processor status register (hereinafter described as the PSR) is a 32-bit register that indicates the CPU status and the content changes according to the instruction executed. It can be read and written using the load instruction.

Since the PSR also affects program execution, when an interrupt or exception occurs, the contents of the PSR are saved into the stack before branching to the handler routine. The saved contents return to the PSR when the return (reti) instruction is executed.

At initial reset, each bit in the PSR is set to 0.

The following shows the function of each bit.

"-" indicates unused bit. Writing operation is invalid and 0 is always read.

## N (bit 0): Negative flag

Indicates a sign: positive or negative. When a logic operation, arithmetic operation or a shift instruction is executed, the MSB (bit 31) of the result (loaded in the destination register) is copied to the N flag. When a step division is executed, the sign bit of the divisor is copied to the N flag and it affects the division.

## Z (bit 1): Zero flag

Indicates that the operation result is zero. The Z flag is set to 1 when the operation result (loaded in the destination register) of a logic operation, arithmetic operation or a shift instruction is zero, and is reset to 0 when the result is not zero.

## V (bit 2): Overflow flag

Indicates that an overflow or underflow has occurred. The V flag is set to 1 when an overflow or underflow occurs due to an execution of an addition or subtraction instruction that handles the values as signed 32-bit integers. It is reset to 0 when the addition/subtraction result is within the signed 32-bit data range. The following shows the conditions that set the V flag:

- (1) The sign bit (MSB) of the result is 0 (positive) when a negative integer is added to a negative integer.

- (2) The sign bit (MSB) of the result is 1 (negative) when a positive integer is added to a positive integer.

- (3) The sign bit (MSB) of the result is 1 (negative) when a negative integer is subtracted from a positive integer.

- (4) The sign bit (MSB) of the result is 0 (positive) when a positive integer is subtracted from a negative integer.

## C (bit 3): Carry flag

Indicates a carry or a borrow. The C flag is set to 1 when the execution result of an addition or subtraction instruction that handles the values as unsigned 32-bit integers exceeds the unsigned 32-bit data range. It is reset to 0 when the addition/subtraction result is within the unsigned 32-bit data range. The following shows the conditions that set the V flag:

- (1) When an addition instruction is executed as the result will be bigger than the unsigned 32-bit maximum value 0xFFFFFFF.

- (2) When a subtraction instruction is executed as the result will be smaller than the unsigned 32-bit maximum value 0x00000000.

## IE (bit 4): Interrupt enable bit

Enables or disables accepting maskable external interrupts. When the IE bit is set to 1, the CPU can accept maskable external interrupts and when it is reset to 0 it cannot.

See Section 3.3.8, "Maskable external interrupts", for details of the IE bit.

## DS (bit 6): Dividend sign flag

The step division copies the sign bit of the dividend to the DS flag. The DS flag affects the division.

#### MO (bit 7): MAC (Multiply and accumulate) overflow flag

Indicates that an overflow has occurred due to a multiply and accumulate operation. The MO flag is set to 1 when the temporary result of the multiply and accumulate (mac) operation exceeds the effective range of the signed 64-bit data. The operation continues at the last stage regardless of the overflow, therefore the MO flag should be read after the operation has finished to decide whether the result is valid or not. When the MO flag is set to 1, it is maintained until the MO flag is reset by program or initial reset.

#### IL (bit 8 to bit 11): Interrupt level

Indicates the acceptable interrupt level of the CPU. Maskable external interrupt requests are accepted only when the interrupt level is higher than the level set in the IL field. Furthermore, when an interrupt is accepted, the IL field is set to the accepted interrupt level. After that, interrupts that have the same or lower levels than the IL field are disabled until the program changes the IL field or the interrupt handler routine is terminated with the "reti" instruction.

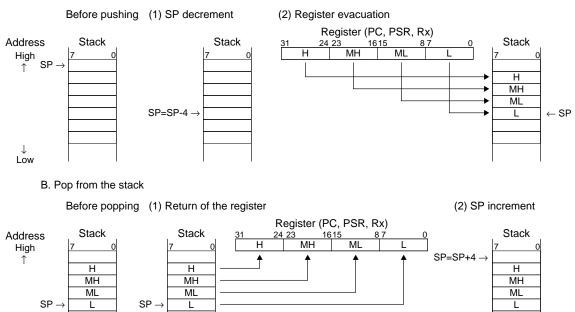

## 2.1.4 Stack pointer

The stack pointer (hereinafter described as the SP) is a 32-bit register that maintains the stack beginning address.

The stack is an area allocable anywhere in the RAM and is extended toward to the low address from the address initially set in the SP according to the data number saved (pushed). When writing (pushing) data into the stack, the SP is decremented (-4; word units) before writing data to reserve the word area for the data. When getting (popping) data from the stack, word data is retrieved from the address specified by the SP, and then the SP is incremented (+4) to release the word area.

#### A. Push to the stack

Fig. 2.1.4.2 SP and stack

6

↓ Low Data that is pushed into the stack is only 32-bit internal register data, therefore the low-order 2 bits of the SP is fixed at 0 indicating a word boundary. Furthermore the high-order 4 bits are invalidated because the address bus is 28-bit size. However, effective address size differs depending on the memory configuration of each model.

Data push and pop from/to the stack is done in the following cases:

## (1) When the call instruction is executed

"call" is the subroutine call instruction and uses 1 word from the stack area. The "call" instruction pushes the contents of the PC (return address; the next address of "call") into the stack before branching. The pushed address is loaded to the PC by the "ret" (return) instruction at the end of the subroutine and the program execution returns to the routine that called the subroutine.

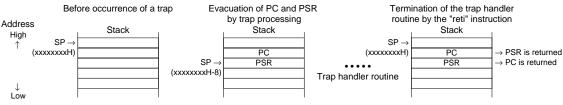

## (2) When an interrupt or exception occurs

When a trap such as an interrupt and software exception by the "int" instruction occurs, the CPU pushes the contents of the PC and the PSR into the stack before branching to the handler routine. This is because the trap processing changes these registers. The PC and PSR data is pushed into the stack as shown in Figure 2.1.4.3.

The "reti" instruction that returns the PC and PSR data should be used for return from handler routines.

Fig. 2.1.4.3 Stack operation when an interrupt or exception occurs

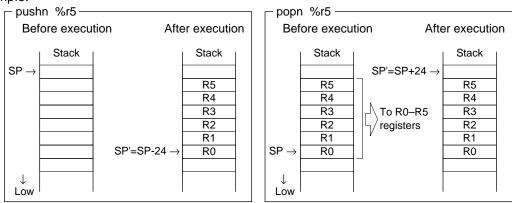

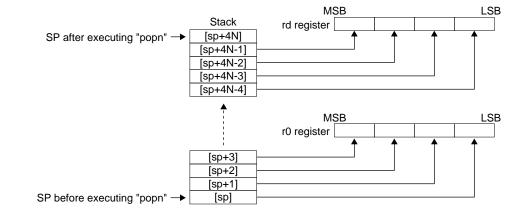

## (3) When the "pushn" or "popn" instruction is executed

The "pushn" instruction saves the contents of R0 to the specified general-purpose register. The "popn" instruction returns the saved data to each register.

The stack area size is restricted according to the RAM size and the area used for storing general data. Pay attention that both areas are not duplicated.

The SP is undefined at initial reset, therefore write an address (stack end address +4; low-order 2 bits are 0) at the head of the initial routine. The stack address can be written using the load instruction. When an interrupt or an exception occurs before setting the stack, the PC and PSR are saved to an undefined location. It cannot guarantee proper operation. Consequently, NMI that cannot be controlled by software is masked by the hardware until the SP is initialized.

## 2.1.5 Arithmetic operation register (ALR, AHR)

The arithmetic operation low register (hereinafter described as the ALR) and arithmetic operation high register (AHR) in the special registers are used for multiplication, division and multiplication and accumulation operations. These are 32-bit data registers and data can be transferred from/to general-purpose registers using the load instructions.

The multiplication instruction and the multiplication and accumulation instruction place the low-order 32 bits of the result to the ALR and the high-order 32 bits to the AHR.

The division instruction places the quotient to the ALR and the remainder to the AHR.

At initial reset, the ALR and AHR are undefined.

The ALR and the AHR can be used only in the models that have a built-in multiplier.

## 2.1.6 Register notation and register number

The following shows register notation and register numbers used in the S1C33000 instruction set. Register specification uses a 4-bit field in the instruction code. The specified register number is set in the field. In the mnemonics, "%" must be prefixed to register names.

## (1) General-purpose registers

- **%rs** rs is the metasymbol indicating a general-purpose register that contains source data for operation or transfer. Actually describe as %r0 to %r15.

- **%rd** rd is the metasymbol indicating a general-purpose register used as destination (operated or data loaded). Actually describe as %r0 to %r15.

%rb rb is the metasymbol indicating a general-purpose register that contains the base address of the memory to be accessed. In this case, the register works as an index register. Actually, enclose the register name to be specified with [] that indicate register indirect addressing like [%r0] to [%r15]. The S1C33000 allows a register indirect addressing with post increment function for sequential memory accessing. When using this function, postfix "+" like [%r0]+ to [%r15]+. In this case, the base address in the specified register is incremented according to the accessed data size after the memory has been accessed. rb is also used in the "call" and "jp" instructions and indicates a register that contains a destination address for branching. In this case, [] are not necessary, just describe as %r0 to %r15.

The register number of the general-purpose registers is the same as the number in the register name. 0 to 15 (0b0000–0b1111) enters in the register bit field of the instruction code according to the register to be specified.

## (2) Special registers

- **%ss** ss is the metasymbol indicating a special register that contains source data to be transferred to a general-purpose register. This symbol is used only in the "ld.w %rd, %ss" instruction.

- **%sd** sd is the metasymbol indicating a special register in which data is loaded from a generalpurpose register. This symbol is used only in the "ld.w %sd, %rs" instruction.

Table 2.1.6.1 shows the special register number and the actual notation.

| Special register name              | Register number |      |

|------------------------------------|-----------------|------|

| Processor status register          | 0               | %psr |

| Stack pointer                      | 1               | %sp  |

| Arithmetic operation low register  | 2               | %alr |

| Arithmetic operation high register | 3               | %ahr |

Table 2.1.6.1 Special register number and notation

0b00 enters in the high-order 2 bits of the register bit field and a register number 0-3 (0b00-0b11) enters in the low-order 2 bits.

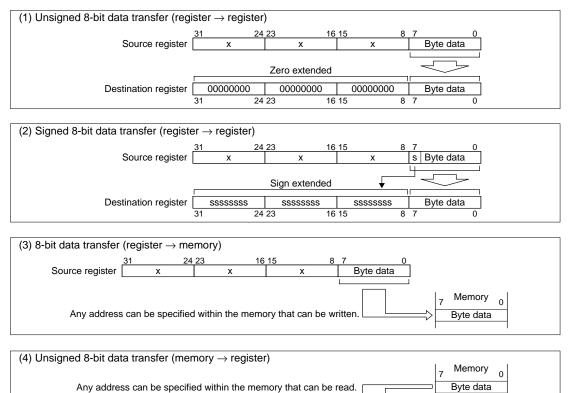

# 2.2 Data Type

The S1C33000 can handle 8-bit, 16-bit and 32-bit data. This manual describes each data size as follows:

```

8-bit data: Byte or B16-bit data: Half word or H32-bit data: Word or W

```

Note that some other manuals describe 16-bit data as Word and 32-bit data as Long word.

Data size can be selected only in data transfers (using a load instruction) between memory and a generalpurpose register and between general-purpose registers.

Processing in the CPU core is performed in 32 bits. Consequently, in 16-bit data transfer and 8-bit data transfer to a general-purpose register, the transfer data is sign-extended or zero-extended into 32 bits when it is loaded to the register. The extension type, sign or zero, is decided according to the load instruction to be used.

In 16-bit data transfer or 8-bit data transfer from a general-purpose register, the low-order half word or the low-order byte is transferred, respectively.

Memory is accessed in byte, half word or word units with the little endian method. The address to be specified must be a half word boundary address (MSB is 0) for half word data accessing, and a word boundary address (low-order 2 bits are 0) for word data accessing, otherwise an address error exception will occur.

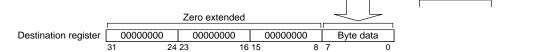

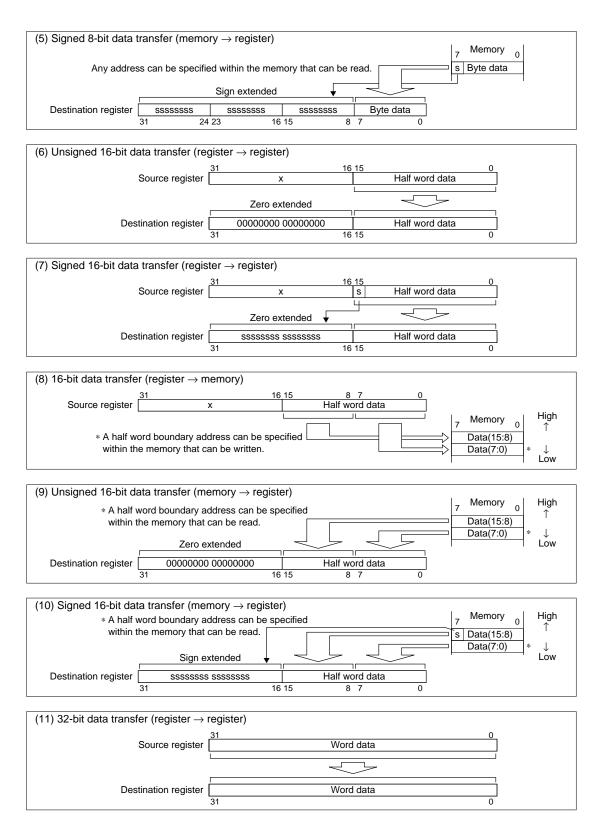

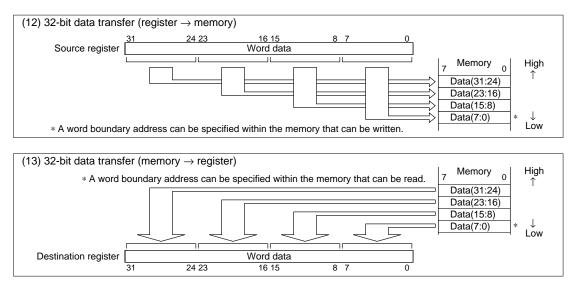

Figure 2.2.1 shows the types of data transfer.

Fig. 2.2.1 Data transfer type

# 2.3 Address Space

The S1C33000 has a 28-bit (256MB) address space.

Memories are all allocated within the space. Furthermore the S1C33000 employs a memory mapped I/O method, thus control registers of I/O modules are also allocated in this space and they can be accessed as well as general memories.

Figure 2.3.1 shows the basic memory map.

| Area No. | Address                |                             | Area size |

|----------|------------------------|-----------------------------|-----------|

| Area 18  | 0xFFFFFFF<br>0xC000000 | External memory             | 64MB      |

| Area 17  | 0xBFFFFFF              |                             | 64MB      |

| /        | 0x8000000              | External memory             | 0 1112    |

| Area 16  | 0x7FFFFFF              | E. t                        | 32MB      |

|          | 0x6000000              | External memory             |           |

| Area 15  | 0x5FFFFFF              | External memory             | 32MB      |

|          | 0x4000000              | External memory             |           |

| Area 14  | 0x3FFFFFF              | External memory             | 16MB      |

|          | 0x3000000              | External memory             |           |

| Area 13  | 0x2FFFFFF              | External memory             | 16MB      |

|          | 0x2000000              | External memory             |           |

| Area 12  | 0x1FFFFFF              | External memory             | 8MB       |

|          | 0x1800000              | External memory             |           |

| Area 11  | 0x17FFFFF              | External memory             | 8MB       |

|          | 0x1000000              | ,                           |           |

| Area 10  | 0x0FFFFFF              | External memory             | 4MB       |

| Area 9   | 0x0C00000<br>0x0BFFFFF |                             | 4MB       |

| Alea 9   | 0x0800000              | External memory             | 4IVID     |

| Area 8   | 0x0800000<br>0x07FFFFF |                             | 2MB       |

| Aleao    | 0x07FFFFF<br>0x0600000 | External memory             | ZIVID     |

| Area 7   | 0x0000000              |                             | 2MB       |

| Alea I   | 0x03FFFFF              | External memory             | 21010     |

| Area 6   | 0x03FFFFF              |                             | 1MB       |

| / 100 0  | 0x0300000              | External I/O                | me        |

| Area 5   | 0x02FFFFF              |                             | 1MB       |

|          | 0x0200000              | External memory             |           |

| Area 4   | 0x01FFFFF              |                             | 1MB       |

|          | 0x0100000              | External memory             |           |

| Area 3   | 0x00FFFFF              |                             | 512KB     |

|          | $0 \times 0080000$     | Internal ROM                |           |

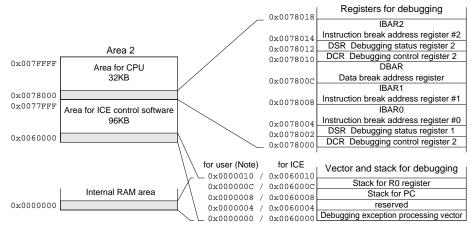

| Area 2   | 0x007FFFF              | Reserved area for ICE       | 128KB     |

|          | 0x0060000              | Reserved area for ICE       |           |

| Area 1   | 0x005FFFF              | Internal peripheral circuit | 128KB     |

|          | $0 \times 0040000$     |                             |           |

| Area 0   | 0x003FFFF              | Internal RAM                | 256KB     |

|          | $0 \times 00000000$    |                             |           |

|          | ,                      |                             |           |

Fig. 2.3.1 Memory map

As shown in the figure, the S1C33000 manages the address space by dividing it into 19 areas. The type of modules that can be connected are predefined in each area. Area 0 is for the internal RAM in the S1C33 Family, Area 1 is for internal peripheral circuits and Area 3 is for the internal ROM.

Area 10 can be used as an external ROM area including a boot address.

Area 2 is an internal area, but do not use it because Area 2 is reserved for ICE software (See Section 3.6, "Debugging Mode").

Each area for external modules can specify the device type to be used, data size and number of wait cycles. The specifiable items differ depending on the S1C33 Family model.

The S1C33000 has a built-in address decoder, it makes it possible to output 19 select signals corresponding to the 19 areas. Thus the system that follows the basic memory map does not need any external glue logic, and external devices can be directly connected.

The internal memory capacity, I/O memory size and address bus size differ depending on the S1C33 Family model. Therefore, the memory map shown in Figure 2.3.1 does not apply to all models. Refer to the "Technical Manual" of each model for the actual memory map.

## 2.4 Boot Address

In the S1C33000, the trap table location can be selected from either Area 3 (internal ROM) or Area 10 (external ROM) by the BTA3 terminal setting. The trap table begins from the head of the area and the reset vector for booting is placed at the head of the table, so the boot address is placed at the beginning address of the selected area.

| Terminal level | Area selected          | Boot address |

|----------------|------------------------|--------------|

| BTA3=1 (High)  | Area 3 (internal ROM)  | 0x0080000    |

| BTA3=0 (Low)   | Area 10 (external ROM) | 0x0C00000    |

Table 2.4.1 Boot address setting

General models of the S1C33 Family have a built-in ROM and can boot from both areas. Models that have no built-in ROM can only boot from the external ROM. Refer to the "Technical Manual" of each model for boot address settings.

# 2.5 Instruction Set

The S1C33000 instruction set contains 61 basic instructions (105 instructions in all). The instruction codes are all fixed at the 16-bit size. The CPU can execute the principal instructions in 1 cycle with pipeline processing and load-store type architecture. The instruction set has an optimized code system that can generate compact object codes even if developing in C language.

This section explains the function overview of the S1C33000 instruction set.

See Chapter 4, "Detailed Explanation of Instructions", for details of each instruction.

## 2.5.1 Type of instructions

Table 2.5.1.1 lists the instructions.

Table 2.5.1.1 Instruction list

|                                                          |               | In a man :- | Table 2.3.1.1 Instruction list                                                                                                           |                             |  |  |  |

|----------------------------------------------------------|---------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--|--|--|

| Classification                                           |               |             | Function                                                                                                                                 |                             |  |  |  |

| Logic and %rd, %rs AND between general-purpose registers |               |             | <u>`</u>                                                                                                                                 |                             |  |  |  |

| operation                                                |               | %rd, sign6  |                                                                                                                                          |                             |  |  |  |

|                                                          | or            | %rd, %rs    | OR between general-purpose registers                                                                                                     |                             |  |  |  |

|                                                          |               | %rd, sign6  | OR between general-purpose register and immediate data (with sign extension)                                                             |                             |  |  |  |

|                                                          | xor %rd, %rs  |             | XOR between general-purpose registers                                                                                                    |                             |  |  |  |

|                                                          |               | %rd, sign6  | XOR between general-purpose register and immediate data (with sign extension)                                                            | )                           |  |  |  |

|                                                          | not           | %rd, %rs    | NOT for general-purpose registers                                                                                                        |                             |  |  |  |

|                                                          |               | %rd, sign6  | NOT for immediate data (with sign extension)                                                                                             |                             |  |  |  |

| Arithmetic                                               | add           | %rd, %rs    | Addition between general-purpose registers                                                                                               |                             |  |  |  |

| operation                                                |               | %rd, imm6   | Addition of immediate data to general-purpose registers (with zero extension)                                                            |                             |  |  |  |

|                                                          |               | %sp, imm10  | Addition of immediate data to SP (with zero extension)                                                                                   |                             |  |  |  |

|                                                          | adc           | %rd, %rs    | Addition with carry between general-purpose registers                                                                                    |                             |  |  |  |

|                                                          | sub           | %rd, %rs    | Subtraction between general-purpose registers                                                                                            |                             |  |  |  |

|                                                          |               | %rd, imm6   | Subtraction of immediate data from general-purpose register (with zero extensio                                                          | n)                          |  |  |  |

|                                                          |               | %sp, imm10  | Subtraction of immediate data from SP (with zero extension)                                                                              |                             |  |  |  |

|                                                          | sbc           | %rd, %rs    | Subtraction with borrow between general-purpose registers                                                                                |                             |  |  |  |

|                                                          | cmp           | %rd, %rs    | Comparison between general-purpose registers                                                                                             |                             |  |  |  |

|                                                          |               | %rd, sign6  | Comparison between general-purpose register and immediate data (with sign ext                                                            | ension)                     |  |  |  |

|                                                          | mlt.h         | %rd, %rs    | Multiplication for signed integers (16 bits $\times$ 16 bits = 32 bits)                                                                  | <option:< td=""></option:<> |  |  |  |

|                                                          | mltu.h        | %rd, %rs    | Multiplication for unsigned integers (16 bits $\times$ 16 bits $=$ 32 bits)                                                              | <option:< td=""></option:<> |  |  |  |

|                                                          | mlt.w         | %rd, %rs    | Multiplication for signed integers ( $32 \text{ bits} \times 32 \text{ bits} = 64 \text{ bits}$ )                                        | <option:< td=""></option:<> |  |  |  |

|                                                          | mltu.w        | %rd, %rs    | Multiplication for unsigned integers (32 bits × 32 bits = 64 bits)<br>Multiplication for unsigned integers (32 bits × 32 bits = 64 bits) | <option:< td=""></option:<> |  |  |  |

|                                                          | div0s         | %rs         | Signed division 1st step                                                                                                                 | <option:< td=""></option:<> |  |  |  |

|                                                          | div0u         | %rs         | Unsigned division 1st step                                                                                                               | <option:< td=""></option:<> |  |  |  |

|                                                          | div1          | %rs         | Step division execution                                                                                                                  | <option:< td=""></option:<> |  |  |  |

|                                                          | div1<br>div2s | %rs         | Data correction 1 for signed division result                                                                                             | •                           |  |  |  |

|                                                          |               | %15         | e                                                                                                                                        | <option></option>           |  |  |  |

| C1.:C                                                    | div3s         | 0/1 0/      | Data correction 2 for signed division result                                                                                             | <option></option>           |  |  |  |

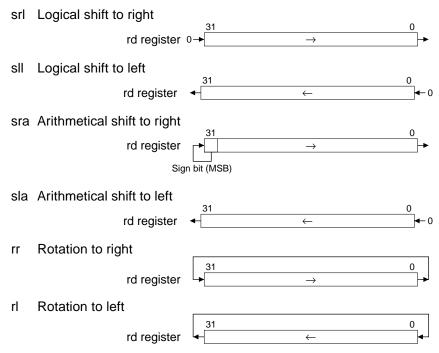

| Shift                                                    | srl           | %rd, %rs    | Logical shift to right (shift count is specified with register)                                                                          |                             |  |  |  |

| & Rotate                                                 | 11            | %rd, imm4   | Logical shift to right (shift count is specified with immediate data)                                                                    |                             |  |  |  |

|                                                          | sll           | %rd, %rs    | Logical shift to left (shift count is specified with register)                                                                           |                             |  |  |  |

|                                                          |               | %rd, imm4   | Logical shift to left (shift count is specified with immediate data)                                                                     |                             |  |  |  |

|                                                          | sra           | %rd, %rs    | Arithmetic shift to right (shift count is specified with register)                                                                       |                             |  |  |  |

|                                                          |               | %rd, imm4   | Arithmetic shift to right (shift count is specified with immediate data)                                                                 |                             |  |  |  |

|                                                          | sla           | %rd, %rs    | Arithmetic shift to left (shift count is specified with register)                                                                        |                             |  |  |  |

|                                                          |               | %rd, imm4   | Arithmetic shift to left (shift count is specified with immediate data)                                                                  |                             |  |  |  |

|                                                          | rr            | %rd, %rs    | Rotation to right (shift count is specified with register)                                                                               |                             |  |  |  |

|                                                          |               | %rd, imm4   | Rotation to right (shift count is specified with immediate data)                                                                         |                             |  |  |  |

|                                                          | rl            | %rd, %rs    | Rotation to left (shift count is specified with register)                                                                                |                             |  |  |  |

|                                                          |               | %rd, imm4   | Rotation to left (shift count is specified with immediate data)                                                                          |                             |  |  |  |

| Branch                                                   | jrgt          | sign8       | PC relative conditional jump; Branch condition: !Z & !(N ^ V)                                                                            |                             |  |  |  |

|                                                          | jrgt.d        |             | (".d" allows delayed branch.)                                                                                                            |                             |  |  |  |

|                                                          | jrge          | sign8       | PC relative conditional jump; Branch condition: !(N ^ V)                                                                                 |                             |  |  |  |

|                                                          | jrge.d        | 0           | (".d" allows delayed branch.)                                                                                                            |                             |  |  |  |

|                                                          | jrlt          | sign8       | PC relative conditional jump; Branch condition: N ^ V                                                                                    |                             |  |  |  |

|                                                          | jrlt.d        |             | (".d" allows delayed branch.)                                                                                                            |                             |  |  |  |

|                                                          | jrle          | sign8       | PC relative conditional jump; Branch condition: Z   N ^ V                                                                                |                             |  |  |  |

|                                                          | jrle.d        | 0           | (".d" allows delayed branch.)                                                                                                            |                             |  |  |  |

|                                                          | jrugt         | sign8       | PC relative conditional jump; Branch condition: !Z & !C                                                                                  |                             |  |  |  |

|                                                          | jrugt.d       | 515110      | (".d" allows delayed branch.)                                                                                                            |                             |  |  |  |

|                                                          |               | sign8       | PC relative conditional jump; Branch condition: !C                                                                                       |                             |  |  |  |

|                                                          | jruge         | sign8       | 5 1                                                                                                                                      |                             |  |  |  |

|                                                          | jruge.d       |             | (".d" allows delayed branch.)                                                                                                            |                             |  |  |  |

| Classification |                                                 | Mnemonic                                                           | Function                                                                                                                                                                                                                                                                                                                 |

|----------------|-------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Branch         | jrult                                           | sign8                                                              | PC relative conditional jump; Branch condition: C                                                                                                                                                                                                                                                                        |

|                | jrult.d                                         | 0                                                                  | (".d" allows delayed branch.)                                                                                                                                                                                                                                                                                            |

|                | jrule                                           | sign8                                                              | PC relative conditional jump; Branch condition: Z   C                                                                                                                                                                                                                                                                    |

|                | jrule.d                                         | Signo                                                              | (".d" allows delayed branch.)                                                                                                                                                                                                                                                                                            |

|                | jreq                                            | sign8                                                              | PC relative conditional jump; Branch condition: Z                                                                                                                                                                                                                                                                        |

|                | jreq.d                                          | 315110                                                             | (".d" allows delayed branch.)                                                                                                                                                                                                                                                                                            |

|                | jrne                                            | sign8                                                              | PC relative conditional jump; Branch condition: !Z                                                                                                                                                                                                                                                                       |

|                | jrne.d                                          | signo                                                              | (".d" allows delayed branch.)                                                                                                                                                                                                                                                                                            |

|                | jp                                              | sign8                                                              | PC relative jump (".d" allows delayed branch.)                                                                                                                                                                                                                                                                           |

|                | jp.d                                            | %rb                                                                | Absolute jump (".d" allows delayed branch.)                                                                                                                                                                                                                                                                              |

|                | call                                            | sign8                                                              | PC relative call (".d" allows delayed branch.)                                                                                                                                                                                                                                                                           |

|                | call.d                                          | %rb                                                                | Absolute call (".d" allows delayed branch.)                                                                                                                                                                                                                                                                              |

|                | ret                                             | /010                                                               | Return from subroutine                                                                                                                                                                                                                                                                                                   |

|                | ret.d                                           |                                                                    | (".d" allows delayed branch.)                                                                                                                                                                                                                                                                                            |

|                | reti                                            |                                                                    | Return from interrupt/exception handler routine                                                                                                                                                                                                                                                                          |

|                | retd                                            |                                                                    | Return from debugging routine                                                                                                                                                                                                                                                                                            |

|                | int                                             | imm2                                                               | Software exception                                                                                                                                                                                                                                                                                                       |

|                | brk                                             | 1111112                                                            | Debugging exception                                                                                                                                                                                                                                                                                                      |

| Data           | ld.b                                            | %rd, %rs                                                           | General-purpose register (byte) $\rightarrow$ General-purpose register (with sign extension)                                                                                                                                                                                                                             |

|                | 10.0                                            |                                                                    | $Memory (byte) \rightarrow General-purpose register (with sign extension)$                                                                                                                                                                                                                                               |

| transfer       |                                                 | %rd, [%rb]                                                         | "+" is specification for address post-increment function.                                                                                                                                                                                                                                                                |

|                |                                                 | %rd, [%rb]+<br>%rd,[%sp+imm6]                                      | $^{++}$ is specification for address post-increment function.<br>Stack (byte) $\rightarrow$ General-purpose register (with sign extension)                                                                                                                                                                               |

|                |                                                 |                                                                    |                                                                                                                                                                                                                                                                                                                          |

|                |                                                 | [%rb], %rs                                                         | General-purpose register (byte) $\rightarrow$ Memory                                                                                                                                                                                                                                                                     |

|                |                                                 | [%rb]+, %rs                                                        | "+" is specification for address post-increment function.                                                                                                                                                                                                                                                                |

|                | 11 1                                            | [%sp+imm6],%rs                                                     | General-purpose register (byte) $\rightarrow$ Stack                                                                                                                                                                                                                                                                      |

|                | ld.ub                                           | %rd, %rs                                                           | General-purpose register (byte) $\rightarrow$ General-purpose register (with zero extension)                                                                                                                                                                                                                             |