# **CMOS 4-BIT SINGLE CHIP MICROCOMPUTER** S1C60N08/60R08 Technical Manual S1C60N08 Technical Hardware/S1C60R08 Technical Hardware

## S1C60N08/S1C60R08 Technical Manual

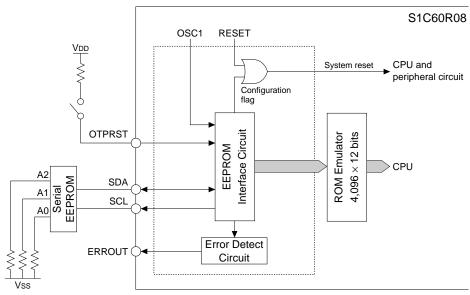

This publication consists of two manuals that explain the hardware specifications of the S1C60N08 and S1C60R08 (ROM emulator model for S1C60N08) CMOS 4-bit single chip microcomputers.

#### I. S1C60N08 Technical Hardware

This manual describes the functions, circuit configuration and control method of the S1C60N08.

#### II. S1C60R08 Technical Hardware

This manual describes the hardware specifications of the S1C60R08 except where the functions are the same as the S1C60N08.

#### The information of the product number change

Starting April 1, 2001, the product number will be changed as listed below. To order from April 1, 2001 please use the new product number. For further information, please contact Epson sales representative.

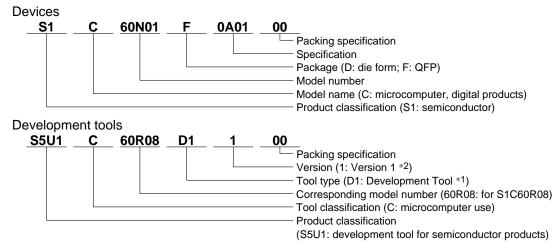

### Configuration of product number

<sup>\*1:</sup> For details about tool types, see the tables below. (In some manuals, tool types are represented by one digit.)

### Comparison table between new and previous number

S1C60 Family processors

| <u> </u>     | ·        |

|--------------|----------|

| Previous No. | New No.  |

| E0C6001      | S1C60N01 |

| E0C6002      | S1C60N02 |

| E0C6003      | S1C60N03 |

| E0C6004      | S1C60N04 |

| E0C6005      | S1C60N05 |

| E0C6006      | S1C60N06 |

| E0C6007      | S1C60N07 |

| E0C6008      | S1C60N08 |

| E0C6009      | S1C60N09 |

| E0C6011      | S1C60N11 |

| E0C6013      | S1C60N13 |

| E0C6014      | S1C60140 |

| E0C60R08     | S1C60R08 |

#### S1C62 Family processors

| Previous No. | New No.  | Previous No. | New No.  |

|--------------|----------|--------------|----------|

| E0C621A      | S1C621A0 | E0C6247      | S1C62470 |

| E0C6215      | S1C62150 | E0C6248      | S1C62480 |

| E0C621C      | S1C621C0 | E0C6S48      | S1C6S480 |

| E0C6S27      | S1C6S2N7 | E0C624C      | S1C624C0 |

| E0C6S37      | S1C6S3N7 | E0C6251      | S1C62N51 |

| E0C623A      | S1C6N3A0 | E0C6256      | S1C62560 |

| E0C623E      | S1C6N3E0 | E0C6292      | S1C62920 |

| E0C6S32      | S1C6S3N2 | E0C6262      | S1C62N62 |

| E0C6233      | S1C62N33 | E0C6266      | S1C62660 |

| E0C6235      | S1C62N35 | E0C6274      | S1C62740 |

| E0C623B      | S1C6N3B0 | E0C6281      | S1C62N81 |

| E0C6244      | S1C62440 | E0C6282      | S1C62N82 |

| E0C624A      | S1C624A0 | E0C62M2      | S1C62M20 |

| E0C6S46      | S1C6S460 | E0C62T3      | S1C62T30 |

## Comparison table between new and previous number of development tools

Development tools for the S1C60/62 Family

| Previous No. | New No.     | Previous No. | New No.      |  |

|--------------|-------------|--------------|--------------|--|

| ASM62        | S5U1C62000A | DEV6262      | S5U1C62620D  |  |

| DEV6001      | S5U1C60N01D | DEV6266      | S5U1C62660D  |  |

| DEV6002      | S5U1C60N02D | DEV6274      | S5U1C62740D  |  |

| DEV6003      | S5U1C60N03D | DEV6292      | S5U1C62920D  |  |

| DEV6004      | S5U1C60N04D | DEV62M2      | S5U1C62M20D  |  |

| DEV6005      | S5U1C60N05D | DEV6233      | S5U1C62N33D  |  |

| DEV6006      | S5U1C60N06D | DEV6235      | S5U1C62N35D  |  |

| DEV6007      | S5U1C60N07D | DEV6251      | S5U1C62N51D  |  |

| DEV6008      | S5U1C60N08D | DEV6256      | S5U1C62560D  |  |

| DEV6009      | S5U1C60N09D | DEV6281      | S5U1C62N81D  |  |

| DEV6011      | S5U1C60N11D | DEV6282      | S5U1C62N82D  |  |

| DEV60R08     | S5U1C60R08D | DEV6S27      | S5U1C6S2N7D  |  |

| DEV621A      | S5U1C621A0D | DEV6S32      | S5U1C6S3N2D  |  |

| DEV621C      | S5U1C621C0D | DEV6S37      | S5U1C6S3N7D  |  |

| DEV623B      | S5U1C623B0D | EVA6008      | S5U1C60N08E  |  |

| DEV6244      | S5U1C62440D | EVA6011      | S5U1C60N11E  |  |

| DEV624A      | S5U1C624A0D | EVA621AR     | S5U1C621A0E2 |  |

| DEV624C      | S5U1C624C0D | EVA621C      | S5U1C621C0E  |  |

| DEV6248      | S5U1C62480D | EVA6237      | S5U1C62N37E  |  |

| DEV6247      | S5U1C62470D | EVA623A      | S5U1C623A0E  |  |

| Previous No.         New No.           EVA623B         S5U1C623B0E           EVA623F         S5U1C623B0E           EVA6247         S5U1C62470E           EVA6248         S5U1C62480E           EVA6256R         S5U1C62N51E1           EVA6256S         S5U1C62N56E           EVA6262S         S5U1C6260E           EVA6274S         S5U1C62740E           EVA6281S         S5U1C62N81E           EVA6282S         S5U1C62N82E           EVA6281S         S5U1C62N82E           EVA6281S         S5U1C62N82E           EVA6281S         S5U1C62N82E           EVA627S         S5U1C62N30E           EVA6S27S         S5U1C63N2E2           EVA6S32RS         S5U1C63N2E2           ICE62RS         S5U1C62000H           KIT6003S         S5U1C60N03K           KIT6004S         S5U1C60N07K |              |              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|

| EVA623E S5U1C623E0E EVA6247 S5U1C62470E EVA6248 S5U1C62480E EVA6251R S5U1C62N51E1 EVA6256 S5U1C62050E EVA6262 S5U1C62600E EVA6274 S5U1C62740E EVA6281 S5U1C62740E EVA6282 S5U1C62N81E EVA6281 S5U1C62N81E EVA6281 S5U1C62N82E EVA62M1 S5U1C62N10E EVA6273 S5U1C62N30E EVA6273 S5U1C63N7E EVA6827 S5U1C6S3N7E EVA6832R S5U1C6S3N2E2 ICE62R S5U1C60N03K KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                    | Previous No. | New No.      |

| EVA6247 S5U1C62470E EVA6248 S5U1C62480E EVA6251R S5U1C62N51E1 EVA6256 S5U1C62N56E EVA6262 S5U1C62600E EVA6264 S5U1C62600E EVA6264 S5U1C62740E EVA6281 S5U1C62N81E EVA6282 S5U1C62N81E EVA6281 S5U1C62N81E EVA6281 S5U1C62N81E EVA6282 S5U1C62N81E EVA6283 S5U1C62N81E EVA62T3 S5U1C62N10E EVA62T3 S5U1C6SN7E EVA6S32R S5U1C6SN2E2 ICE62R S5U1C60N03K KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                     | EVA623B      | S5U1C623B0E  |

| EVA6248 S5U1C62480E EVA6251R S5U1C62N51E1 EVA6256 S5U1C62N56E EVA6262 S5U1C62600E EVA6266 S5U1C62600E EVA6274 S5U1C62740E EVA6281 S5U1C62N81E EVA6282 S5U1C62N81E EVA6281 S5U1C62N81E EVA6287 S5U1C62N80E EVA6273 S5U1C62N10E EVA6273 S5U1C6SN7E EVA6S32R S5U1C6SN7E EVA6S32R S5U1C6SN0E2 KIT6003 S5U1C60N03K KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                            | EVA623E      | S5U1C623E0E  |

| EVA6251R S5U1C62N51E1 EVA6256 S5U1C62N56E EVA6262 S5U1C62620E EVA6266 S5U1C6260E EVA6274 S5U1C62740E EVA6281 S5U1C62N81E EVA6282 S5U1C62N81E EVA6281 S5U1C62N81E EVA6287 S5U1C62N82E EVA62M1 S5U1C62T30E EVA62T3 S5U1C6S2N72 EVA6S32R S5U1C6SN2E2 ICE62R S5U1C60N03K KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | EVA6247      | S5U1C62470E  |

| EVA6256 S5U1C62N56E<br>EVA6262 S5U1C62620E<br>EVA6266 S5U1C62660E<br>EVA6274 S5U1C62740E<br>EVA6281 S5U1C62N81E<br>EVA6282 S5U1C62N82E<br>EVA62M1 S5U1C62M10E<br>EVA62T3 S5U1C62T30E<br>EVA6S27 S5U1C63N2E2<br>EVA6S32R S5U1C6S3N2E2<br>ICE62R S5U1C62000H<br>KIT6003 S5U1C60N03K<br>KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | EVA6248      | S5U1C62480E  |

| EVA6262 S5U1C62620E<br>EVA6266 S5U1C62660E<br>EVA6274 S5U1C62740E<br>EVA6281 S5U1C62N81E<br>EVA6282 S5U1C62N82E<br>EVA62M1 S5U1C62M10E<br>EVA62T3 S5U1C62T30E<br>EVA6S27 S5U1C6S2N7E<br>EVA6S32R S5U1C6S3N2E2<br>ICE62R S5U1C62000H<br>KIT6003 S5U1C60N03K<br>KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | EVA6251R     | S5U1C62N51E1 |

| EVA6266 S5U1C62660E<br>EVA6274 S5U1C62740E<br>EVA6281 S5U1C62N81E<br>EVA6282 S5U1C62N82E<br>EVA62M1 S5U1C62M10E<br>EVA62T3 S5U1C62T30E<br>EVA6S27 S5U1C6S2N7E<br>EVA6S32R S5U1C6S3N2E2<br>ICE62R S5U1C62000H<br>KIT6003 S5U1C60N03K<br>KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | EVA6256      | S5U1C62N56E  |

| EVA6274 S5U1C62740E<br>EVA6281 S5U1C62N81E<br>EVA6282 S5U1C62N82E<br>EVA62M1 S5U1C62M10E<br>EVA62T3 S5U1C62T30E<br>EVA6S27 S5U1C6S2N7E<br>EVA6S32R S5U1C6S3N2E2<br>ICE62R S5U1C6C900H<br>KIT6003 S5U1C60N03K<br>KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | EVA6262      | S5U1C62620E  |

| EVA6281 S5U1C62N81E<br>EVA6282 S5U1C62N82E<br>EVA62M1 S5U1C62M10E<br>EVA62T3 S5U1C62T30E<br>EVA6S227 S5U1C6S2N7E<br>EVA6S32R S5U1C6S3N2E2<br>ICE62R S5U1C6C000H<br>KIT6003 S5U1C60N03K<br>KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | EVA6266      | S5U1C62660E  |

| EVA6282 S5U1C62N82E<br>EVA62M1 S5U1C62M10E<br>EVA62T3 S5U1C62T30E<br>EVA6S227 S5U1C6S2N7E<br>EVA6S32R S5U1C6S3N2E2<br>ICE62R S5U1C6C2000H<br>KIT6003 S5U1C60N03K<br>KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | EVA6274      | S5U1C62740E  |

| EVA62M1 S5U1C62M10E<br>EVA62T3 S5U1C62T30E<br>EVA6S27 S5U1C6S2N7E<br>EVA6S32R S5U1C6S3N2E2<br>ICE62R S5U1C62000H<br>KIT6003 S5U1C60N03K<br>KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | EVA6281      | S5U1C62N81E  |

| EVA62T3 S5U1C62T30E<br>EVA6S27 S5U1C6S2N7E<br>EVA6S32R S5U1C6S3N2E2<br>ICE62R S5U1C62000H<br>KIT6003 S5U1C60N03K<br>KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | EVA6282      | S5U1C62N82E  |

| EVA6S27 S5U1C6S2N7E<br>EVA6S32R S5U1C6S3N2E2<br>ICE62R S5U1C62000H<br>KIT6003 S5U1C60N03K<br>KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | EVA62M1      | S5U1C62M10E  |

| EVA6S32R S5U1C6S3N2E2<br>ICE62R S5U1C62000H<br>KIT6003 S5U1C60N03K<br>KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | EVA62T3      | S5U1C62T30E  |

| ICE62R S5U1C62000H<br>KIT6003 S5U1C60N03K<br>KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | EVA6S27      | S5U1C6S2N7E  |

| KIT6003 S5U1C60N03K<br>KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | EVA6S32R     | S5U1C6S3N2E2 |

| KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ICE62R       | S5U1C62000H  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | KIT6003      | S5U1C60N03K  |

| KIT6007 S5U1C60N07K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | KIT6004      | S5U1C60N04K  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | KIT6007      | S5U1C60N07K  |

<sup>\*2:</sup> Actual versions are not written in the manuals.

| I. S1C60N08 Technical Hardware |

|--------------------------------|

|                                |

## **CONTENTS**

| CHAPTER 1 | <b>O</b> vi              | ERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | I-1                                                      |

|-----------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|           | 1.1                      | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                          |

|           | 1.2                      | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <i>I-1</i>                                               |

|           | 1.3                      | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <i>I-2</i>                                               |

|           | 1.4                      | Pin Layout Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                          |

|           | 1.5                      | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |

|           | 1.6                      | S1C60N08 Option List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                          |

| CHAPTER 2 | Por                      | WER SUPPLY AND INITIAL RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <i>I-7</i>                                               |

| cmm tex 2 | 2.1                      | Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          |

|           |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |

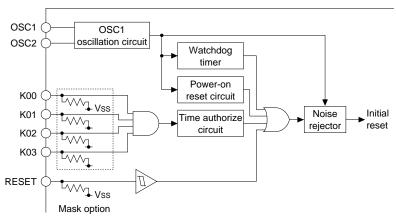

|           | 2.2                      | Initial Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                          |

|           |                          | 2.2.2 RESET terminal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                          |

|           |                          | 2.2.3 Simultaneous high input to input ports (K00–K03)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                          |

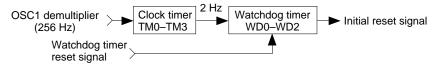

|           |                          | 2.2.4 Watchdog timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                          |

|           |                          | 2.2.5 Internal register at initial reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I-10                                                     |

|           | 2.3                      | Test Terminal (TEST)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I-10                                                     |

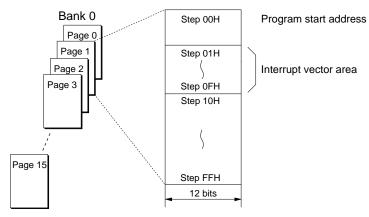

| CHAPTER 3 | CP                       | U, ROM, RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <i>I-11</i>                                              |

|           | 3.1                      | CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                          |

|           | 3.2                      | ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                          |

|           | 3.3                      | RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                          |

|           |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |

|           |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |

| CHAPTER 4 | PEF                      | RIPHERAL CIRCUITS AND OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |

| CHAPTER 4 | <b>P</b> EF 4.1          | RIPHERAL CIRCUITS AND OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I-12                                                     |

| CHAPTER 4 |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |

| CHAPTER 4 | 4.1                      | Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                          |

| CHAPTER 4 | 4.1                      | Memory MapResetting Watchdog Timer4.2.1 Configuration of watchdog timer4.2.2 Mask option                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                          |

| CHAPTER 4 | 4.1                      | Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | I-121-121-161-161-16                                     |

| CHAPTER 4 | <i>4.1</i><br><i>4.2</i> | Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | I-12 I-12 I-16 I-16 I-16 I-16 I-16                       |

| CHAPTER 4 | 4.1                      | Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | I-121-121-161-161-161-161-161-16                         |

| CHAPTER 4 | <i>4.1</i><br><i>4.2</i> | Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | I-121-121-161-161-161-161-161-17                         |

| CHAPTER 4 | <i>4.1</i><br><i>4.2</i> | Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | I-121-161-161-161-161-161-171-17                         |

| CHAPTER 4 | <i>4.1</i><br><i>4.2</i> | Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | I-121-161-161-161-161-171-171-17                         |

| CHAPTER 4 | <i>4.1</i><br><i>4.2</i> | Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | I-121-121-161-161-161-171-171-181-19                     |

| CHAPTER 4 | <i>4.1</i><br><i>4.2</i> | Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | I-121-121-161-161-161-171-171-171-181-19                 |

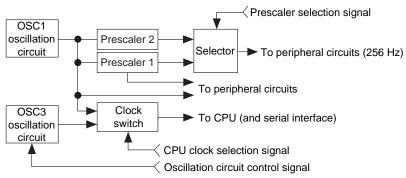

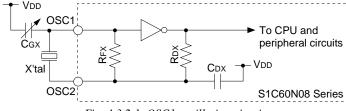

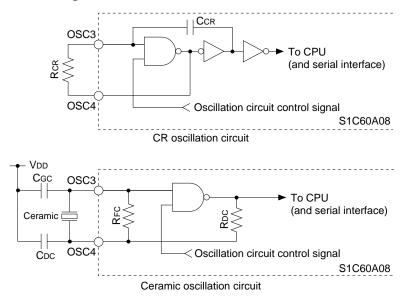

| CHAPTER 4 | 4.1<br>4.2<br>4.3        | Memory Map  Resetting Watchdog Timer  4.2.1 Configuration of watchdog timer  4.2.2 Mask option  4.2.3 Control of watchdog timer  4.2.4 Programming note  Oscillation Circuit and Prescaler  4.3.1 Configuration of oscillation circuit and prescaler  4.3.2 OSC1 oscillation circuit  4.3.3 OSC3 oscillation circuit  4.3.4 Control of oscillation circuit and prescaler  4.3.5 Programming notes  Input Ports (K00–K03, K10, K20–K23)                                                                                                                                               | I-121-121-161-161-161-171-171-171-191-201-21             |

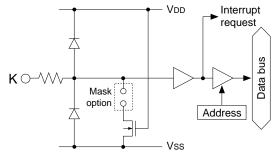

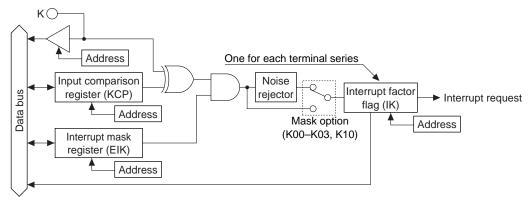

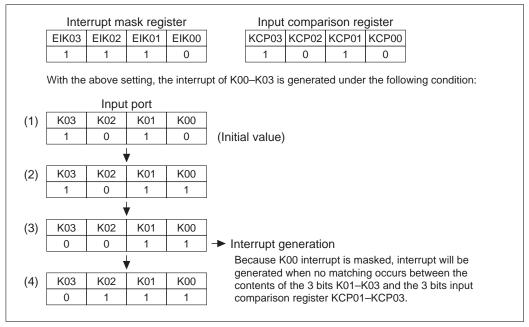

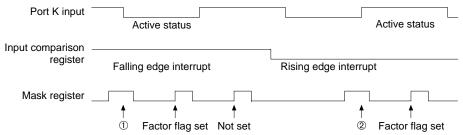

| CHAPTER 4 | 4.1<br>4.2<br>4.3        | Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | I-121-121-161-161-161-171-171-171-181-191-201-21         |

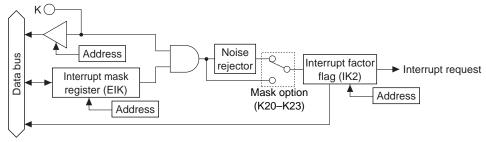

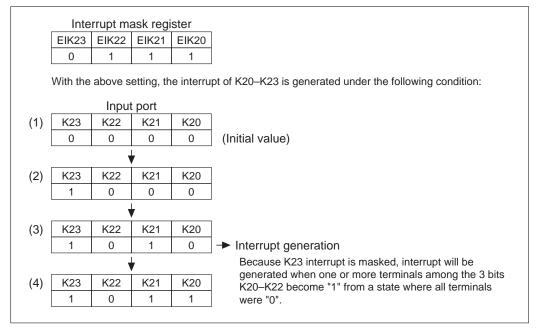

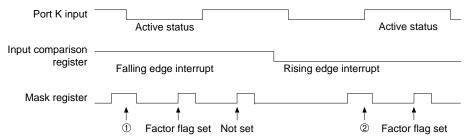

| CHAPTER 4 | 4.1<br>4.2<br>4.3        | Memory Map  Resetting Watchdog Timer  4.2.1 Configuration of watchdog timer  4.2.2 Mask option  4.2.3 Control of watchdog timer  4.2.4 Programming note  Oscillation Circuit and Prescaler  4.3.1 Configuration of oscillation circuit and prescaler  4.3.2 OSC1 oscillation circuit  4.3.3 OSC3 oscillation circuit  4.3.4 Control of oscillation circuit and prescaler  4.3.5 Programming notes  Input Ports (K00–K03, K10, K20–K23)  4.4.1 Configuration of input ports  4.4.2 Input comparison registers and interrupt function  4.4.3 Mask option                               | I-121-121-161-161-161-171-171-171-181-191-201-211-211-21 |

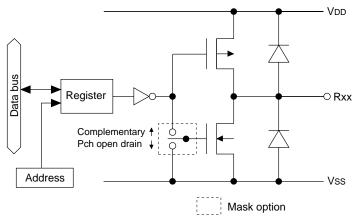

| CHAPTER 4 | 4.1<br>4.2<br>4.3        | Memory Map  Resetting Watchdog Timer  4.2.1 Configuration of watchdog timer  4.2.2 Mask option  4.2.3 Control of watchdog timer  4.2.4 Programming note  Oscillation Circuit and Prescaler  4.3.1 Configuration of oscillation circuit and prescaler  4.3.2 OSC1 oscillation circuit  4.3.3 OSC3 oscillation circuit  4.3.4 Control of oscillation circuit and prescaler  4.3.5 Programming notes  Input Ports (K00–K03, K10, K20–K23)  4.4.1 Configuration of input ports  4.4.2 Input comparison registers and interrupt function  4.4.3 Mask option  4.4.4 Control of input ports | I-12                                                     |

| CHAPTER 4 | 4.1<br>4.2<br>4.3        | Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | I-12                                                     |

| CHAPTER 4 | 4.1<br>4.2<br>4.3        | Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | I-12                                                     |

| CHAPTER 4 | 4.1<br>4.2<br>4.3        | Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | I-12                                                     |

| CHAPTER 4 | 4.1<br>4.2<br>4.3        | Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | I-12                                                     |

| CHAPTER 4 | 4.1<br>4.2<br>4.3        | Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | I-12                                                     |

| 4.6  | I/O Ports (P00–P03, P10–P13)                         | I-31        |

|------|------------------------------------------------------|-------------|

| 7.0  | 4.6.1 Configuration of I/O ports                     |             |

|      |                                                      |             |

|      | 4.6.2 I/O control register and I/O mode              |             |

|      | 4.6.3 Mask option                                    |             |

|      | 4.6.4 Control of I/O ports                           |             |

|      | 4.6.5 Programming notes                              | . I-33      |

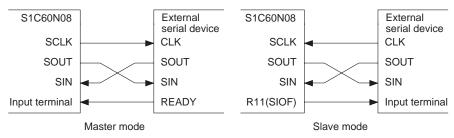

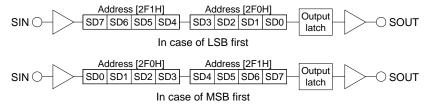

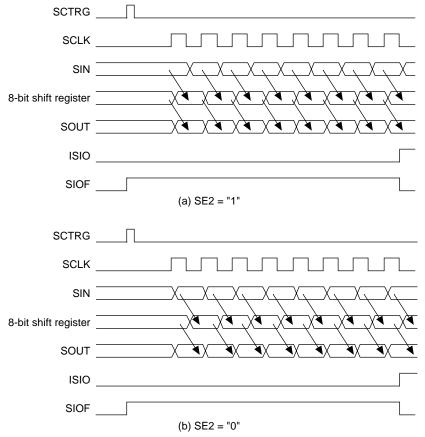

| 4.7  | Serial Interface (SIN, SOUT, SCLK)                   | I-34        |

| ,    | 4.7.1 Configuration of serial interface              |             |

|      | 4.7.2 Master mode and slave mode of serial interface |             |

|      |                                                      |             |

|      | 4.7.3 Data input/output and interrupt function       |             |

|      | 4.7.4 Mask option                                    |             |

|      | 4.7.5 Control of serial interface                    |             |

|      | 4.7.6 Programming notes                              | . I-40      |

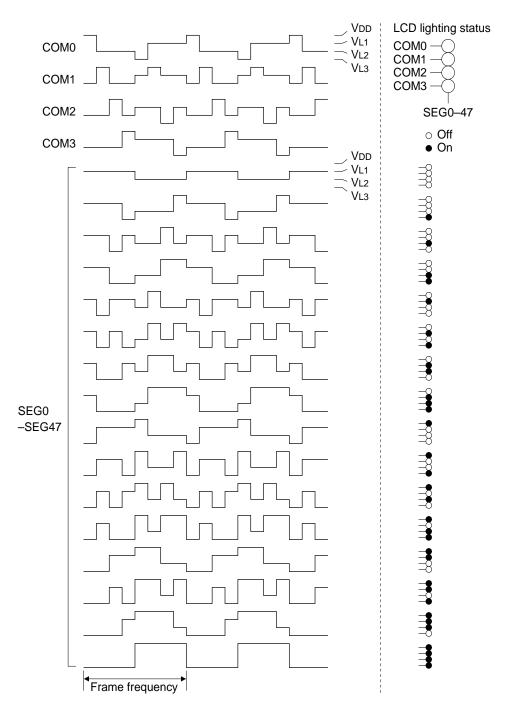

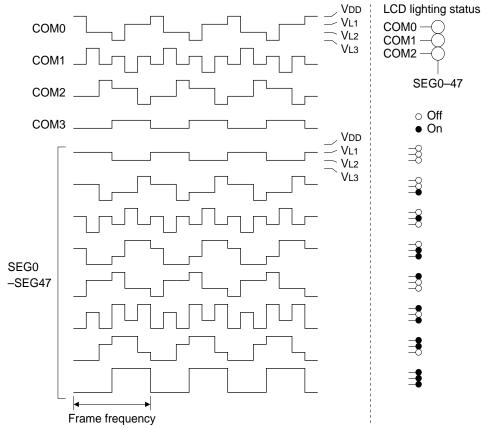

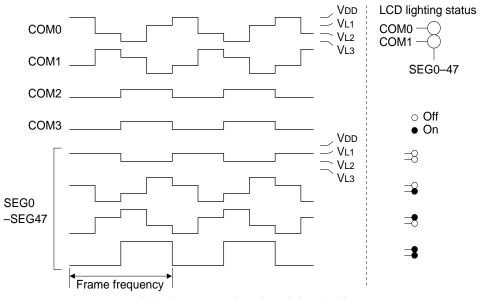

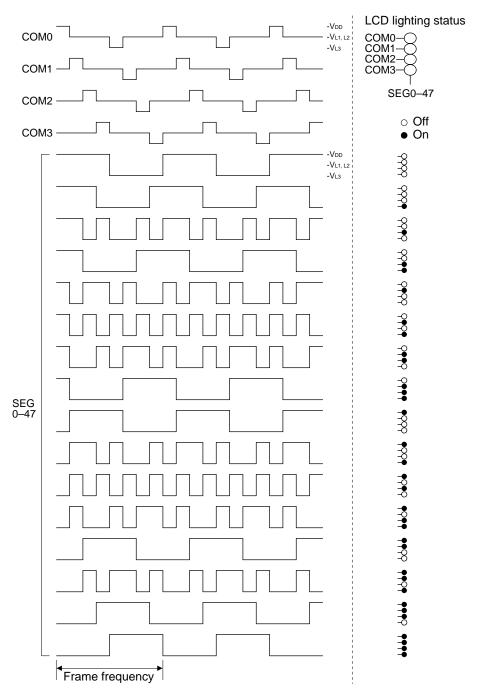

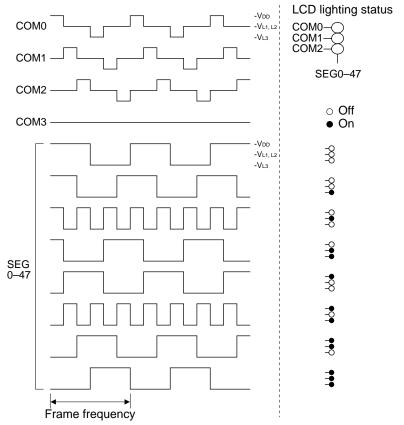

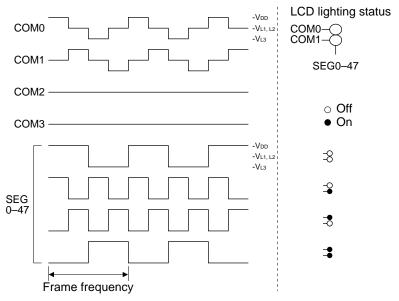

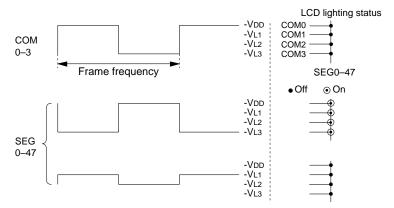

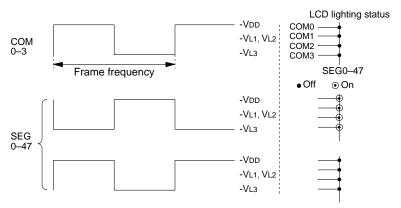

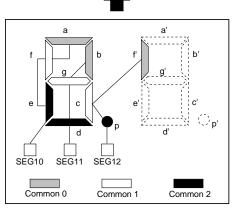

| 4.8  | LCD Driver (COM0–COM3, SEG0–SEG47)                   | I-41        |

|      | 4.8.1 Configuration of LCD driver                    | I_11        |

|      | 4.8.2 Cadence adjustment of oscillation frequency    |             |

|      |                                                      |             |

|      | 4.8.3 Mask option (segment allocation)               |             |

|      | 4.8.4 Control of LCD driver                          |             |

|      | 4.8.5 Programming notes                              | . I-49      |

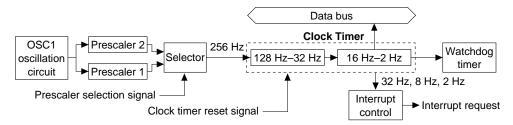

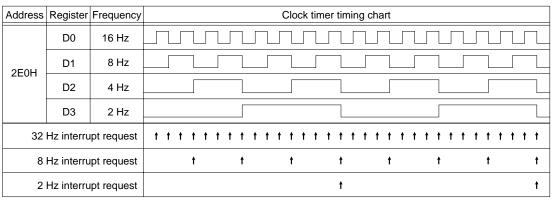

| 4.9  | Clock Timer                                          | I-50        |

|      | 4.9.1 Configuration of clock timer                   |             |

|      | 4.9.2 Interrupt function                             |             |

|      |                                                      |             |

|      | 4.9.3 Control of clock timer                         |             |

|      | 4.9.4 Programming notes                              | . 1-32      |

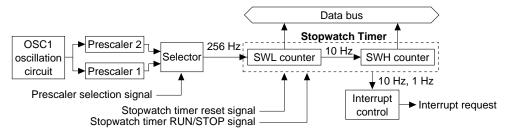

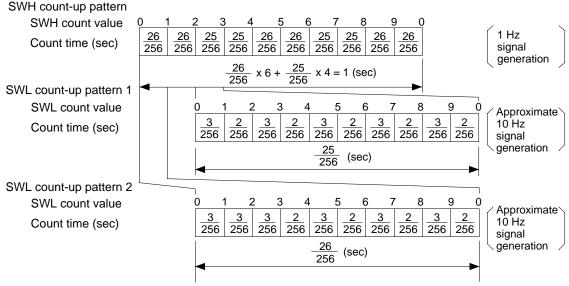

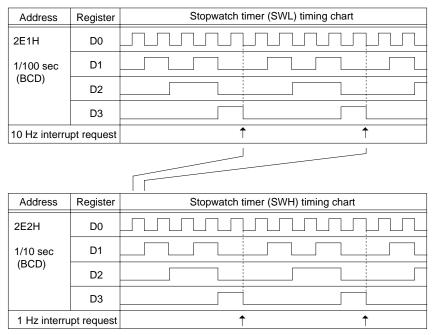

| 4.10 | Stopwatch Timer                                      | <i>I-53</i> |

|      | 4.10.1 Configuration of stopwatch timer              | . I-53      |

|      | 4.10.2 Count-up pattern                              |             |

|      | 4.10.3 Interrupt function                            |             |

|      | 4.10.4 Control of stopwatch timer                    |             |

|      | 4.10.5 Programming notes                             |             |

|      |                                                      |             |

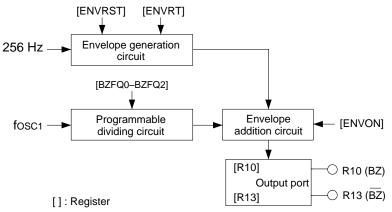

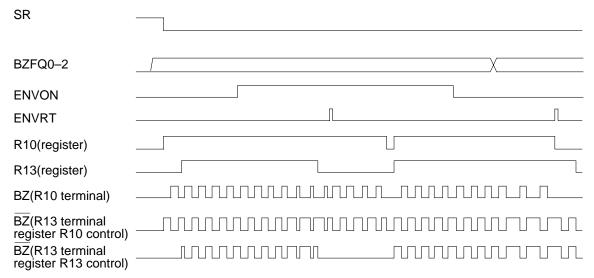

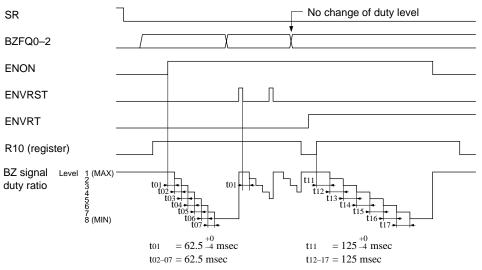

| 4.11 | Sound Generator                                      | <i>I-57</i> |

|      | 4.11.1 Configuration of sound generator              | . I-57      |

|      | 4.11.2 Frequency setting                             |             |

|      | 4.11.3 Digital envelope                              |             |

|      | 4.11.4 Mask option                                   |             |

|      | 4.11.5 Control of sound generator                    |             |

|      | 4.11.6 Programming note                              |             |

|      |                                                      |             |

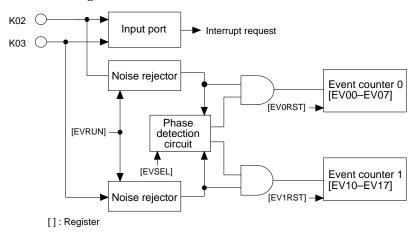

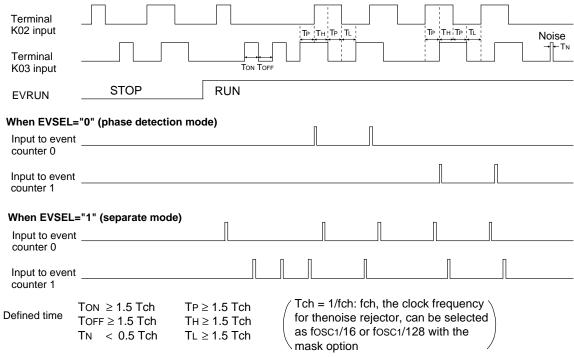

| 4.12 | Event Counter                                        |             |

|      | 4.12.1 Configuration of event counter                | . I-62      |

|      | 4.12.2 Switching count mode                          | . I-62      |

|      | 4.12.3 Mask option                                   | . I-63      |

|      | 4.12.4 Control of event counter                      |             |

|      | 4.12.5 Programming notes                             |             |

| 4.12 |                                                      |             |

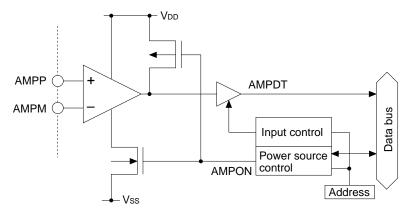

| 4.13 | Analog Comparator                                    |             |

|      | 4.13.1 Configuration of analog comparator            |             |

|      | 4.13.2 Operation of analog comparator                |             |

|      | 4.13.3 Control of analog comparator                  | . I-67      |

|      | 4.13.4 Programming notes                             |             |

| 111  |                                                      |             |

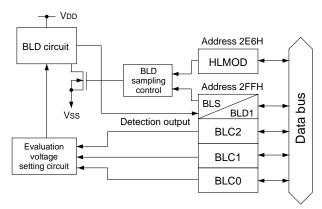

| 4.14 | Battery Life Detection (BLD) Circuit                 |             |

|      | 4.14.1 Configuration of BLD circuit                  |             |

|      | 4.14.2 Programmable selection of evaluation voltage  |             |

|      | 4.14.3 Detection timing of BLD circuit               |             |

|      | 4.14.4 Control of BLD circuit                        | . I-70      |

|      | 4.14.5 Programming notes                             | . I-71      |

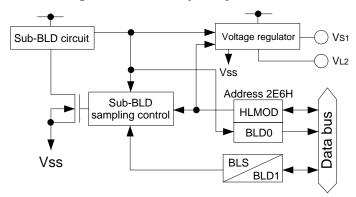

|           | 4.15 | Heavy Load Protection Function and Sub-BLD Circuit                   | <i>I-72</i>  |

|-----------|------|----------------------------------------------------------------------|--------------|

|           |      | 4.15.1 Heavy load protection function                                | <i>I-72</i>  |

|           |      | 4.15.2 Operation of sub-BLD circuit                                  |              |

|           |      | 4.15.3 Control of heavy load protection function and sub-BLD circuit |              |

|           |      | 4.15.4 Programming notes                                             | <i>I-76</i>  |

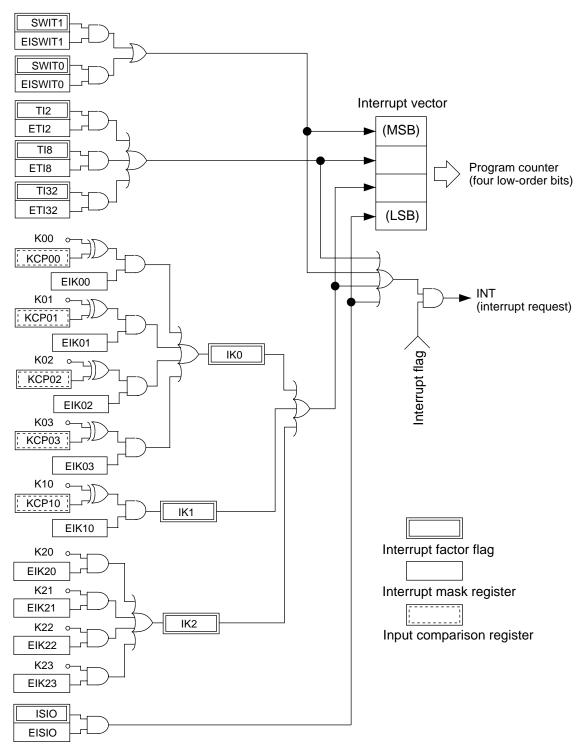

|           | 4.16 | Interrupt and HALT                                                   | <i>I-77</i>  |

|           |      | 4.16.1 Interrupt factors                                             |              |

|           |      | 4.16.2 Specific masks and factor flags for interrupt                 |              |

|           |      | 4.16.3 Interrupt vectors                                             |              |

|           |      | 4.16.4 Control of interrupt and HALT                                 |              |

|           |      | 4.16.5 Programming notes                                             | I-82         |

| CHAPTER 5 | SUM  | MARY OF NOTES                                                        | <i>I-83</i>  |

|           | 5.1  | Notes for Low Current Consumption                                    | <i>I-83</i>  |

|           | 5.2  | Summary of Notes by Function                                         | <i>I-84</i>  |

|           | 5.3  | Precautions on Mounting                                              | <i>I-89</i>  |

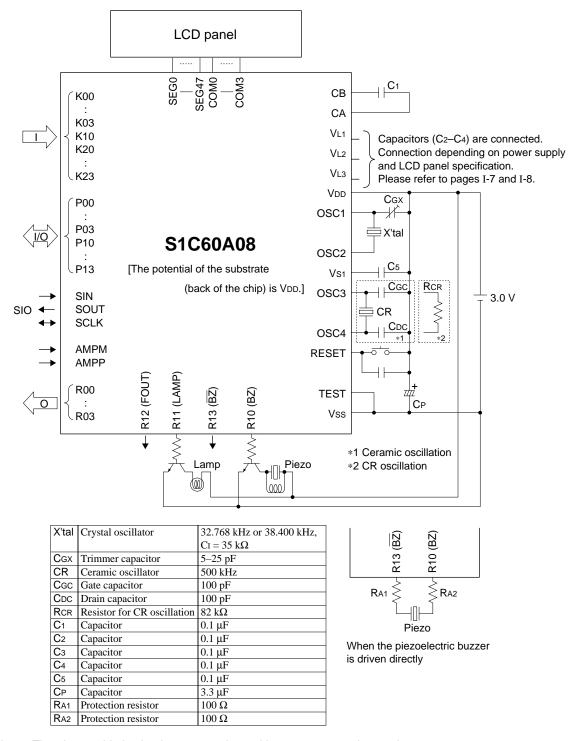

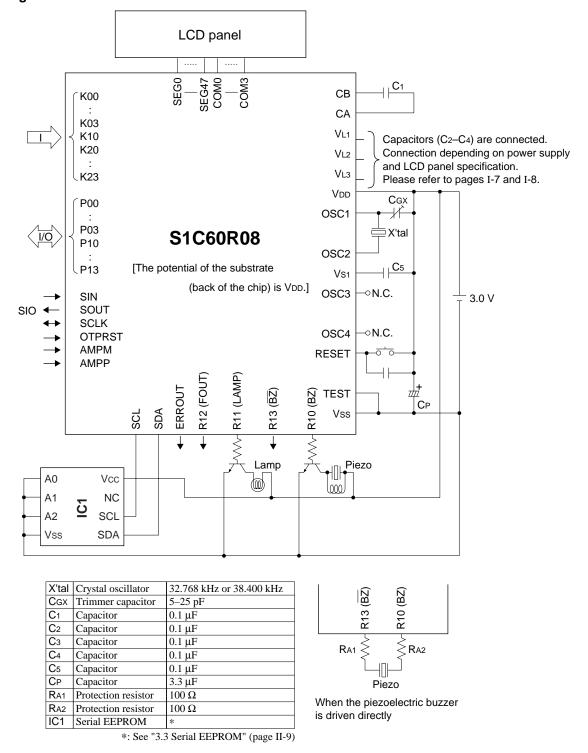

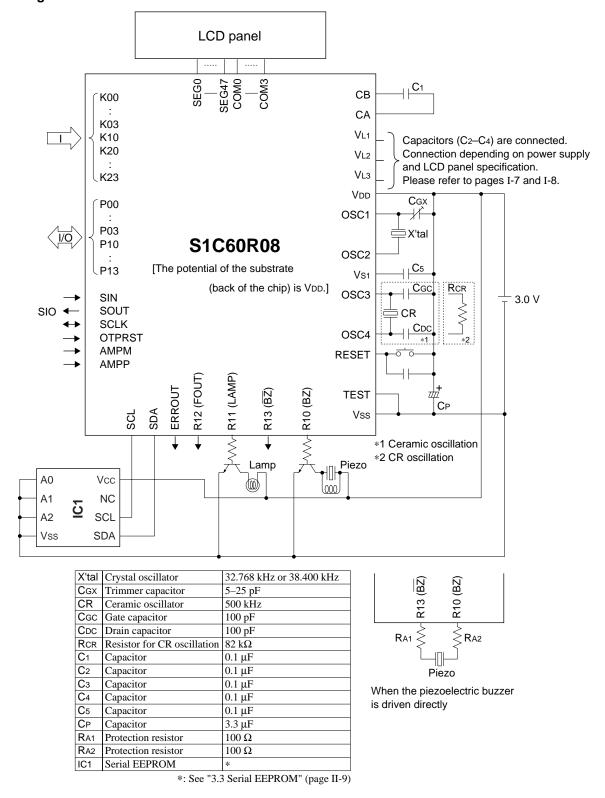

| CHAPTER 6 | BAS  | IC EXTERNAL WIRING DIAGRAM                                           | <i>I-91</i>  |

| CHAPTER 7 | ELE  | CTRICAL CHARACTERISTICS                                              | <i>I-93</i>  |

|           | 7.1  | Absolute Maximum Rating                                              |              |

|           | 7.2  | Recommended Operating Conditions                                     | <i>I-93</i>  |

|           | 7.3  | DC Characteristics                                                   | <i>I-94</i>  |

|           | 7.4  | Analog Circuit Characteristics and Current Consumption               | <i>I-95</i>  |

|           | 7.5  | Oscillation Characteristics                                          | <i>I-98</i>  |

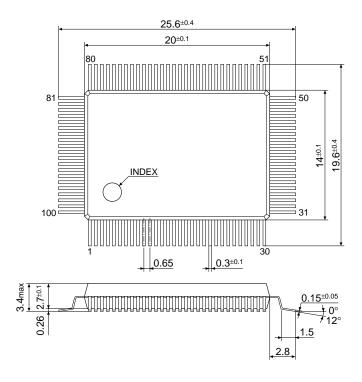

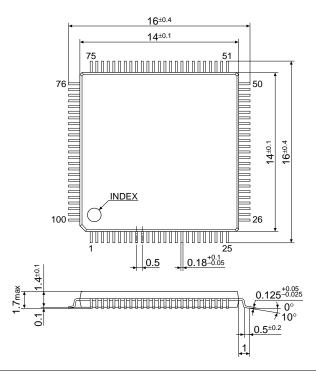

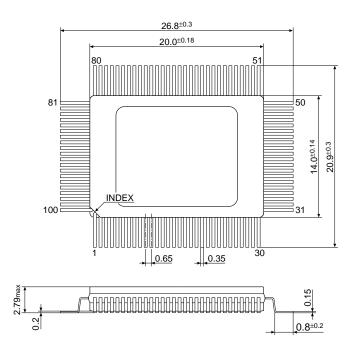

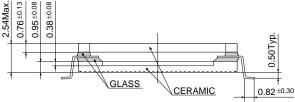

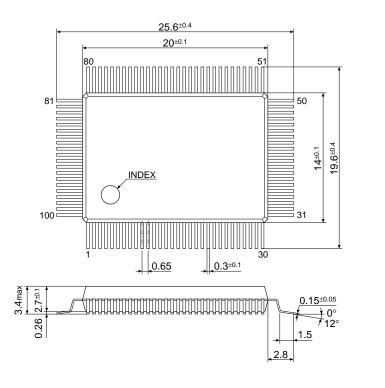

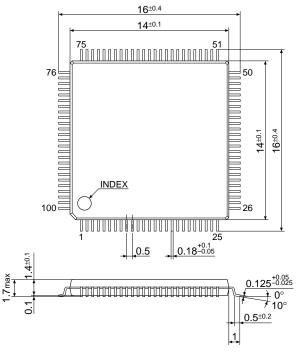

| CHAPTER 8 | PAC  | KAGE                                                                 | <i>I-99</i>  |

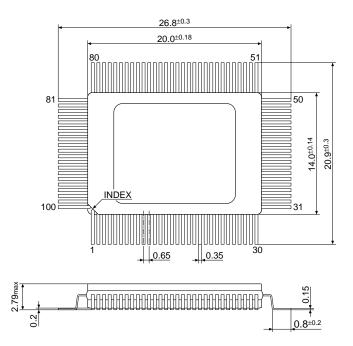

|           | 8.1  | Plastic Package                                                      |              |

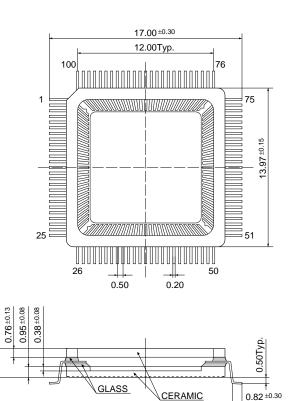

|           | 8.2  | Ceramic Package for Test Samples                                     | I-100        |

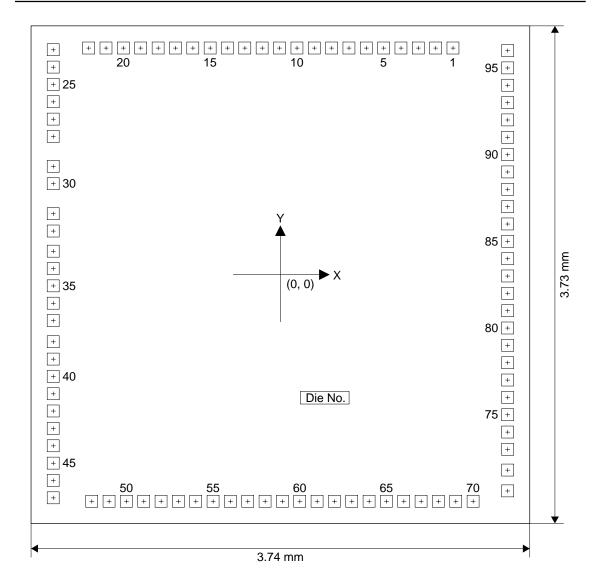

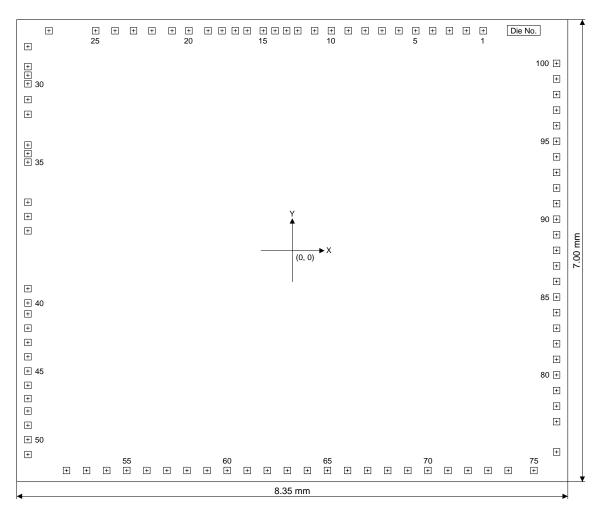

| CHAPTER 9 | PAD  | LAYOUT                                                               |              |

|           | 9.1  | Diagram of Pad Layout                                                | <i>I-101</i> |

|           | 9.2  | Pad Coordinates                                                      | <i>I-102</i> |

## CHAPTER 1 OVERVIEW

The S1C60N08 Series is a single-chip microcomputer made up of the 4-bit core CPU S1C6200C, ROM (4,096 words  $\times$  12 bits), RAM (832 words  $\times$  4 bits), LCD driver, serial interface, event counter with dial input function, watchdog timer, and two types of time base counter. Because of its low-voltage operation and low power consumption, this series is ideal for a wide range of applications, and is especially suitable for battery-driven systems.

## 1.1 Configuration

The S1C60N08 Series is configured as follows, depending on supply voltage and oscillation circuits.

Table 1.1.1 Model configuration

| Model           | S1C60N08       | S1C60A08      | S1C60L08       |

|-----------------|----------------|---------------|----------------|

| Supply voltage  | 3.0 V          | 3.0 V         | 1.5 V          |

| Oscillation     | OSC1 only      | OSC1 and OSC3 | OSC1 only      |

| circuit         | (Single clock) | (Twin clock)  | (Single clock) |

| Evaluation tool | S1C6           | _             |                |

#### 1.2 Features

Table 1.2.1 Features

| Model            |                      | S1C60N08/S1C60R08                                       | S1C60L08                               | S1C60A08/S1C60R08            |  |  |  |  |  |  |  |  |

|------------------|----------------------|---------------------------------------------------------|----------------------------------------|------------------------------|--|--|--|--|--|--|--|--|

| OSC1 oscillati   | ion circuit          | Crystal oscillatio                                      | on circuit 32.768 kHz (Typ.)/38        | 3.400 kHz (Typ.)             |  |  |  |  |  |  |  |  |

| OSC3 oscillati   | ion circuit          | _                                                       |                                        | CR or ceramic oscillation    |  |  |  |  |  |  |  |  |

|                  |                      |                                                         |                                        | circuit (selected by mask    |  |  |  |  |  |  |  |  |

|                  |                      |                                                         |                                        | option) 500 kHz (Typ.)       |  |  |  |  |  |  |  |  |

| Instruction set  |                      |                                                         | 108 types                              |                              |  |  |  |  |  |  |  |  |

| Instruction exe  | ecution time         | 153 μsec, 2                                             | 214 $\mu$ sec, 366 $\mu$ sec (CLK = 32 | .768 kHz)                    |  |  |  |  |  |  |  |  |

| (differs depen   | ding on instruction) | 130 µsec,                                               | 182 μsec, 313 μsec (CLK = 38           | .400 kHz)                    |  |  |  |  |  |  |  |  |

| (CLK: CPU op     | peration frequency)  | – 10 μsec, 14 μsec, 24 μ                                |                                        |                              |  |  |  |  |  |  |  |  |

|                  |                      |                                                         |                                        | (CLK = 500  kHz)             |  |  |  |  |  |  |  |  |

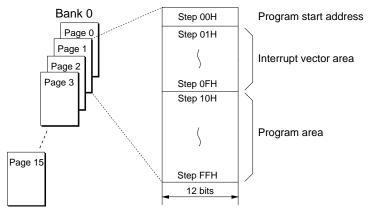

| ROM capacity     | 1                    | $4,096 \text{ words} \times 12 \text{ bits}$            |                                        |                              |  |  |  |  |  |  |  |  |

| RAM capacity     | '                    | 832 words × 4 bits                                      |                                        |                              |  |  |  |  |  |  |  |  |

| Input ports      |                      | 9 bits (pull-down resistor can be added by mask option) |                                        |                              |  |  |  |  |  |  |  |  |

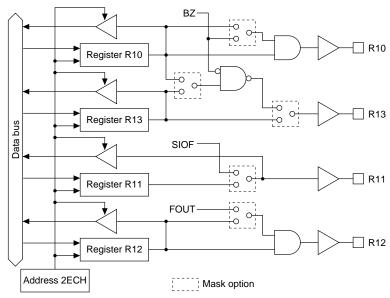

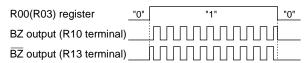

| Output ports     |                      | 8 bits (BZ, BZ, F                                       | FOUT and SIOF outputs are av           | ailable by mask option)      |  |  |  |  |  |  |  |  |

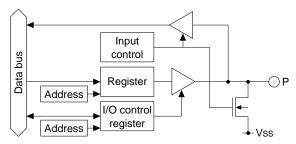

| I/O ports        |                      | 8 bits (pull-dow                                        | n resistor is added during inpu        | t data read-out)             |  |  |  |  |  |  |  |  |

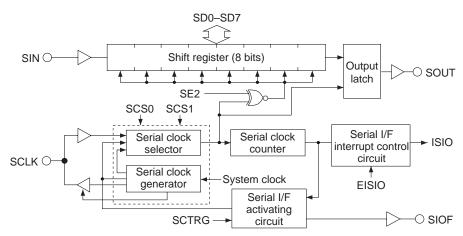

| Serial interfac  | е                    | 1 port (8-bit clock synchronous system)                 |                                        |                              |  |  |  |  |  |  |  |  |

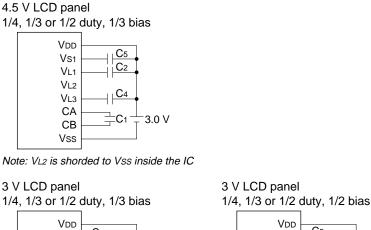

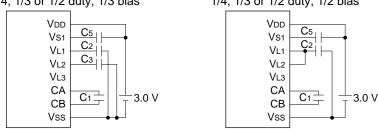

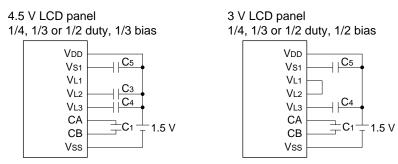

| LCD driver       |                      |                                                         | 4, 3, or 2 commons (selected by        |                              |  |  |  |  |  |  |  |  |

|                  |                      | V-3 V 1/4, 1/3 or                                       | r 1/2 duty (voltage regulator ar       | d booster circuits built-in) |  |  |  |  |  |  |  |  |

| Time base cou    | unter                | Two types (timer and stopwatch)                         |                                        |                              |  |  |  |  |  |  |  |  |

| Watchdog time    |                      | Built-in (can be disabled by mask option)               |                                        |                              |  |  |  |  |  |  |  |  |

| Event counter    | •                    | Two 8-bit inputs (dial input evaluation or independent) |                                        |                              |  |  |  |  |  |  |  |  |

| Sound genera     | ntor                 | Progra                                                  | mmable in 8 sounds (8 frequen          | ncies)                       |  |  |  |  |  |  |  |  |

|                  |                      | Digital envelop                                         | pe built-in (can be disabled by        | mask option)                 |  |  |  |  |  |  |  |  |

| Analog compa     |                      |                                                         | ed input $\times$ 1, non-inverted inpu |                              |  |  |  |  |  |  |  |  |

| Battery low de   | etection circuit     |                                                         | programmable in 8 values and           | a fixed value)               |  |  |  |  |  |  |  |  |

| (BLD)            |                      | 2.4 V, 2.2–2.55 V                                       | 1.2 V, 1.05–1.4 V                      | 2.4 V, 2.2–2.55 V            |  |  |  |  |  |  |  |  |

| External interr  |                      |                                                         | Input interrupt: 3 systems             |                              |  |  |  |  |  |  |  |  |

| Internal interru | upt                  |                                                         | e base counter interrupt: 2 syste      |                              |  |  |  |  |  |  |  |  |

|                  |                      |                                                         | rial interface interrupt: 1 system     |                              |  |  |  |  |  |  |  |  |

| Supply voltage   |                      | 3.0 V (1.8–3.5 V)                                       | 1.5 V (0.9–1.7 V)                      | 3.0 V (2.2–3.5 V)            |  |  |  |  |  |  |  |  |

| Current          | CLK= 32.768 kHz      | 1.0 μΑ                                                  | 1.0 μΑ                                 | 1.1 μΑ                       |  |  |  |  |  |  |  |  |

| consumption      | (when halted)        |                                                         |                                        |                              |  |  |  |  |  |  |  |  |

| (Typ. value)     | CLK= 32.768 kHz      | 2.2 μΑ                                                  | 2.2 μΑ                                 | 3.0 μΑ                       |  |  |  |  |  |  |  |  |

|                  | (when executed)      |                                                         |                                        |                              |  |  |  |  |  |  |  |  |

|                  | CLK= 500 kHz         | -                                                       | _                                      | 50 μΑ                        |  |  |  |  |  |  |  |  |

|                  | (when executed)      |                                                         |                                        |                              |  |  |  |  |  |  |  |  |

| Form when sh     | nipped               | QFF                                                     | P5-100pin, QFP15-100pin or c           | hip                          |  |  |  |  |  |  |  |  |

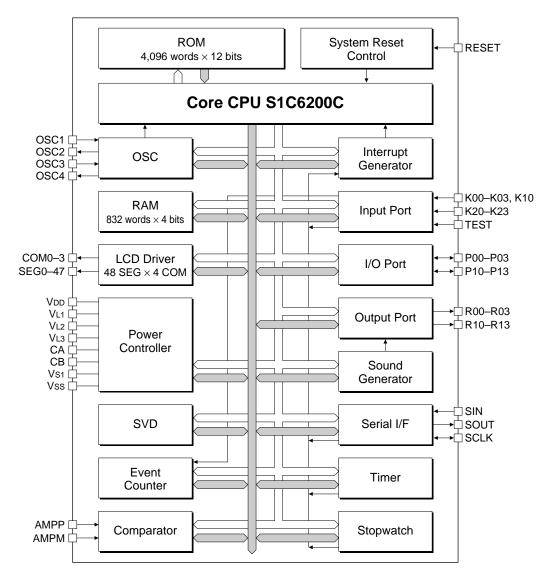

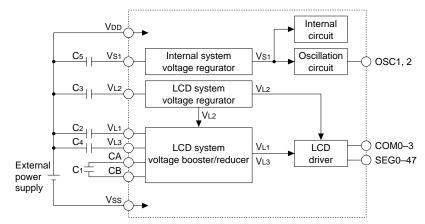

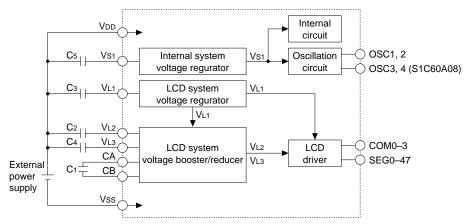

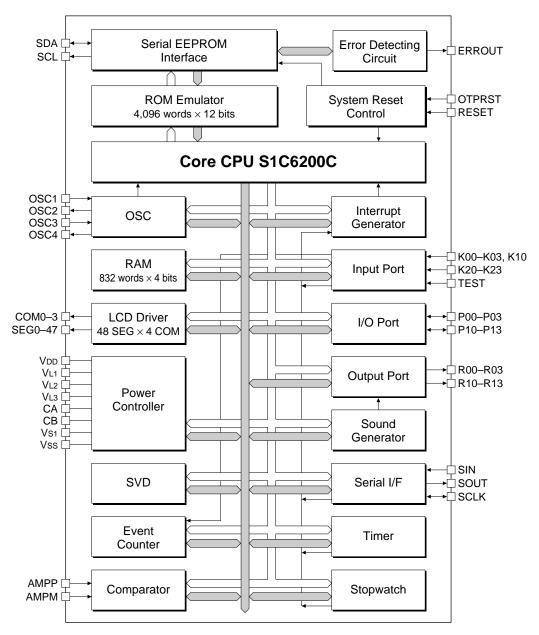

## 1.3 Block Diagram

Fig. 1.3.1 Block diagram

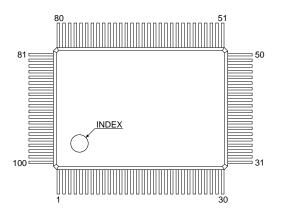

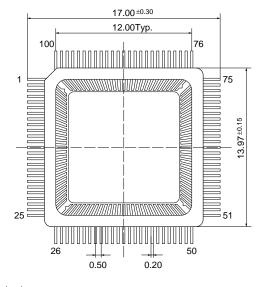

## 1.4 Pin Layout Diagram

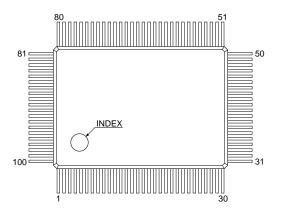

## QFP5-100pin

| No. | Pin name        |

|-----|----------|-----|----------|-----|----------|-----|-----------------|

| 1   | COM1     | 26  | SEG24    | 51  | SEG0     | 76  | P10             |

| 2   | COM0     | 27  | TEST     | 52  | AMPP     | 77  | R03             |

| 3   | SEG47    | 28  | SEG23    | 53  | AMPM     | 78  | R02             |

| 4   | SEG46    | 29  | SEG22    | 54  | K23      | 79  | R01             |

| 5   | SEG45    | 30  | SEG21    | 55  | K22      | 80  | R00             |

| 6   | SEG44    | 31  | SEG20    | 56  | K21      | 81  | R12             |

| 7   | SEG43    | 32  | SEG19    | 57  | K20      | 82  | R11             |

| 8   | SEG42    | 33  | SEG18    | 58  | K10      | 83  | R10             |

| 9   | SEG41    | 34  | SEG17    | 59  | K03      | 84  | R13             |

| 10  | SEG40    | 35  | SEG16    | 60  | K02      | 85  | Vss             |

| 11  | SEG39    | 36  | SEG15    | 61  | K01      | 86  | RESET           |

| 12  | SEG38    | 37  | SEG14    | 62  | K00      | 87  | OSC4            |

| 13  | SEG37    | 38  | SEG13    | 63  | SIN      | 88  | OSC3            |

| 14  | SEG36    | 39  | SEG12    | 64  | SOUT     | 89  | Vs1             |

| 15  | SEG35    | 40  | SEG11    | 65  | N.C.     | 90  | OSC2            |

| 16  | SEG34    | 41  | SEG10    | 66  | SCLK     | 91  | OSC1            |

| 17  | SEG33    | 42  | SEG9     | 67  | P03      | 92  | Vdd             |

| 18  | SEG32    | 43  | SEG8     | 68  | P02      | 93  | VL3             |

| 19  | SEG31    | 44  | SEG7     | 69  | P01      | 94  | VL2             |

| 20  | SEG30    | 45  | SEG6     | 70  | P00      | 95  | V <sub>L1</sub> |

| 21  | SEG29    | 46  | SEG5     | 71  | N.C.     | 96  | CA              |

| 22  | SEG28    | 47  | SEG4     | 72  | N.C.     | 97  | CB              |

| 23  | SEG27    | 48  | SEG3     | 73  | P13      | 98  | N.C.            |

| 24  | SEG26    | 49  | SEG2     | 74  | P12      | 99  | COM3            |

| 25  | SEG25    | 50  | SEG1     | 75  | P11      | 100 | COM2            |

N.C. = No connection

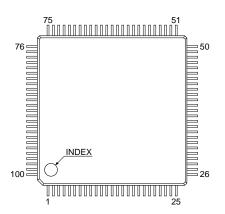

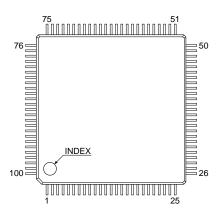

## QFP15-100pin

| No. | Pin name        |

|-----|----------|-----|----------|-----|----------|-----|-----------------|

| 1   | SEG47    | 26  | SEG23    | 51  | AMPP     | 76  | R02             |

| 2   | SEG46    | 27  | SEG22    | 52  | AMPM     | 77  | R01             |

| 3   | SEG45    | 28  | SEG21    | 53  | K23      | 78  | R00             |

| 4   | SEG44    | 29  | SEG20    | 54  | K22      | 79  | R12             |

| 5   | SEG43    | 30  | SEG19    | 55  | K21      | 80  | R11             |

| 6   | SEG42    | 31  | SEG18    | 56  | K20      | 81  | R10             |

| 7   | SEG41    | 32  | SEG17    | 57  | K10      | 82  | R13             |

| 8   | SEG40    | 33  | SEG16    | 58  | K03      | 83  | Vss             |

| 9   | SEG39    | 34  | SEG15    | 59  | K02      | 84  | RESET           |

| 10  | SEG38    | 35  | SEG14    | 60  | K01      | 85  | OSC4            |

| 11  | SEG37    | 36  | SEG13    | 61  | K00      | 86  | OSC3            |

| 12  | SEG36    | 37  | SEG12    | 62  | SIN      | 87  | Vs1             |

| 13  | SEG35    | 38  | N.C.     | 63  | SOUT     | 88  | OSC2            |

| 14  | SEG34    | 39  | SEG11    | 64  | N.C.     | 89  | OSC1            |

| 15  | SEG33    | 40  | SEG10    | 65  | SCLK     | 90  | Vdd             |

| 16  | SEG32    | 41  | SEG9     | 66  | N.C.     | 91  | VL3             |

| 17  | SEG31    | 42  | SEG8     | 67  | P03      | 92  | VL2             |

| 18  | SEG30    | 43  | SEG7     | 68  | P02      | 93  | V <sub>L1</sub> |

| 19  | SEG29    | 44  | SEG6     | 69  | P01      | 94  | CA              |

| 20  | SEG28    | 45  | SEG5     | 70  | P00      | 95  | CB              |

| 21  | SEG27    | 46  | SEG4     | 71  | P13      | 96  | N.C.            |

| 22  | SEG26    | 47  | SEG3     | 72  | P12      | 97  | COM3            |

| 23  | SEG25    | 48  | SEG2     | 73  | P11      | 98  | COM2            |

| 24  | SEG24    | 49  | SEG1     | 74  | P10      | 99  | COM1            |

| 25  | TEST     | 50  | SEG0     | 75  | R03      | 100 |                 |

N.C. = No connection

Fig. 1.4.1 Pin layout

## 1.5 Pin Description

Table 1.5.1 Pin description

| D'       | Pin           | No.         | 1/0 | Formula                                                                 |  |  |  |  |  |

|----------|---------------|-------------|-----|-------------------------------------------------------------------------|--|--|--|--|--|

| Pin name | QFP5-100      | QFP15-100   | I/O | Function                                                                |  |  |  |  |  |

| Vdd      | 92            | 90          | (I) | Power supply pin (+)                                                    |  |  |  |  |  |

| Vss      | 85            | 83          | (I) | Power supply pin (-)                                                    |  |  |  |  |  |

| Vs1      | 89            | 87          | -   | Oscillation and internal logic system voltage output pin                |  |  |  |  |  |

| VL1      | 95            | 93          | -   | LCD drive voltage output pin (approx1.05 V or 1/2·VL2)                  |  |  |  |  |  |

| VL2      | 94            | 92          | -   | LCD drive voltage output pin (2·VL1 or approx2.10 V)                    |  |  |  |  |  |

| VL3      | 93            | 91          | -   | LCD drive voltage output pin (3·VL1 or 3/2·VL2)                         |  |  |  |  |  |

| CA, CB   | 96, 97        | 94, 95      | -   | Boost capacitor connecting pin                                          |  |  |  |  |  |

| OSC1     | 91            | 89          | I   | Crystal oscillation input pin                                           |  |  |  |  |  |

| OSC2     | 90            | 88          | О   | Crystal oscillation output pin                                          |  |  |  |  |  |

| OSC3     | 88            | 86          | I   | CR or ceramic oscillation input pin * (N.C. for S1C60N08 and S1C60L08)  |  |  |  |  |  |

| OSC4     | 87            | 85          | О   | CR or ceramic oscillation output pin * (N.C. for S1C60N08 and S1C60L08) |  |  |  |  |  |

| K00-K03  | 62–59         | 61–58       | I   | Input port pin                                                          |  |  |  |  |  |

| K10      | 58            | 57          | I   | Input port pin                                                          |  |  |  |  |  |

| K20-K23  | 57–54         | 56–53       | I   | Input port pin                                                          |  |  |  |  |  |

| P00-P03  | 70–67         | 70–67       | I/O | I/O port pin                                                            |  |  |  |  |  |

| P10-P13  | 76–73         | 74–71       | I/O | I/O port pin                                                            |  |  |  |  |  |

| R00-R03  | 80–77         | 78–75       | О   | Output port pin                                                         |  |  |  |  |  |

| R10      | 83            | 81          | О   | Output port pin or BZ output pin *                                      |  |  |  |  |  |

| R13      | 84            | 82          | О   | Output port pin or BZ output pin *                                      |  |  |  |  |  |

| R11      | 82            | 80          | О   | Output port pin or SIOF output pin *                                    |  |  |  |  |  |

| R12      | 81            | 79          | О   | Output port pin or FOUT output pin *                                    |  |  |  |  |  |

| SIN      | 63            | 62          | I   | Serial interface data input pin                                         |  |  |  |  |  |

| SOUT     | 64            | 63          | О   | Serial interface data output pin                                        |  |  |  |  |  |

| SCLK     | 66            | 65          | I/O | Serial interface clock input/output pin                                 |  |  |  |  |  |

| AMPP     | 52            | 51          | I   | Analog comparator non-inverted input pin                                |  |  |  |  |  |

| AMPM     | 53            | 52          | I   | Analog comparator inverted input pin                                    |  |  |  |  |  |

| SEG0-47  | 51–28, 26–3   | 50–39,      | О   | LCD segment output pin                                                  |  |  |  |  |  |

|          |               | 37–26, 24–1 |     | or DC output pin *                                                      |  |  |  |  |  |

| COM0-3   | 2, 1, 100, 99 | 100–97      | 0   | LCD common output pin (1/2, 1/3 or 1/4 duty are selectable *)           |  |  |  |  |  |

| RESET    | 86            | 84          | I   | Initial reset input pin                                                 |  |  |  |  |  |

| TEST     | 27            | 25          | I   | Input pin for test                                                      |  |  |  |  |  |

|          |               |             |     |                                                                         |  |  |  |  |  |

<sup>\*</sup> Can be selected by mask option

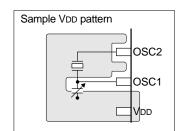

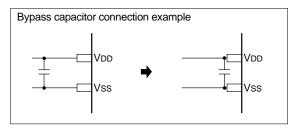

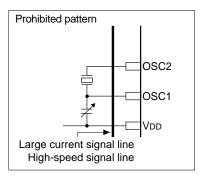

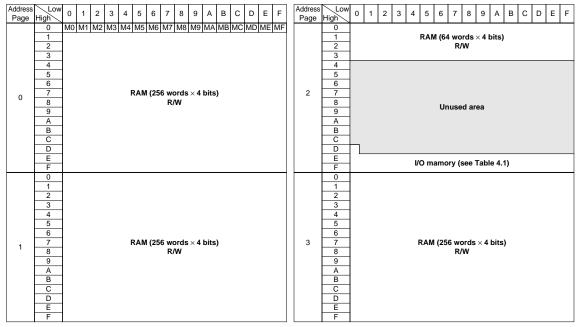

## 1.6 S1C60N08 Option List