### **CMOS 32-BIT SINGLE CHIP MICROCONTROLLER**

# S1C33E07 Technical Manual

# NOTICE No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of Economy, Trade and Industry or other approval from another government agency. All brands or product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

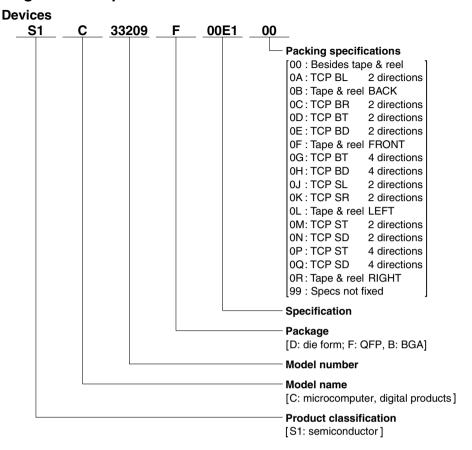

### Configuration of product number

# S1C33E07 Technical Manual

| L 0400000 OREGIFICATIONS                             |                  |

|------------------------------------------------------|------------------|

| I S1C33E07 SPECIFICATIONS                            | I                |

| I.1 Overview                                         | Overview         |

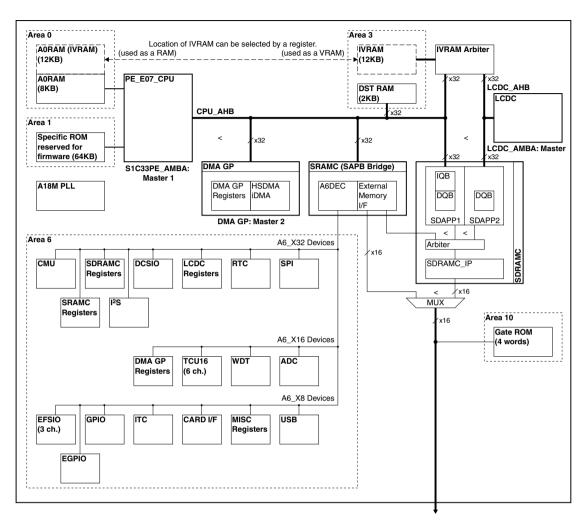

| I.2 Block Diagram                                    | Block            |

| I.3 Pin Description                                  | Pin              |

| I.4 Power Supply                                     | Power            |

| I.5 CPU Core and Bus Architecture                    | CPU              |

| I.6 Memory Map                                       | Map              |

| I.7 Electrical Characteristics                       | E char           |

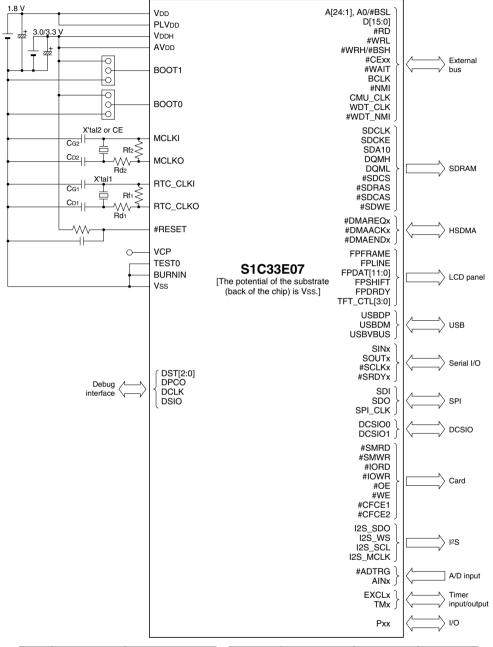

| I.8 Basic External Wiring Diagram                    | Wiring           |

| I.9 Precautions on Mounting                          | Mount            |

| II BUS MODULES                                       | II               |

| II.1 High-Speed DMA (HSDMA)                          | HSDMA            |

| II.2 Intelligent DMA (IDMA)                          | IDMA             |

| II.3 SRAM Controller (SRAMC)                         | SRAMC            |

| II.4 SDRAM Controller (SDRAMC)                       | SDRAMC           |

| III PERIPHERAL MODULES 1 (SYSTEM)                    | III              |

| III.1 Clock Management Unit (CMU)                    | CMU              |

| III.2 Interrupt Controller (ITC)                     | ITC              |

| III.3 Real-Time Clock (RTC)                          | RTC              |

| III.4 Misc Registers                                 | MISC             |

| IV PERIPHERAL MODULES 2 (TIMERS)                     | IV               |

| IV.1 16-Bit Timers (T16)                             | T16              |

| IV.2 Watchdog Timer (WDT)                            | WDT              |

| V PERIPHERAL MODULES 3 (INTERFACE)                   | V                |

| V.1 General-Purpose Serial Interface (EFSIO)         | EFSIO            |

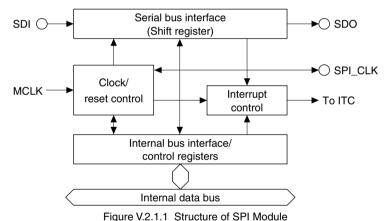

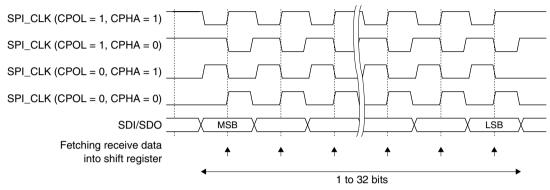

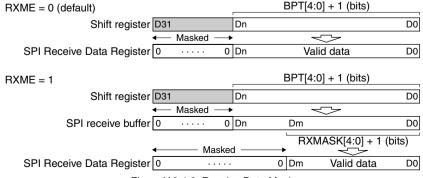

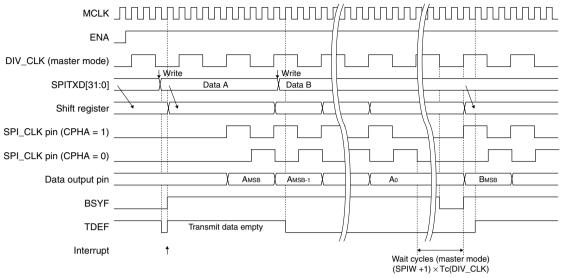

| V.2 Serial Peripheral Interface (SPI)                | SPI              |

| V.3 Direction Control Serial Interface (DCSIO)       | DCSIO            |

| V.4 Card Interface (CARD)                            | CARD             |

| V.5 I <sup>2</sup> S Interface (I <sup>2</sup> S)    | I <sup>2</sup> S |

| VI PERIPHERAL MODULES 4 (PORTS)                      | VI               |

| VI.1 General-Purpose I/O Ports (GPIO)                | GPIO             |

| VI.2 Extended General-Purpose I/O Ports (EGPIO)      | EGPIO            |

| VII PERIPHERAL MODULES 5 (ANALOG)                    | VII              |

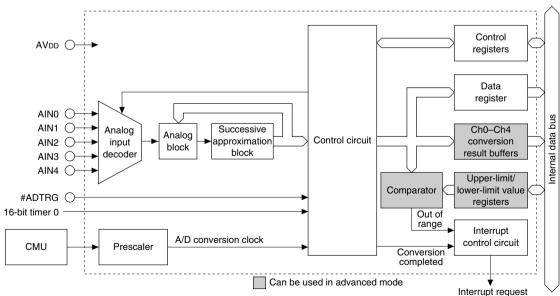

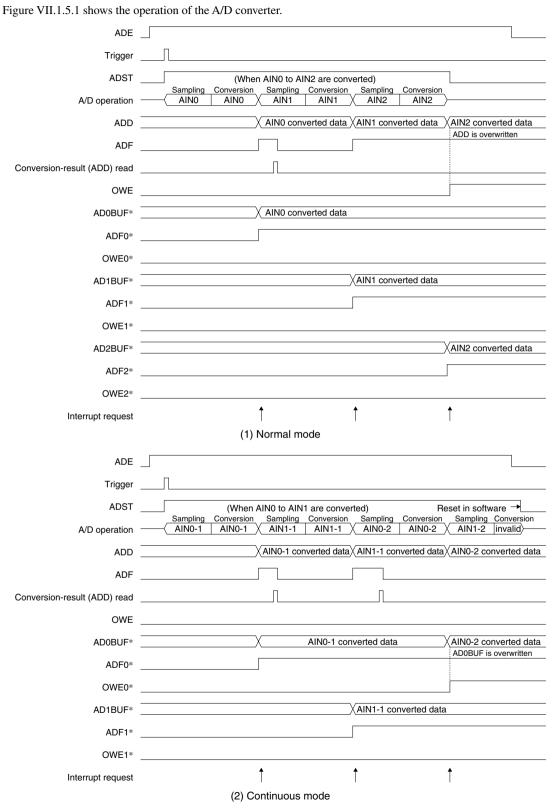

| VII.1 A/D Converter (ADC)                            | ADC              |

| VIII PERIPHERAL MODULES 6 (LCD)                      | VIII             |

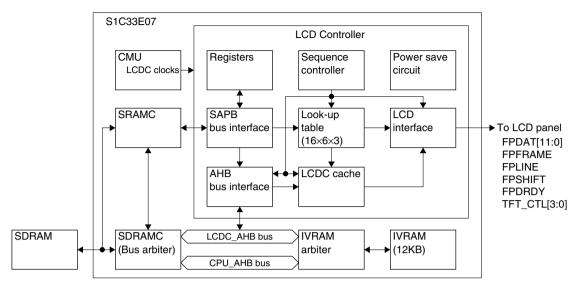

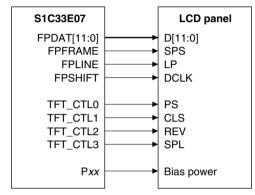

| VIII.1 LCD Controller (LCDC)                         | LCDC             |

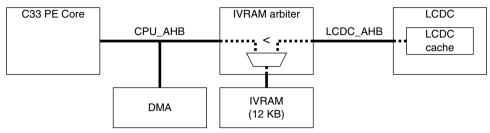

| VIII.2 IVRAM and IVRAM Arbiter                       | IVRAM            |

| IX PERIPHERAL MODULES 7 (USB)                        | IX               |

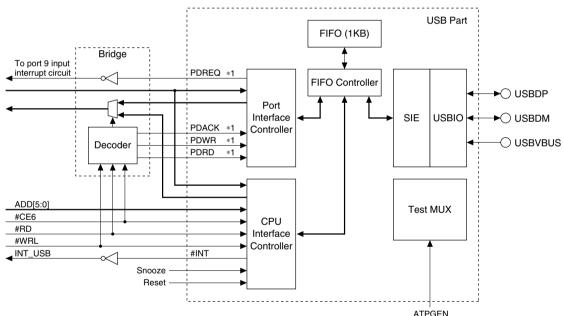

| IX.1 USB Function Controller (USB)                   | USB              |

| APPENDIX                                             | AP               |

| A I/O Map                                            | I/Omap           |

| B Differences Between C33 PE Core and Other C33 Core | СЗЗРЕ            |

| C Development Tools                                  | DEV              |

| D Boot                                               | Boot             |

| E Summary of Precautions                             | Notes            |

| F Supplementary Description for Clock Control        | Clock            |

|                                                      |                  |

### **Application**

This manual describes the hardware functions and control registers of the S1C33E07 or Seiko Epson's RISC-type 32-bit microcomputer, and precautions to observe when designing the application system for the microcomputer. Since this manual is written for those who design applications and circuits, knowledge of embedded-type microcomputers and the functionality and control of general peripheral circuits is required to understand the contents of this manual.

### **Organization of the Manual**

### I. S1C33E07 Specifications

This chapter outlines the S1C33E07 and describes the pin functions, and electrical characteristics. Also noise protection and other precautions to be taken when mounting the chip on the circuit board are included.

### **II. Bus Module**

This chapter describes the modules to control DMA and the bus.

### III-IX Peripheral Modules

This chapter describes each peripheral module embedded in the S1C33E07.

### **Appendix**

Provides a list of control registers built into the S1C33E07 and other additional information.

### **Notational Conventions for Control Bits and Addresses**

This manual describes some control bits as follows:

```

Example: 16-bit timer RUN/STOP control bits PRUNx (D0/0x300786 + 8•x)

```

'x' in this example represents a timer number (0 to 5). Timer 0 to timer 5 have control bits for each timer that have the same functions as other timers. This manual uses 'x' to describe two or more control bits (or addresses) in a bit name (or an expression). Therefore, 'x' should be substituted with 0 to 5 in this example to obtain the actual bit names and addresses.

```

Timer 0: PRUN0 (D0/0x300786)

*0x300786 + 8 \times 0 = 0x300786

Timer 1: PRUN1 (D0/0x30078E)

*0x300786 + 8 \times 1 = 0x30078E

Timer 2: PRUN2 (D0/0x300796)

*0x300786 + 8 \times 2 = 0x300796

Timer 3: PRUN3 (D0/0x30079E)

*0x300786 + 8 \times 3 = 0x30079E

Timer 4: PRUN4 (D0/0x3007AE)

*0x300786 + 8 \times 4 = 0x3007AE

```

<sup>&#</sup>x27;x' is used for not only timer numbers, but also memory block numbers, A/D converter channel numbers and others.

### - Contents -

### I S1C33E07 SPECIFICATIONS

|            |           | ······································                           |                    |

|------------|-----------|------------------------------------------------------------------|--------------------|

| <b>I.2</b> | Block Dia | ngram                                                            | I-2-1              |

| 1.3        | Pin Desci | ription                                                          | I-3-1              |

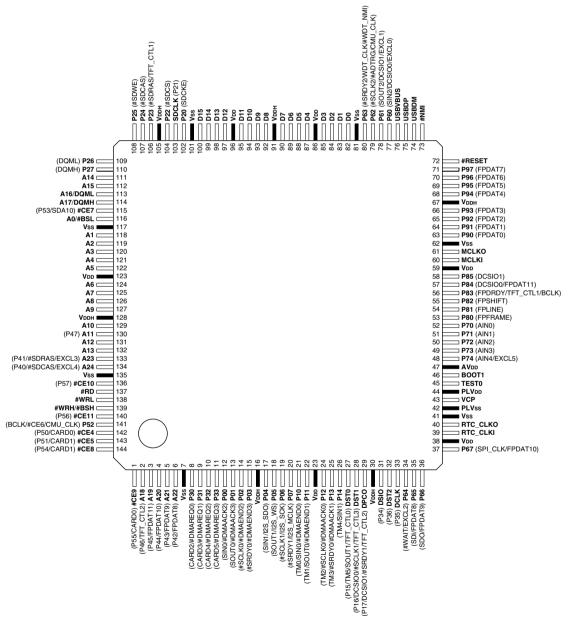

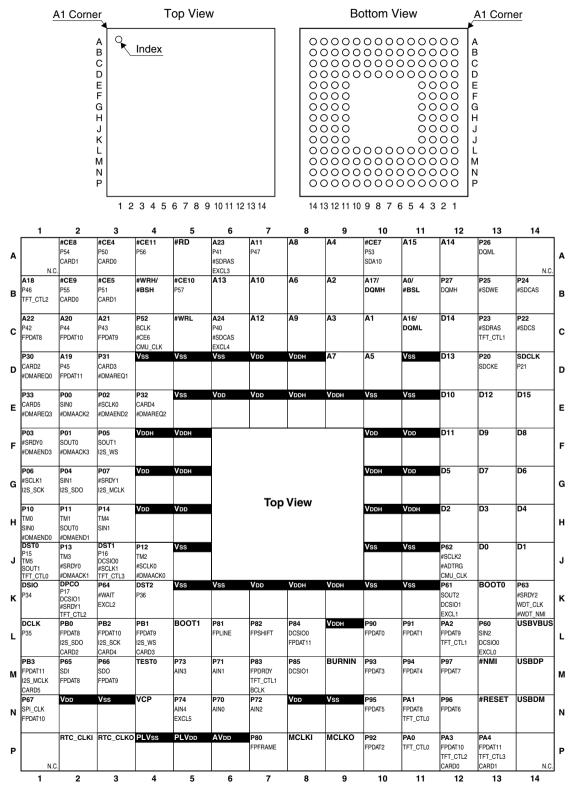

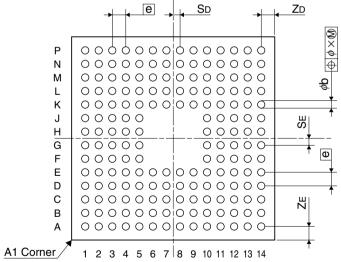

|            | I.3.1 Pii | n Arrangement                                                    | I-3-1              |

|            |           | .3.1.1 QFP Package Pin Arrangement (S1C33E07F)                   |                    |

|            |           | .3.1.2 PFBGA Package Pin Arrangement (S1C33E07B)                 |                    |

|            |           | n Functions                                                      |                    |

|            |           | vitching Over the Multiplexed Pin Functions                      |                    |

|            |           | 3.3.1 Pin Function Select Bits                                   |                    |

|            |           | .3.3.2 List of Port Function Select Registers                    |                    |

|            | 1.        | 0x3003A0: P00–P03 Port Function Select Register (pP0_03_CFP)     |                    |

|            |           | 0x3003A1: P04–P07 Port Function Select Register (pr 0_03_crr / ) |                    |

|            |           | 0x3003A2: P10–P13 Port Function Select Register (pP1_03_CFP)     |                    |

|            |           | 0x3003A3: P14–P17 Port Function Select Register (pP1_47_CFP)     |                    |

|            |           | 0x3003A4: P20–P23 Port Function Select Register (pP2_03_CFP)     |                    |

|            |           | 0x3003A5: P24–P27 Port Function Select Register (pP2_47_CFP)     | I-3-18             |

|            |           | 0x3003A6: P30–P33 Port Function Select Register (pP3_03_CFP)     |                    |

|            |           | 0x3003A7: P34–P36 Port Function Select Register (pP3_46_CFP)     |                    |

|            |           | 0x3003A8: P40–P43 Port Function Select Register (pP4_03_CFP)     |                    |

|            |           | 0x3003A9: P44–P47 Port Function Select Register (pP4_47_CFP)     |                    |

|            |           | 0x3003AA: P50–P53 Port Function Select Register (pP5_03_CFP)     |                    |

|            |           | 0x3003AB: P54–P57 Port Function Select Register (pP5_47_CFP)     |                    |

|            |           | 0x3003AC: P60–P63 Port Function Select Register (pP6_03_CFP)     |                    |

|            |           | 0x3003AD: P04-P07 P011 Function Select Register (pP0_47_CFP)     |                    |

|            |           | 0x3003AF: P74 Port Function Select Register (pP7_4_CFP)          |                    |

|            |           | 0x3003B0: P80–P83 Port Function Select Register (pP8_03_CFP)     |                    |

|            |           | 0x3003B1: P84–P85 Port Function Select Register (pP8_45_CFP)     |                    |

|            |           | 0x3003B2: P90–P93 Port Function Select Register (pP9_03_CFP)     |                    |

|            |           | 0x3003B3: P94–P97 Port Function Select Register (pP9_47_CFP)     |                    |

|            |           | 0x300C20: PA0-PA3 Port Function Select Register (pPA_03_CFP)     | I-3-33             |

|            |           | 0x300C21: PA4 Port Function Select Register (pPA_4_CFP)          | I-3-34             |

|            |           | 0x300C22: PB0-PB3 Port Function Select Register (pPB_03_CFP)     |                    |

|            |           | 0x300C24: PC0–PC3 Port Function Select Register (pPC_03_CFP)     |                    |

|            |           | 0x300C25: PC4-PC7 Port Function Select Register (pPC_47_CFP)     |                    |

|            | 1.3.4 Inp | out/Output Cells and Input/Output Characteristics                | -3-38              |

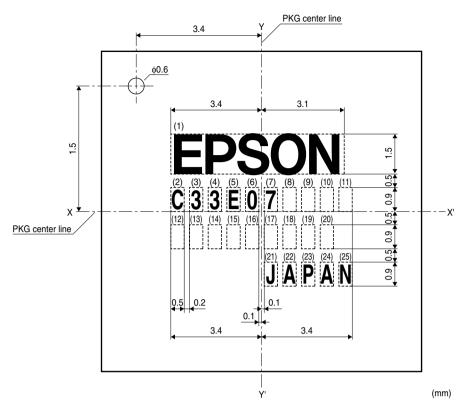

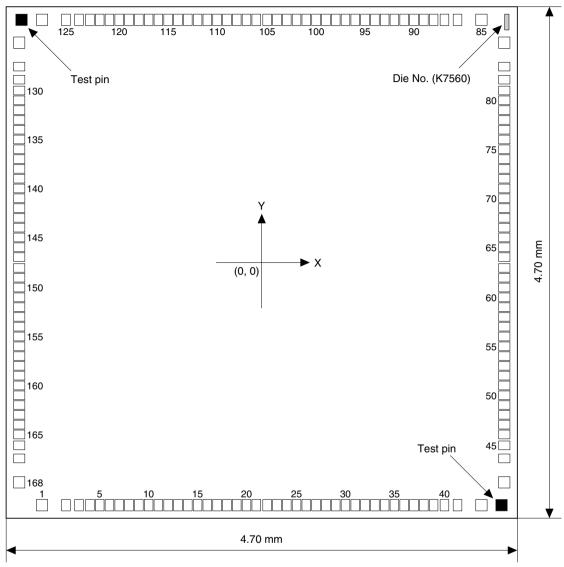

|            | 1.3.5 Pa  | ıckagel                                                          | -3-41              |

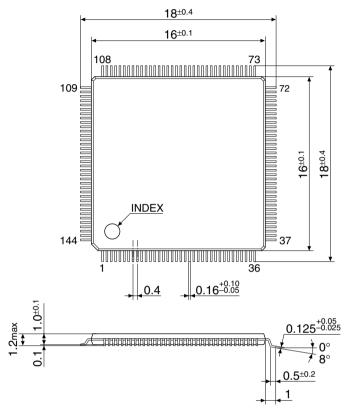

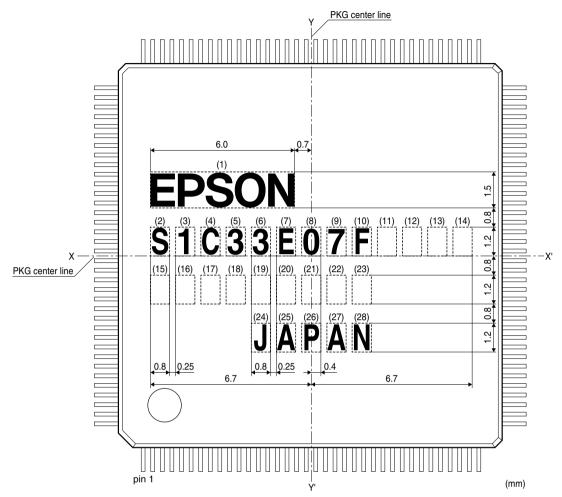

|            | I.        | .3.5.1 TQFP24-144pin PackageI                                    | -3-41              |

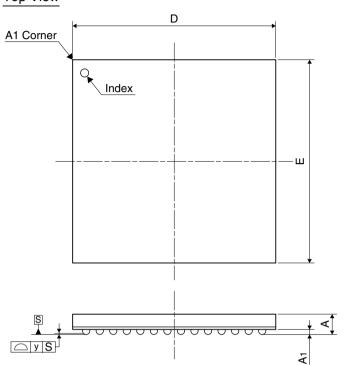

|            | I.        | .3.5.2 PFBGA-180pin PackageI                                     | -3-43              |

|            | I.        | .3.5.3 Thermal Resistance of the Packagel                        | -3-45              |

|            | 1.3.6 Pa  | ld Layoutl                                                       | -3-46              |

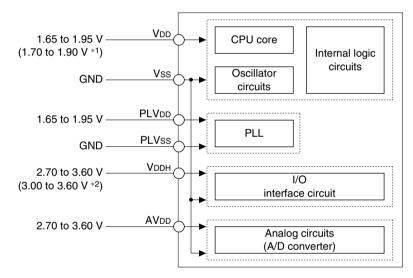

| 1.4        | Power Su  | ıpply                                                            | I-4-1              |

|            |           | ower Supply Pins                                                 |                    |

|            | 1.4.2 Or  | perating Voltage (VDD, Vss)                                      | I-4-2              |

|            |           | ower Supply for PLL (PLVDD, PLVss)                               |                    |

|            |           | ower Supply for I/O Interface (VDDH)                             |                    |

|            |           | ower Supply for Analog Circuits (AVDD)                           |                    |

|            |           |                                                                  |                    |

|            | 1.4.0 Pr  | ecautions on Power Supply                                        | 1 <del>-4-</del> 3 |

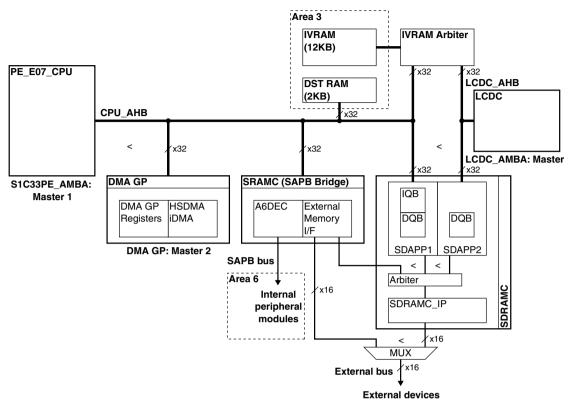

| <b>I.5</b> |         | ore and Bus Architecture                            |        |

|------------|---------|-----------------------------------------------------|--------|

|            | 1.5.1   | Features of the C33 PE Core                         | I-5-1  |

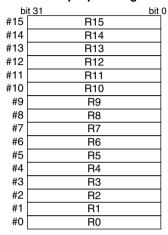

|            | 1.5.2   | CPU Registers                                       | I-5-2  |

|            | 1.5.3   | Instruction Set                                     | I-5-3  |

|            | 1.5.4   | Trap Table                                          | I-5-7  |

|            | 1.5.5   | Power-Down Mode                                     | I-5-9  |

|            | 1.5.6   | Debug Mode                                          | I-5-10 |

|            |         | Bus Architecture                                    |        |

|            |         | I.5.7.1 32-bit High-Speed Bus                       |        |

|            |         | I.5.7.2 SAPB Bus                                    | I-5-12 |

|            |         | I.5.7.3 External Bus                                | I-5-12 |

|            | 1.5.8   | Chip ID                                             | I-5-13 |

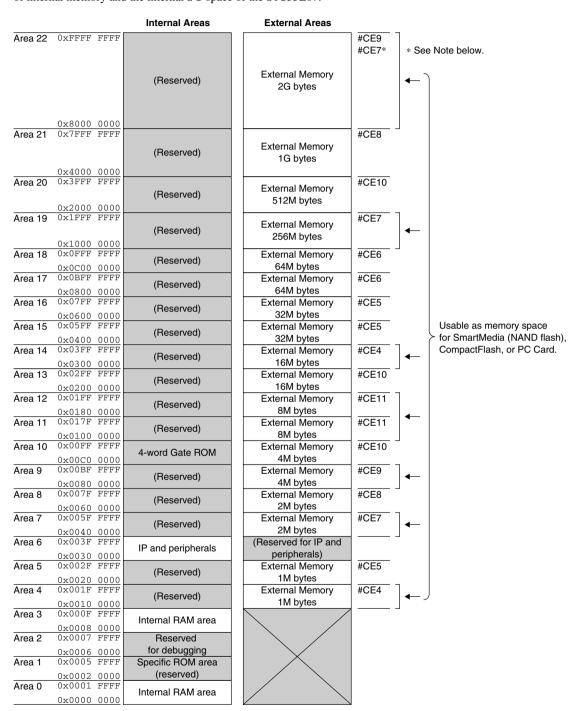

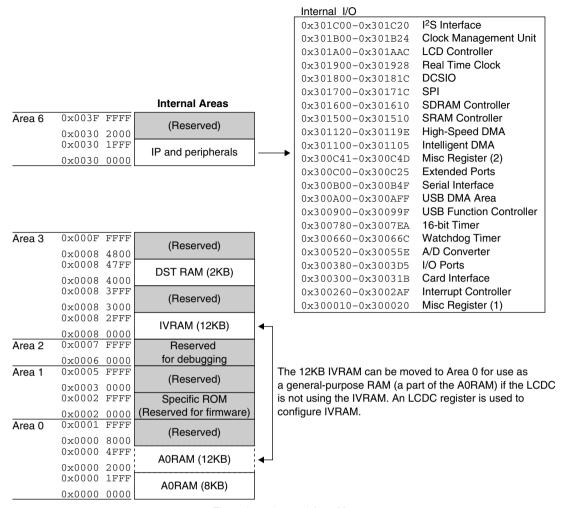

| 1.6        | Memo    | ry Map                                              | l-6-1  |

|            |         | Boot Address and Gate ROM                           |        |

|            |         | Area 0 (A0RAM)                                      |        |

|            |         | Area 1 (Specific ROM for Firmware)                  |        |

|            |         | Area 2 (Debug Area)                                 |        |

|            |         | Area 3 (IVRAM)                                      |        |

|            |         |                                                     |        |

|            |         | Area 3 (DST RAM)                                    |        |

|            |         | Area 6 (I/O Area)                                   |        |

|            |         | External Memory Areas                               |        |

| 1.7        | Electri | cal Characteristics                                 | l-7-1  |

|            | 1.7.1   | Absolute Maximum Rating                             | I-7-1  |

|            | 1.7.2   | Recommended Operating Conditions                    | I-7-1  |

|            | 1.7.3   | DC Characteristics                                  | I-7-2  |

|            | 1.7.4   | Current Consumption                                 | I-7-3  |

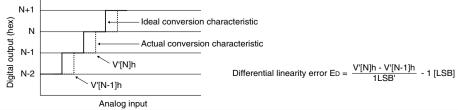

|            | 1.7.5   | A/D Converter Characteristics                       | I-7-5  |

|            | 1.7.6   | Oscillation Characteristics                         | I-7-6  |

|            | 1.7.7   | PLL Characteristics                                 | I-7-7  |

|            | 1.7.8   | AC Characteristics                                  | I-7-8  |

|            |         | I.7.8.1 Symbol Description                          | I-7-8  |

|            |         | I.7.8.2 AC Characteristics Measurement Condition    |        |

|            |         | I.7.8.3 SRAMC AC Characteristic Tables              |        |

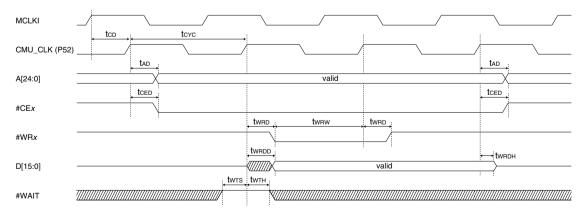

|            |         | I.7.8.4 SRAMC AC Characteristic Timing Charts       |        |

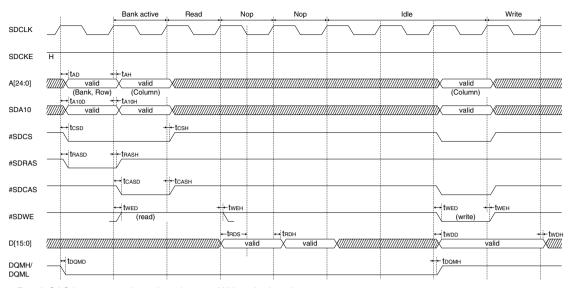

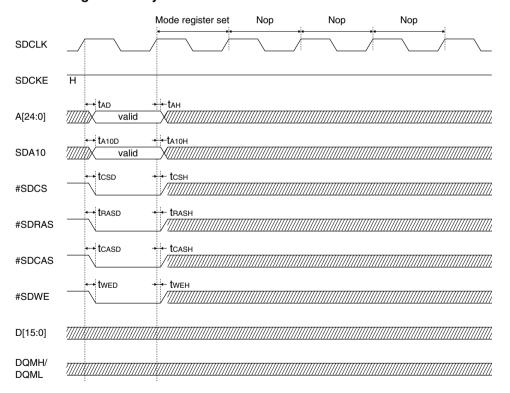

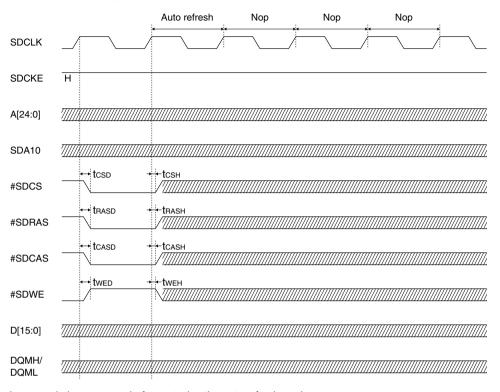

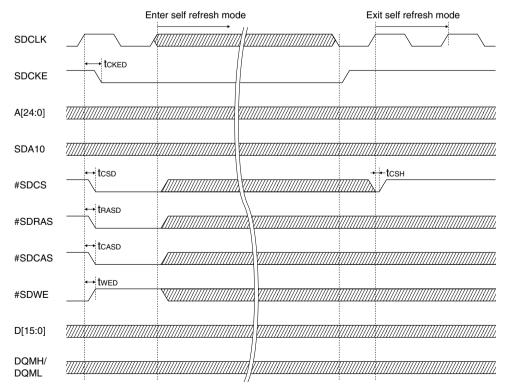

|            |         | I.7.8.5 SDRAM Interface AC Characteristics          |        |

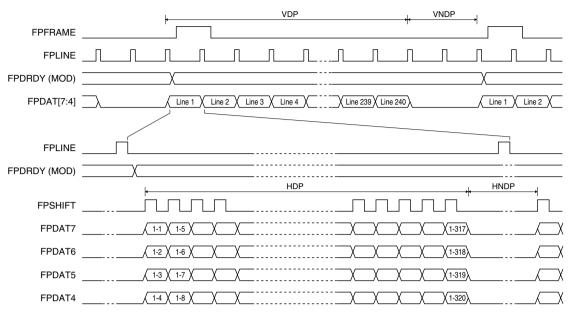

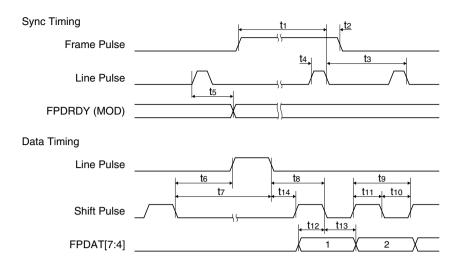

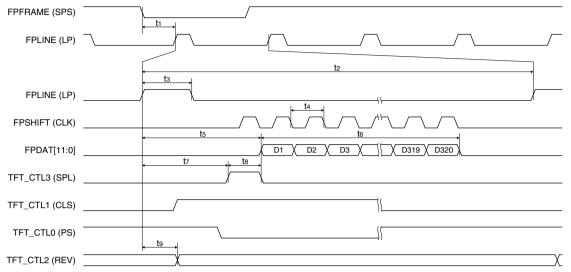

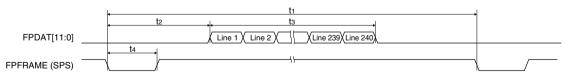

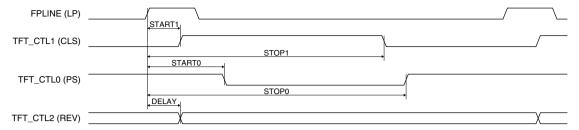

|            | 0       | I.7.8.6 LCDC AC Characteristics                     |        |

|            | 1.7.9   | USB DC and AC Characteristics                       | I-7-27 |

| 1.8        | Basic   | External Wiring Diagram                             | l-8-1  |

| 1.9        | Precau  | utions on Mounting                                  | l-9-1  |

|            |         | -                                                   |        |

| <u>!!_</u> | BO2 I   | MODULES                                             |        |

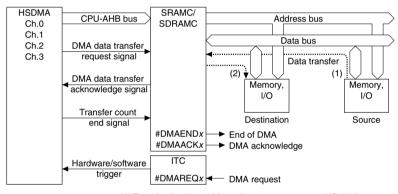

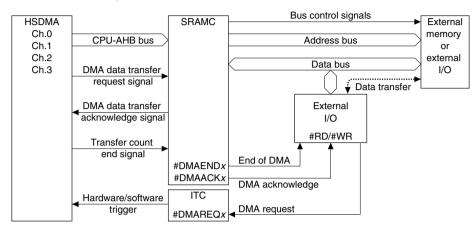

| II.1       | High-   | Speed DMA (HSDMA)                                   | II-1-1 |

|            | II.1.1  | Functional Outline of HSDMA                         | II-1-1 |

|            | II.1.2  | 2 I/O Pins of HSDMA                                 | II-1-5 |

|            | II.1.3  | Programming Control Information                     | II-1-6 |

|            |         | II.1.3.1 Standard Mode and Advanced Mode            |        |

|            |         | II.1.3.2 Sequential Access Time for IDMA and HSDMA  |        |

|            |         | II.1.3.3 Setting the Registers in Dual-Address Mode | II-1-8 |

|             |                                                                                                          | II.1.3.4 Setting the Registers in Single-Address Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . II-1-11                                                                                                                            |

|-------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

|             | II.1.4                                                                                                   | Enabling/Disabling DMA Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .II-1-14                                                                                                                             |

|             |                                                                                                          | Trigger Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                      |

|             |                                                                                                          | Operation of HSDMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                      |

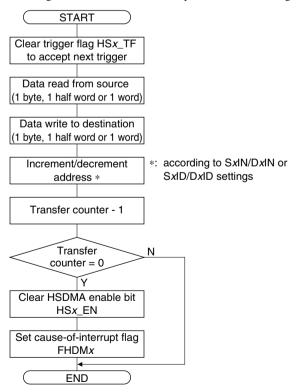

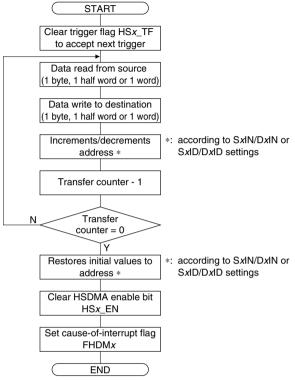

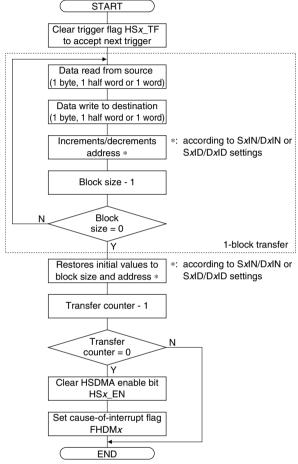

|             |                                                                                                          | II.1.6.1 Operation in Dual-Address Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                      |

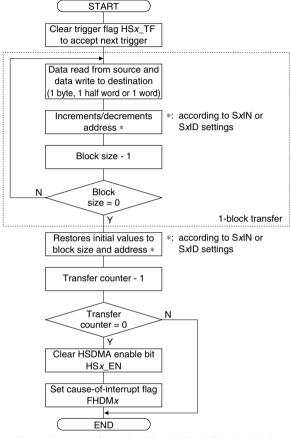

|             |                                                                                                          | II.1.6.2 Operation in Single-Address Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                      |

|             | II.1.7                                                                                                   | Interrupt Function of HSDMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                      |

|             |                                                                                                          | HSDMA Operating Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                      |

|             |                                                                                                          | Details of Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                      |

|             | 11.1.0                                                                                                   | 0x301120–0x301150: HSDMA Ch.x Transfer Counter Registers (pHSx_CNT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                      |

|             |                                                                                                          | 0x301122–0x301152: HSDMA Ch.x Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                      |

|             |                                                                                                          | 0x301124-0x301154: HSDMA Ch.x Low-Order Source Address Setup Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                      |

|             |                                                                                                          | (pHSx_SADR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                      |

|             |                                                                                                          | 0x301126–0x301156: HSDMA Ch.x High-Order Source Address Setup Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | II-1-31                                                                                                                              |

|             |                                                                                                          | (pHSx_DADR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | II-1-33                                                                                                                              |

|             |                                                                                                          | 0x30112A–0x30115A: HSDMA Ch.x High-Order Destination Address Setup Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                      |

|             |                                                                                                          | 0x30112C-0x30115C: HSDMA Ch.x Enable Registers (pHSx_EN)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                      |

|             |                                                                                                          | 0x30112E–0x30115E: HSDMA Ch.x Trigger Flag Registers (pHSx_TF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                      |

|             |                                                                                                          | 0x301162–0x301192: HSDMA Ch.x Control Registers (pHSx_ADVMODE) for ADV mode 0x301164–0x301196: HSDMA Ch.x Source Address Setup Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11-1-38                                                                                                                              |

|             |                                                                                                          | (pHSx_AD_SADR) for ADV mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | II-1-40                                                                                                                              |

|             |                                                                                                          | 0x301168–0x30119A: HSDMA Ch.x Destination Address Setup Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1 40                                                                                                                                 |

|             |                                                                                                          | (pHSx_ADV_DADR) for ADV mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | II-1-42                                                                                                                              |

|             |                                                                                                          | 0x30119C: HSDMA STD/ADV Mode Select Register (pHS_CNTLMODE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                      |

|             |                                                                                                          | 0x30119E: DMA Sequential Access Time Register (pHS_ACCTIME)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                      |

|             | II.1.1                                                                                                   | 9 Precautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . II-1-46                                                                                                                            |

|             |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                      |

| <b>II.2</b> | Intellig                                                                                                 | jent DMA (IDMA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . II-2-1                                                                                                                             |

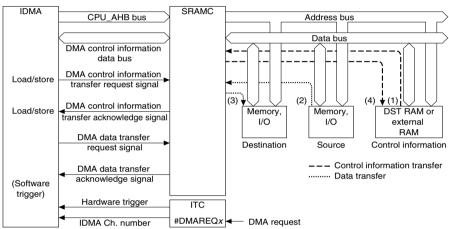

| II.2        | _                                                                                                        | gent DMA (IDMA)  Functional Outline of IDMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                      |

| II.2        | II.2.1                                                                                                   | Functional Outline of IDMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | II-2-1                                                                                                                               |

| II.2        | II.2.1                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | II-2-1<br>II-2-3                                                                                                                     |

| II.2        | II.2.1                                                                                                   | Functional Outline of IDMA  Programming Control Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | II-2-1<br>II-2-3<br>II-2-3                                                                                                           |

| II.2        | II.2.1<br>II.2.2                                                                                         | Functional Outline of IDMA  Programming Control Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | II-2-1<br>II-2-3<br>II-2-3<br>II-2-3                                                                                                 |

| II.2        | II.2.1<br>II.2.2<br>II.2.3                                                                               | Functional Outline of IDMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | II-2-1<br>II-2-3<br>II-2-3<br>II-2-3                                                                                                 |

| II.2        | II.2.1<br>II.2.2<br>II.2.3                                                                               | Functional Outline of IDMA  Programming Control Information  II.2.2.1 Setting the Base Address  II.2.2.2 Control Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | II-2-1<br>II-2-3<br>II-2-3<br>II-2-8<br>II-2-11                                                                                      |

| II.2        | II.2.1<br>II.2.2<br>II.2.3                                                                               | Functional Outline of IDMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | II-2-1<br>II-2-3<br>II-2-3<br>II-2-8<br>. II-2-11<br>. II-2-11                                                                       |

| II.2        | II.2.1<br>II.2.2<br>II.2.3                                                                               | Functional Outline of IDMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | II-2-1<br>II-2-3<br>II-2-3<br>II-2-8<br>II-2-11<br>. II-2-11                                                                         |

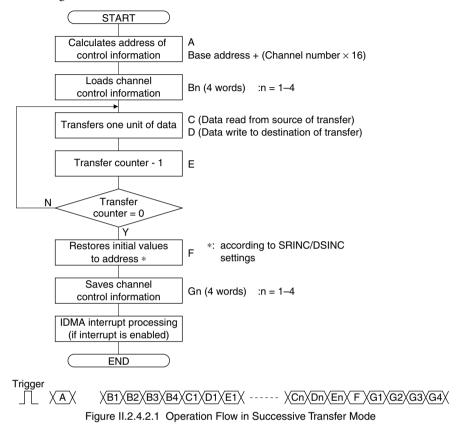

| II.2        | II.2.1<br>II.2.2<br>II.2.3                                                                               | Functional Outline of IDMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | II-2-1<br>II-2-3<br>II-2-3<br>II-2-8<br>II-2-11<br>. II-2-12<br>. II-2-13                                                            |

| II.2        | II.2.1<br>II.2.2<br>II.2.3<br>II.2.4                                                                     | Functional Outline of IDMA  Programming Control Information  II.2.2.1 Setting the Base Address  II.2.2.2 Control Information  IDMA Invocation  Operation of IDMA  II.2.4.1 Single Transfer Mode  II.2.4.2 Successive Transfer Mode  II.2.4.3 Block Transfer Mode                                                                                                                                                                                                                                                                                                                                                                                         | II-2-1<br>II-2-3<br>II-2-3<br>II-2-8<br>.II-2-11<br>.II-2-12<br>.II-2-13                                                             |

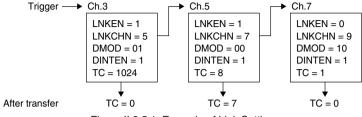

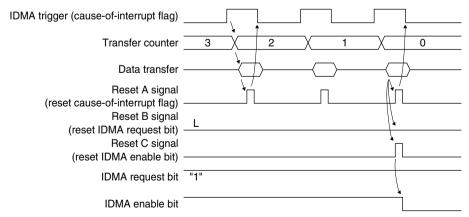

| II.2        | II.2.1<br>II.2.2<br>II.2.3<br>II.2.4                                                                     | Functional Outline of IDMA  Programming Control Information  II.2.2.1 Setting the Base Address  II.2.2.2 Control Information  IDMA Invocation  Operation of IDMA  II.2.4.1 Single Transfer Mode  II.2.4.2 Successive Transfer Mode  II.2.4.3 Block Transfer Mode  II.2.4.4 Cause-of-Interrupt Processing by Trigger Type                                                                                                                                                                                                                                                                                                                                 | II-2-1<br>II-2-3<br>II-2-3<br>II-2-8<br>.II-2-11<br>.II-2-12<br>.II-2-13<br>.II-2-14                                                 |

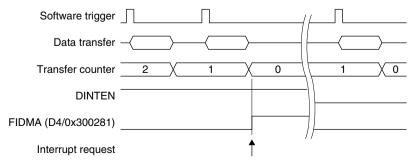

| II.2        | II.2.1<br>II.2.2<br>II.2.3<br>II.2.4<br>II.2.5<br>II.2.6                                                 | Functional Outline of IDMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | II-2-1<br>II-2-3<br>II-2-3<br>II-2-8<br>.II-2-11<br>.II-2-11<br>.II-2-12<br>.II-2-13<br>.II-2-14<br>.II-2-15                         |

| II.2        | II.2.1<br>II.2.2<br>II.2.3<br>II.2.4<br>II.2.5<br>II.2.6                                                 | Functional Outline of IDMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | II-2-1<br>II-2-3<br>II-2-3<br>II-2-8<br>.II-2-11<br>.II-2-12<br>.II-2-13<br>.II-2-14<br>.II-2-15<br>.II-2-16                         |

| II.2        | II.2.1<br>II.2.2<br>II.2.3<br>II.2.4<br>II.2.5<br>II.2.6                                                 | Functional Outline of IDMA  Programming Control Information  II.2.2.1 Setting the Base Address  II.2.2.2 Control Information  IDMA Invocation  Operation of IDMA  II.2.4.1 Single Transfer Mode  II.2.4.2 Successive Transfer Mode  II.2.4.3 Block Transfer Mode  II.2.4.4 Cause-of-Interrupt Processing by Trigger Type  Linking  Interrupt Function of Intelligent DMA  Details of Control Registers  0x301100: IDMA Base Address Register 0 (pIDMABASE)  0x301102: IDMA Base Address Register 1                                                                                                                                                       | II-2-1<br>II-2-3<br>II-2-3<br>II-2-8<br>.II-2-11<br>.II-2-13<br>.II-2-14<br>.II-2-16<br>.II-2-17<br>.II-2-18                         |

| II.2        | II.2.1<br>II.2.2<br>II.2.3<br>II.2.4<br>II.2.5<br>II.2.6                                                 | Functional Outline of IDMA  Programming Control Information  II.2.2.1 Setting the Base Address  II.2.2.2 Control Information  IDMA Invocation  Operation of IDMA  II.2.4.1 Single Transfer Mode  II.2.4.2 Successive Transfer Mode  II.2.4.3 Block Transfer Mode  II.2.4.4 Cause-of-Interrupt Processing by Trigger Type  Linking.  Interrupt Function of Intelligent DMA  Details of Control Registers  0x301100: IDMA Base Address Register 0 (pIDMABASE)  0x301102: IDMA Base Address Register 1  0x301104: IDMA Start Register (pIDMA_START)                                                                                                         | II-2-1<br>II-2-3<br>II-2-3<br>II-2-8<br>.II-2-11<br>.II-2-12<br>.II-2-13<br>.II-2-14<br>.II-2-16<br>.II-2-16<br>.II-2-18<br>.II-2-18 |

| II.2        | II.2.1<br>II.2.2<br>II.2.3<br>II.2.4<br>II.2.5<br>II.2.6<br>II.2.7                                       | Functional Outline of IDMA  Programming Control Information  II.2.2.1 Setting the Base Address  II.2.2.2 Control Information  IDMA Invocation  Operation of IDMA  II.2.4.1 Single Transfer Mode  II.2.4.2 Successive Transfer Mode  II.2.4.3 Block Transfer Mode  II.2.4.4 Cause-of-Interrupt Processing by Trigger Type  Linking  Interrupt Function of Intelligent DMA  Details of Control Registers  0x301100: IDMA Base Address Register 0 (pIDMABASE)  0x301102: IDMA Base Address Register 1  0x301104: IDMA Start Register (pIDMA_START)  0x301105: IDMA Enable Register (pIDMA_EN)                                                               | II-2-1II-2-3II-2-3II-2-8II-2-11 .II-2-12 .II-2-14 .II-2-15 .II-2-18 .II-2-18 .II-2-19II-2-19                                         |

| II.2        | II.2.1<br>II.2.2<br>II.2.3<br>II.2.4<br>II.2.5<br>II.2.6<br>II.2.7                                       | Functional Outline of IDMA  Programming Control Information  II.2.2.1 Setting the Base Address  II.2.2.2 Control Information  IDMA Invocation  Operation of IDMA  II.2.4.1 Single Transfer Mode  II.2.4.2 Successive Transfer Mode  II.2.4.3 Block Transfer Mode  II.2.4.4 Cause-of-Interrupt Processing by Trigger Type  Linking.  Interrupt Function of Intelligent DMA  Details of Control Registers  0x301100: IDMA Base Address Register 0 (pIDMABASE)  0x301102: IDMA Base Address Register 1  0x301104: IDMA Start Register (pIDMA_START)                                                                                                         | II-2-1II-2-3II-2-3II-2-8II-2-11 .II-2-12 .II-2-14 .II-2-15 .II-2-16 .II-2-18II-2-18II-2-19II-2-20                                    |

|             | II.2.1<br>II.2.2<br>II.2.3<br>II.2.4<br>II.2.5<br>II.2.6<br>II.2.7                                       | Functional Outline of IDMA  Programming Control Information  II.2.2.1 Setting the Base Address  II.2.2.2 Control Information  IDMA Invocation  Operation of IDMA  II.2.4.1 Single Transfer Mode  II.2.4.2 Successive Transfer Mode  II.2.4.3 Block Transfer Mode  II.2.4.4 Cause-of-Interrupt Processing by Trigger Type  Linking  Interrupt Function of Intelligent DMA  Details of Control Registers  0x301100: IDMA Base Address Register 0 (pIDMABASE)  0x301102: IDMA Base Address Register 1  0x301104: IDMA Start Register (pIDMA_START)  0x301105: IDMA Enable Register (pIDMA_EN)                                                               | II-2-1II-2-3II-2-3II-2-8 .II-2-11 .II-2-12 .II-2-13 .II-2-15 .II-2-16 .II-2-18II-2-18II-2-19II-2-19                                  |

|             | II.2.1<br>II.2.2<br>II.2.3<br>II.2.4<br>II.2.5<br>II.2.6<br>II.2.7                                       | Functional Outline of IDMA  Programming Control Information  II.2.2.1 Setting the Base Address  II.2.2.2 Control Information  IDMA Invocation  Operation of IDMA  II.2.4.1 Single Transfer Mode  II.2.4.2 Successive Transfer Mode  II.2.4.3 Block Transfer Mode  II.2.4.4 Cause-of-Interrupt Processing by Trigger Type  Linking  Interrupt Function of Intelligent DMA  Details of Control Registers  0x301100: IDMA Base Address Register 0 (pIDMABASE)  0x301102: IDMA Base Address Register 1  0x301104: IDMA Start Register (pIDMA_START)  0x301105: IDMA Enable Register (pIDMA_EN)  Precautions                                                  | II-2-1II-2-3II-2-3II-2-8II-2-11 .II-2-12 .II-2-14 .II-2-15 .II-2-18II-2-19II-2-20 .II-2-21                                           |

|             | II.2.1<br>II.2.2<br>II.2.3<br>II.2.4<br>II.2.5<br>II.2.6<br>II.2.7<br>II.2.8<br>SRAM<br>II.3.1           | Functional Outline of IDMA Programming Control Information II.2.2.1 Setting the Base Address II.2.2.2 Control Information IDMA Invocation Operation of IDMA II.2.4.1 Single Transfer Mode II.2.4.2 Successive Transfer Mode II.2.4.3 Block Transfer Mode II.2.4.4 Cause-of-Interrupt Processing by Trigger Type Linking Interrupt Function of Intelligent DMA Details of Control Registers 0x301100: IDMA Base Address Register 0 (pIDMABASE) 0x301102: IDMA Base Address Register 1 0x301104: IDMA Start Register (pIDMA_START) 0x301105: IDMA Enable Register (pIDMA_EN) Precautions  Controller (SRAMC)                                               | II-2-1II-2-3II-2-3II-2-8II-2-11 .II-2-12 .II-2-14 .II-2-15 .II-2-16 .II-2-19II-2-20 .II-2-21                                         |

|             | II.2.1<br>II.2.2<br>II.2.3<br>II.2.4<br>II.2.5<br>II.2.6<br>II.2.7<br>II.2.8<br>SRAM<br>II.3.1<br>II.3.2 | Functional Outline of IDMA  Programming Control Information  III.2.2.1 Setting the Base Address  III.2.2.2 Control Information  IDMA Invocation  Operation of IDMA  III.2.4.1 Single Transfer Mode  III.2.4.2 Successive Transfer Mode  III.2.4.3 Block Transfer Mode  III.2.4.4 Cause-of-Interrupt Processing by Trigger Type  Linking  Interrupt Function of Intelligent DMA  Details of Control Registers  0x301100: IDMA Base Address Register 0 (pIDMABASE)  0x301102: IDMA Base Address Register 1  0x301104: IDMA Start Register (pIDMA_START)  0x301105: IDMA Enable Register (pIDMA_EN)  Precautions  Controller (SRAMC)  Overview of the SRAMC | II-2-1II-2-3II-2-8II-2-8 .II-2-11 .II-2-12 .II-2-13 .II-2-15 .II-2-16 .II-2-18II-2-19II-2-21II-2-21II-3-1                            |

|             | II.2.1<br>II.2.2<br>II.2.3<br>II.2.4<br>II.2.5<br>II.2.6<br>II.2.7<br>II.2.8<br>SRAM<br>II.3.1<br>II.3.2 | Functional Outline of IDMA  Programming Control Information  II.2.2.1 Setting the Base Address  II.2.2.2 Control Information  IDMA Invocation  Operation of IDMA  II.2.4.1 Single Transfer Mode  II.2.4.2 Successive Transfer Mode  II.2.4.3 Block Transfer Mode  II.2.4.4 Cause-of-Interrupt Processing by Trigger Type  Linking  Interrupt Function of Intelligent DMA  Details of Control Registers  0x301100: IDMA Base Address Register 0 (pIDMABASE)  0x301102: IDMA Base Address Register 1  0x301104: IDMA Start Register (pIDMA_START)  0x301105: IDMA Enable Register (pIDMA_EN)  Precautions  Controller (SRAMC)                              | II-2-1II-2-3II-2-8II-2-11 .II-2-12 .II-2-13 .II-2-16 .II-2-16 .II-2-18II-2-18II-2-19II-2-20II-3-1II-3-1II-3-1                        |

|          | II.3.4  | Connection of External Devices and Bus Operation                   |         |

|----------|---------|--------------------------------------------------------------------|---------|

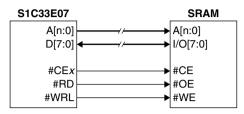

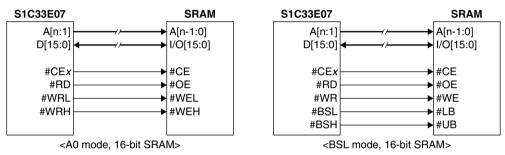

|          |         | II.3.4.1 Connecting External Devices                               |         |

|          |         | II.3.4.2 Data Configuration in Memory                              |         |

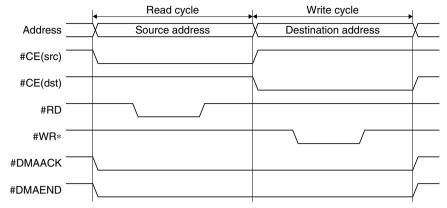

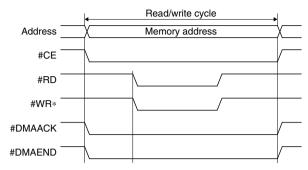

|          |         | II.3.4.3 External Bus Operation                                    |         |

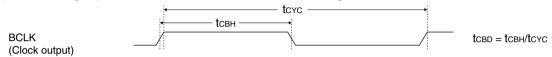

|          | II.3.5  | SRAMC Operating Clock and Bus Clock                                | II-3-9  |

|          |         | II.3.5.1 Operating Clock of the SRAMC                              |         |

|          |         | II.3.5.2 Generation of the Bus Clock                               | II-3-10 |

|          |         | II.3.5.3 External Output of the Bus Clock                          | II-3-10 |

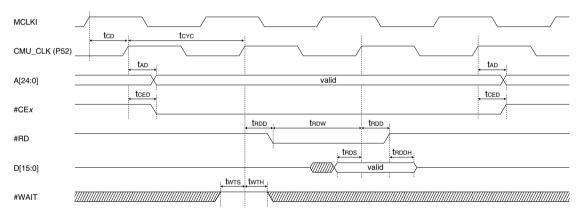

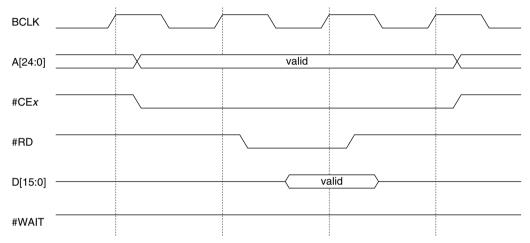

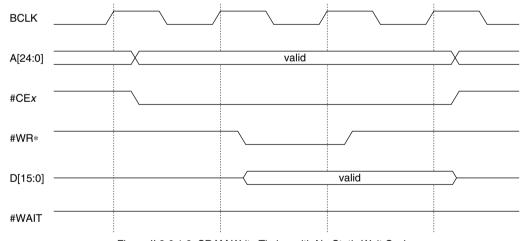

|          | II.3.6  | Bus Access Timing Chart                                            | II-3-11 |

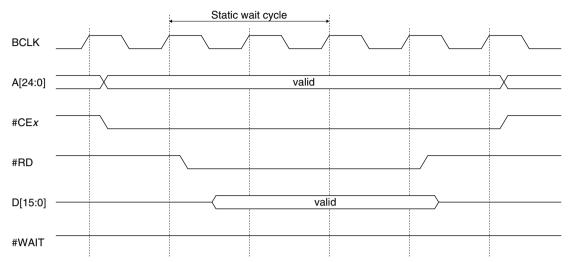

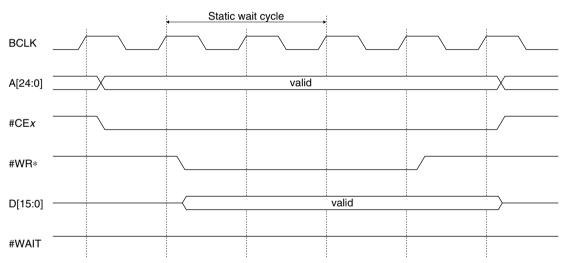

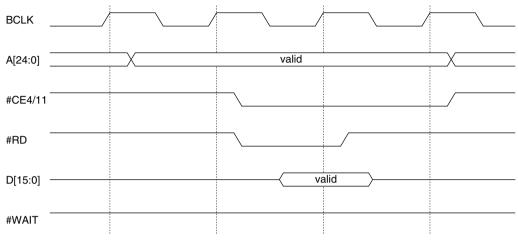

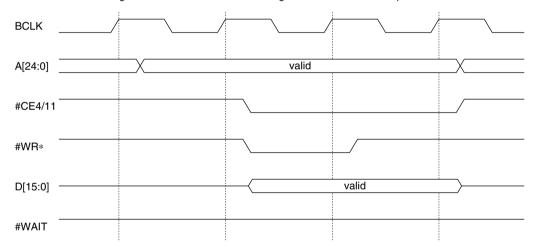

|          |         | II.3.6.1 SRAM Read/Write Timings with No External #WAIT            | II-3-11 |

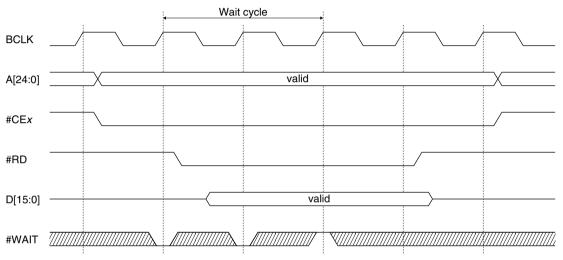

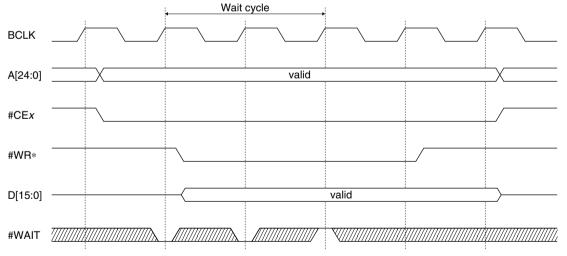

|          |         | II.3.6.2 SRAM Read/Write Timings with External #WAIT               | II-3-13 |

|          |         | II.3.6.3 SRAM Read/Write Timings with #CE4/#CE11 Setup Time        | II-3-14 |

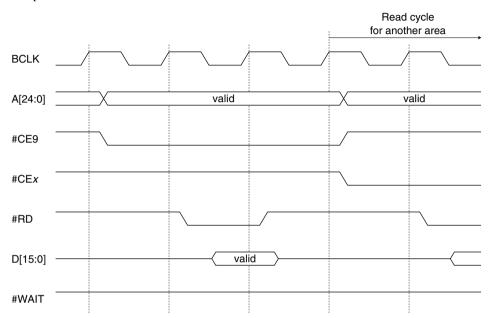

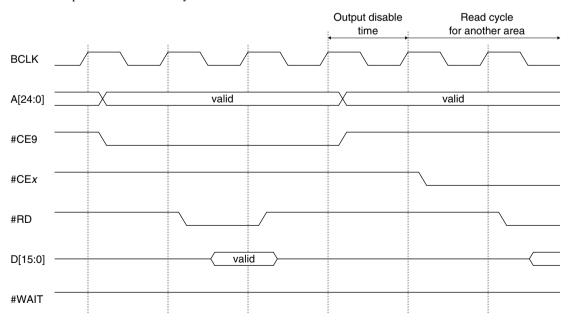

|          |         | II.3.6.4 SRAM Read Timings with #CE9 Output Disable Time           | II-3-15 |

|          | 11.3.7  | Control Register Details                                           | II-3-16 |

|          |         | 0x301500: BCLK and Setup Time Control Register (pSRAMC_BCLK_SETUP) | II-3-17 |

|          |         | 0x301504: Wait Control Register (pSRAMC_SWAIT)                     |         |

|          |         | 0x301508: Device Size Setup Register (pSRAMC_SLV_SIZE)             |         |

|          |         | 0x30150C: Device Type Setup Register (pSRAMC_A0_BSL)               |         |

|          |         | 0x301510: Area Location Setup Register (pSRAMC_ALS)                |         |

|          | II.3.8  | Precautions                                                        | II-3-23 |

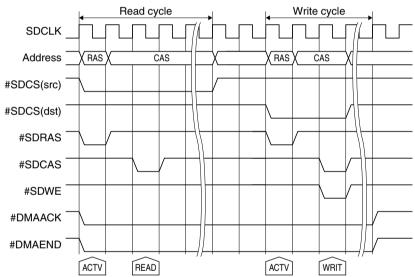

| II.4     | SDRAM   | M Controller (SDRAMC)                                              | II-4-1  |

|          |         | SDRAM Interface                                                    |         |

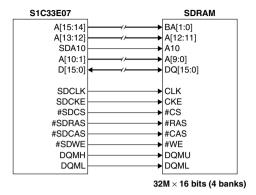

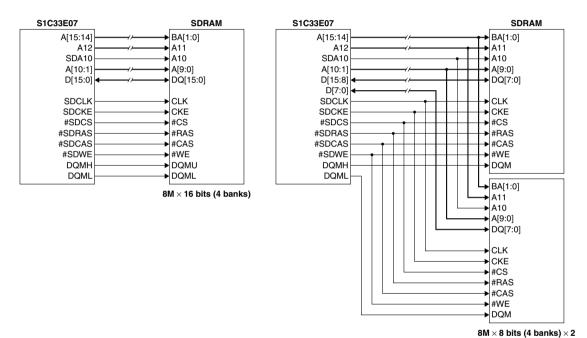

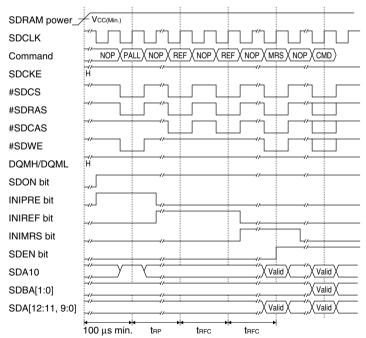

|          |         | II.4.1.1 Overview of the SDRAM Interface                           |         |

|          |         | II.4.1.2 SDRAMC Pins                                               |         |

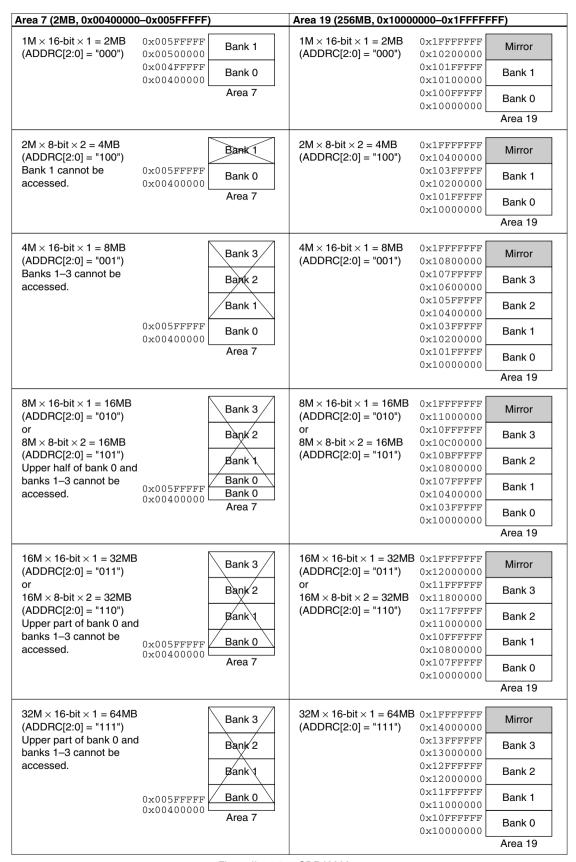

|          |         | II.4.1.3 Configuration of SDRAM                                    |         |

|          |         | II.4.1.4 SDRAMC Operating Clock and SDRAM Clock                    |         |

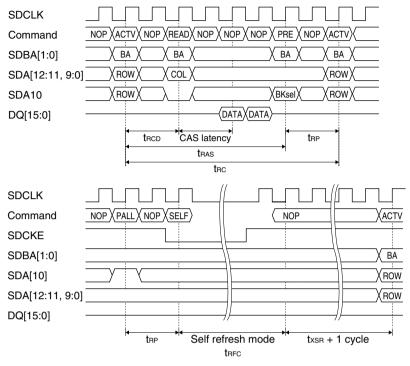

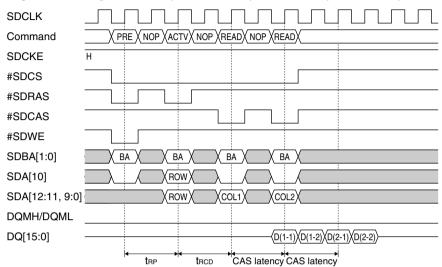

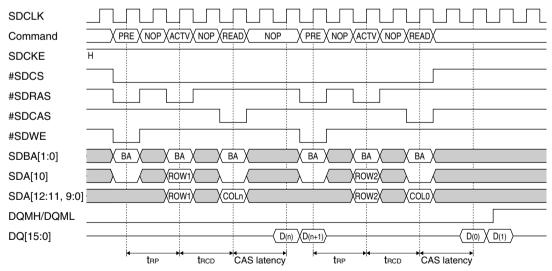

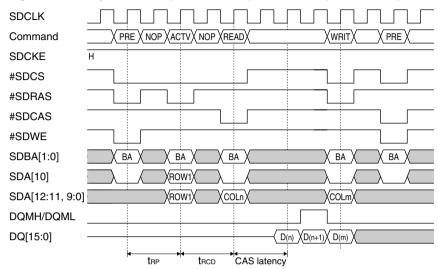

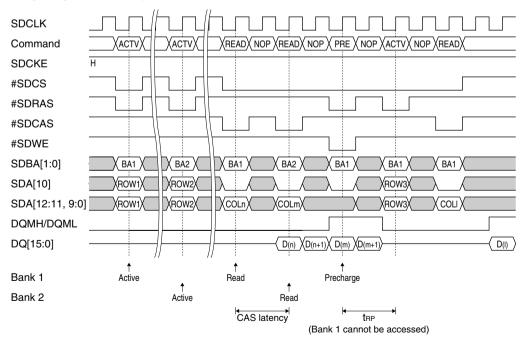

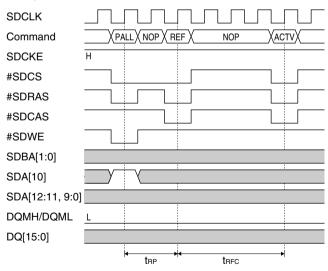

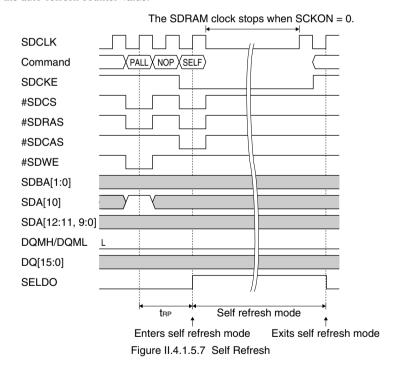

|          |         | II.4.1.5 Control and Operation of SDRAM Interface                  |         |

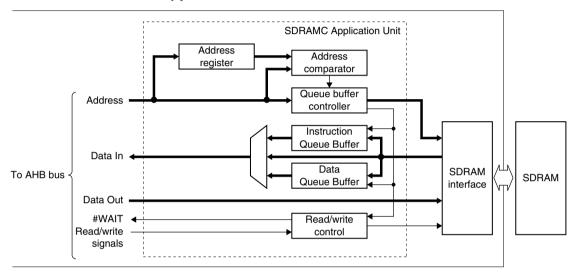

|          | 1142    | Instruction/Data Queue Buffers                                     |         |

|          |         | II.4.2.1 Overview                                                  |         |

|          |         | II.4.2.2 IQB (Instruction Queue Buffer)                            |         |

|          |         | II.4.2.3 DQB (Data Queue Buffer)                                   |         |

|          |         | II.4.2.4 Operations using IQB/DQB                                  |         |

|          | II.4.3  | Bus Arbiter                                                        |         |

|          |         | II.4.3.1 Overview                                                  |         |

|          |         | II.4.3.2 Controlling the Bus Arbiter                               |         |

|          | 11 4 4  | Control Register Details                                           |         |

|          |         | 0x301600: SDRAM Initial Register (pSDRAMC_INI)                     | II-4-23 |

|          |         | 0x301604: SDRAM Configuration Register (pSDRAMC_CTL)               |         |

|          |         | 0x301608: SDRAM Refresh Register (pSDRAMC_REF)                     | II-4-27 |

|          |         | 0x301610: SDRAM Application Configuration Register (pSDRAMC_APP)   | II-4-29 |

|          | 11.4.5  | Precautions                                                        | II-4-31 |

|          | DEDID   | NUEDAL MODULES 1 (SVSTEM)                                          |         |

| <u> </u> | PEKIP   | PHERAL MODULES 1 (SYSTEM)                                          |         |

| III.1    | Clock   | Management Unit (CMU)                                              | III-1-1 |

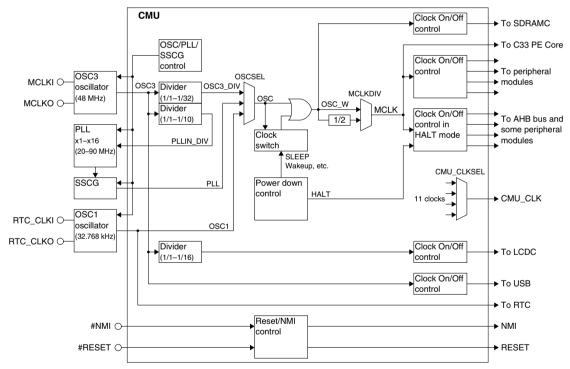

|          | III.1.1 | Overview of the CMU                                                | III-1-1 |

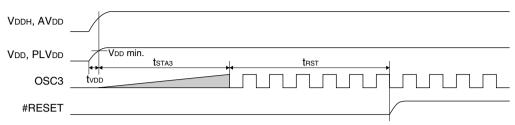

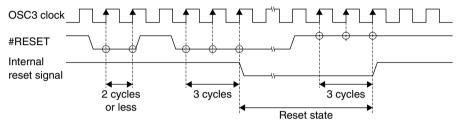

|          | III.1.2 | Reset Input and Initial Reset                                      | III-1-2 |

|          | _       | III.1.2.1 Initial Reset Pin                                        |         |

|          |         | III.1.2.2 Initial Reset Status                                     |         |

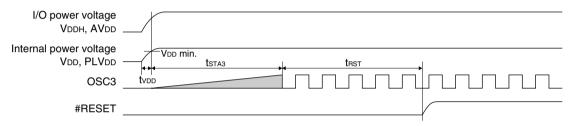

|          |         | III.1.2.3 Power-on Reset                                           |         |

|          |         | III.1.2.4 Precautions to be Taken during Initial Reset             |         |

|          |         | III. 1.2.4 Frecautions to be taken during initial neset            | III-1-4 |

|          | III.1.3 | NMI Input                                                          |         |

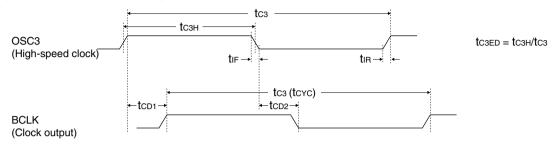

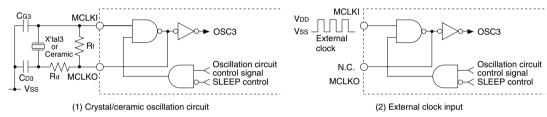

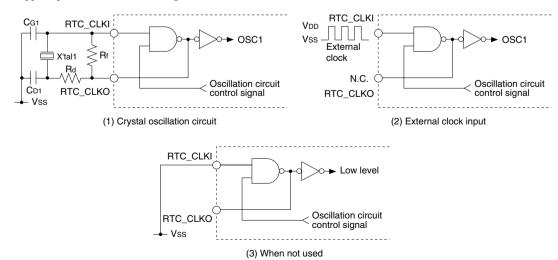

|       | III.1.5.1 OSC3 Oscillator Circuit                              |                       |

|-------|----------------------------------------------------------------|-----------------------|

|       | III.1.5.2 Setting the OSC3 Divider                             |                       |

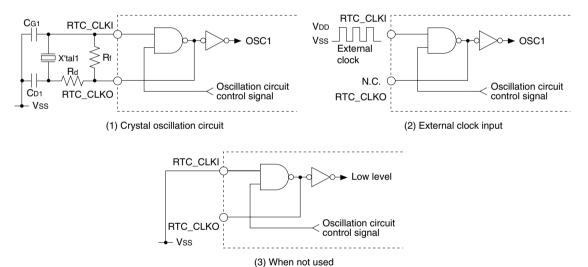

|       | III.1.5.3 OSC1 Oscillator Circuit                              | III-1-8               |

|       | III.1.6 Controlling the PLL                                    |                       |

|       | III.1.6.1 On/Off Control of the PLL                            |                       |

|       | III.1.6.2 Selecting the PLL Input Clock                        | III-1-10              |

|       | III.1.6.3 Setting the Frequency Multiplication Rate            | III-1-11              |

|       | III.1.6.4 Other PLL Settings                                   |                       |

|       | III.1.6.5 Power Supply for PLL                                 |                       |

|       | III.1.7 Control of the SSCG                                    |                       |

|       | III.1.7.1 Turning the SSCG On/Off                              |                       |

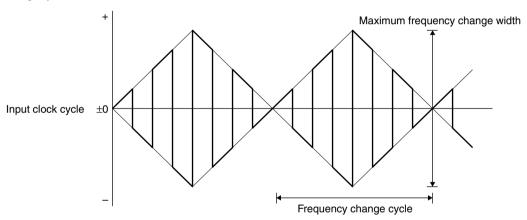

|       | III.1.7.2 Setting SS Modulation Parameters                     | III-1-15              |

|       | III.1.8 Setting the Main System Clock (MCLK)                   | III-1-16              |

|       | III.1.9 Controlling Clock Supply                               | III-1-17              |

|       | III.1.9.1 MCLK Clock Supply to Each Module                     | III-1-17              |

|       | III.1.9.2 Automatic Clock Control in HALT Mode                 | III-1-17              |

|       | III.1.9.3 Clock Supply to the LCDC                             | III-1-18              |

|       | III.1.9.4 Clock Supply to the SDRAMC                           | III-1-19              |

|       | III.1.9.5 Clock Supply to the SRAMC                            | III-1-19              |

|       | III.1.9.6 Clock Supply to the GPIO                             | III-1-20              |

|       | III.1.9.7 Clock Supply to the EFSIO                            | III-1-20              |

|       | III.1.9.8 Clock Supply to the USB                              | III-1-20              |

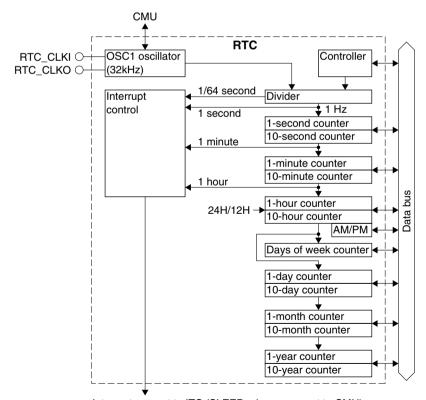

|       | III.1.9.9 Clock Supply to the RTC                              | III-1-21              |

|       | III.1.10 Setting the External Clock Output (CMU_CLK)           | III-1-22              |

|       | III.1.11 Standby Modes                                         | III-1-23              |

|       | III.1.11.1 HALT Mode                                           | III-1-23              |

|       | III.1.11.2 SLEEP Mode                                          | III-1-23              |

|       | III.1.11.3 Precautions                                         | III-1-25              |

|       | III.1.12 Clock Setup Procedure                                 | III-1-26              |

|       | III.1.12.1 Changing the Clock Source from OSC3 to PLL          |                       |

|       | III.1.12.2 Changing the Clock Source from PLL to OSC3,         |                       |

|       | then Turning Off the PLL                                       | III-1-27              |

|       | III.1.12.3 Changing the Clock Source from OSC3 or PLL to OSC1, |                       |

|       | then Turning Off OSC3 and PLL                                  | III-1-28              |

|       | III.1.12.4 Changing the Clock Source from OSC1 to OSC3         | III-1-29              |

|       | III.1.12.5 Changing the Clock Source from OSC1 to PLL          | III-1-30              |

|       | III.1.12.6 Turning Off OSC3 during SLEEP                       | III-1-31              |

|       | III.1.12.7 SLEEP Keeping Oscillation On (without Clock Change) | III-1-32              |

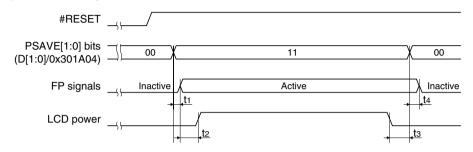

|       | III.1.13 Power-Down Control                                    | III-1-33              |

|       | III.1.14 Details of Control Registers                          | III-1-34              |

|       | 0x301B00: Gated Clock Control Register 0 (pCMU_GATEDCLK0)      |                       |

|       | 0x301B04: Gated Clock Control Register 1 (pCMU_GATEDCLK1)      |                       |

|       | 0x301B08: System Clock Control Register (pCMU_CLKCNTL)         |                       |

|       | 0x301B0C: PLL Control Register (pCMU_PLL)                      |                       |

|       | 0x301B10: SSCG Macro Control Register (pCMU_SSCG)              |                       |

|       | 0x301B14: Clock Option Register (pCMU_OPT)                     |                       |

|       | III.1.15 Precautions                                           |                       |

| III o | Interrupt Controller (ITC)                                     |                       |

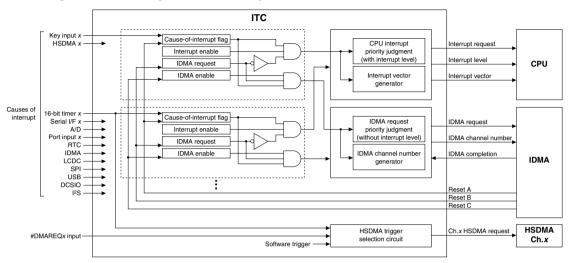

| 111.2 | III.2.1 Outline of Interrupt Functions                         |                       |

|       | III.2.1 Outline of Interrupt Functions                         |                       |

|       | III.2.1.2 Causes of Interrupt and Intelligent DMA              |                       |

| vi    |                                                                | BE07 TECHNICAL MANUAL |

|       | Come Eposit Corporation                                        |                       |

|         | III.2.1.3 Nonmaskable Interrupt (NMI)                                              | III-2-4    |

|---------|------------------------------------------------------------------------------------|------------|

|         | III.2.1.4 Interrupt Processing by the CPU                                          | III-2-4    |

|         | III.2.1.5 Clearing Standby Mode by Interrupts                                      | III-2-4    |

| III.2.2 | Trap Table                                                                         | III-2-6    |

|         | ITC Operating Clock                                                                |            |

|         | Control of Maskable Interrupts                                                     |            |

| 111.2.4 | III.2.4.1 Structure of the Interrupt Controller                                    |            |

|         | ·                                                                                  |            |

|         | III.2.4.2 Processor Status Register (PSR)                                          |            |

|         | III.2.4.3 Cause-of-Interrupt Flag and Interrupt Enable Register                    |            |

|         | III.2.4.4 Interrupt Priority Register and Interrupt Levels                         |            |

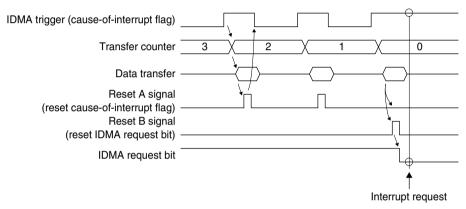

| III.2.5 | IDMA Invocation                                                                    | . III-2-11 |

| III.2.6 | HSDMA Invocation                                                                   | . III-2-13 |

| III.2.7 | Details of Control Registers                                                       | . III-2-14 |

|         | 0x300260: Port Input 0–1 Interrupt Priority Register (pINT_PP01L)                  | III-2-16   |

|         | 0x300261: Port Input 2–3 Interrupt Priority Register (pINT_PP23L)                  |            |

|         | 0x300262: Key Input Interrupt Priority Register (pINT_PK01L)                       |            |

|         | 0x300263: HSDMA Ch.0–1 Interrupt Priority Register (pINT_PHSD01L)                  |            |

|         | 0x300264: HSDMA Ch.2–3 Interrupt Priority Register (pINT_PHSD23L)                  |            |

|         | 0x300265: IDMA Interrupt Priority Register (pINT_PDM)                              |            |

|         | 0x300266: 16-bit Timer 0–1 Interrupt Priority Register (pINT_P16T01)               |            |

|         | 0x300267: 16-bit Timer 2–3 Interrupt Priority Register (pINT_P16T23)               |            |

|         | 0x300268: 16-bit Timer 4–5 Interrupt Priority Register (pINT_P16T45)               |            |

|         | 0x300269: LCDC, Serial I/F Ch.0 Interrupt Priority Register (pINT_PLCDC_PSI00)     |            |

|         | 0x30026A: Serial I/F Ch.1, A/D Interrupt Priority Register (pINT_PSI01_PAD)        |            |

|         | 0x30026B: RTC Interrupt Priority Register (pINT_PRTC)                              |            |

|         | 0x30026C: Port Input 4–5 Interrupt Priority Register (pINT_PP45L)                  | III-2-28   |

|         | 0x30026D: Port Input 6–7 Interrupt Priority Register (pINT_PP67L)                  |            |

|         | 0x30026E: Serial I/F Ch.2, SPI Interrupt Priority Register (pINT_PSI02_PSPI)       |            |

|         | 0x300270: Key Input, Port Input 0–3 Interrupt Enable Register (pINT_EK01_EP03)     |            |

|         | 0x300271: DMA Interrupt Enable Register (pINT_EDMA)                                |            |

|         | 0x300272: 16-bit Timer 0–1 Interrupt Enable Register (pINT_E16T01)                 |            |

|         | 0x300273: 16-bit Timer 2–3 Interrupt Enable Register (pINT_E16T23)                 |            |

|         | 0x300274: 16-bit Timer 4–5 Interrupt Enable Register (pINT_E16T45)                 |            |

|         | 0x300276: Serial I/F Ch.0-1 Interrupt Enable Register (pINT_ESIF01)                |            |

|         | 0x300277: Port Input 4–7, RTC, A/D Interrupt Enable Register (pINT_EP47_ERTC_EAD)  | III-2-37   |

|         | 0x300278: LCDC Interrupt Enable Register (pINT_ELCDC)                              |            |