# CMOS 16-BIT SINGLE CHIP MICROCONTROLLER S1C17554/564 Technical Manual

#### NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of Economy, Trade and Industry or other approval from another government agency.

All brands or product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

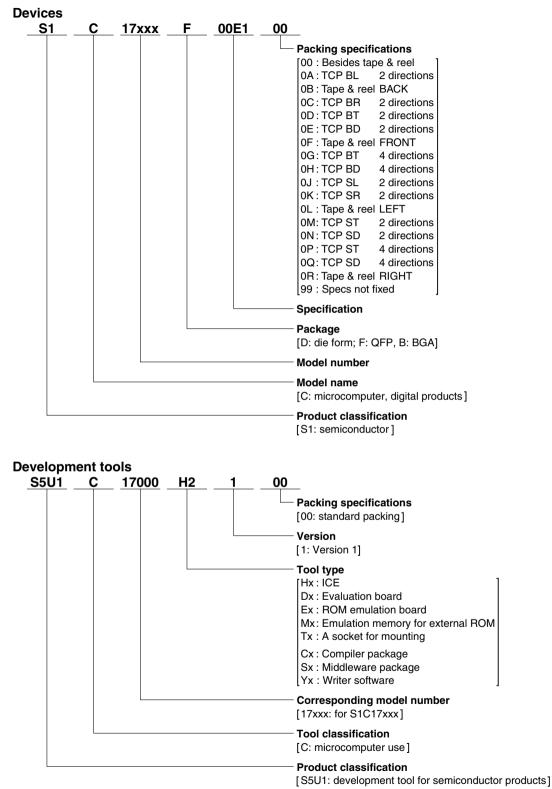

### Configuration of product number

| 1 | Overvie | ew                                                                    | .1-1 |

|---|---------|-----------------------------------------------------------------------|------|

|   | 1.1     | Features                                                              | .1-1 |

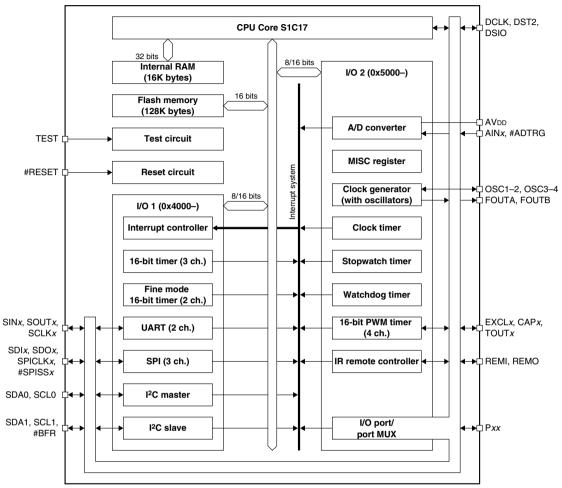

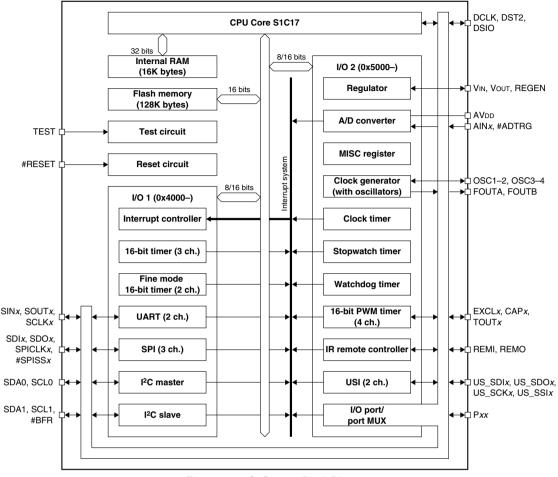

|   | 1.2     | Block Diagram                                                         | .1-3 |

|   | 1.3     | Pins                                                                  | .1-5 |

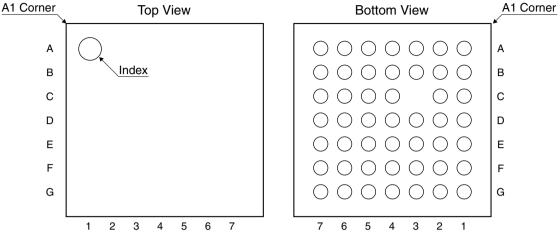

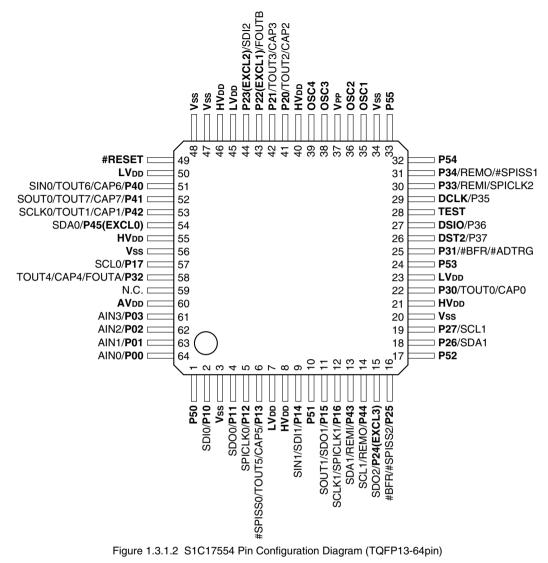

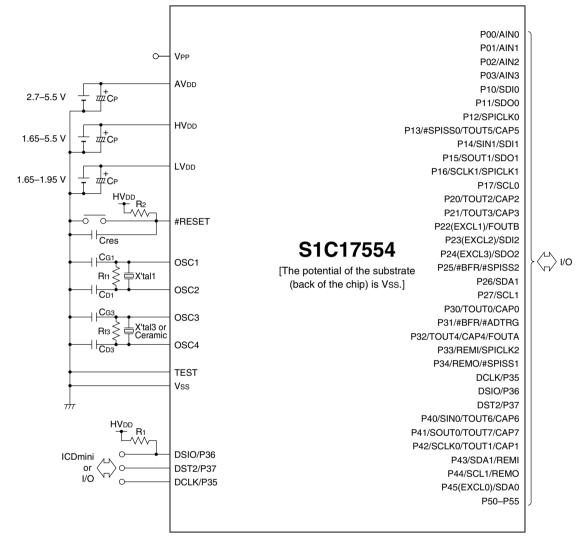

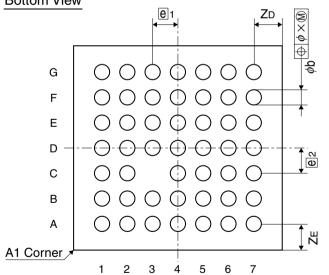

|   |         | 1.3.1 S1C17554 Pin Configuration Diagrams                             | .1-5 |

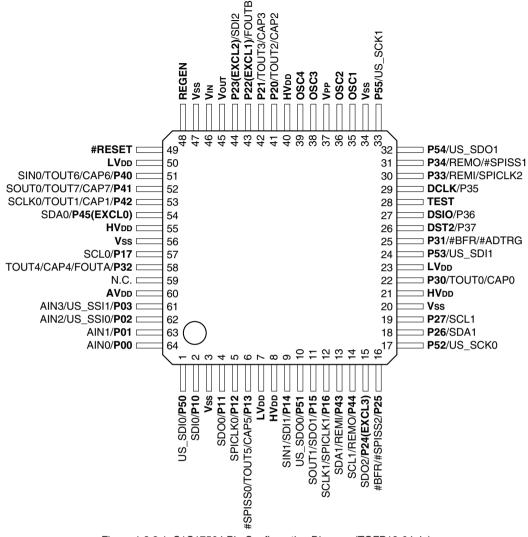

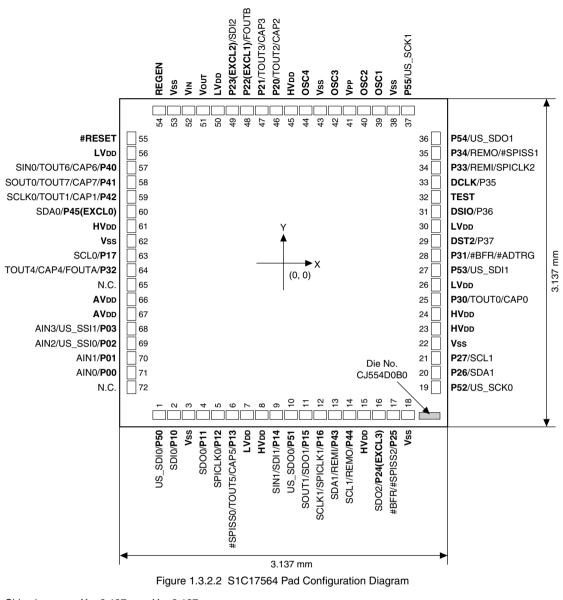

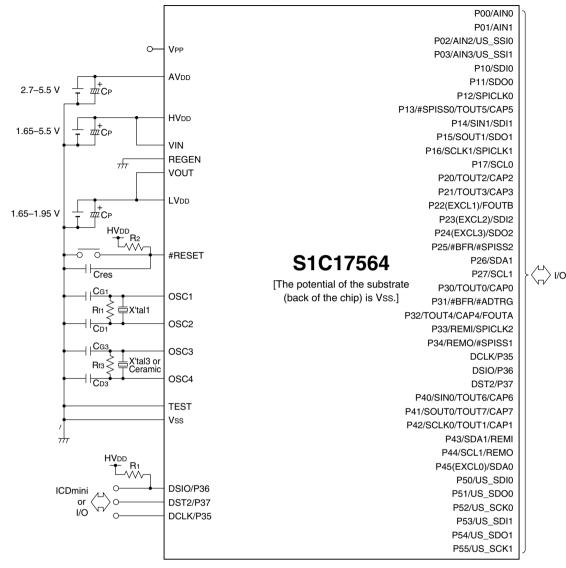

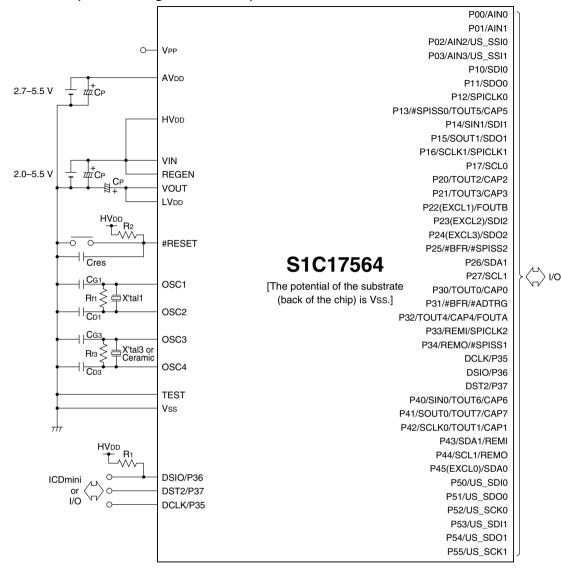

|   |         | 1.3.2 S1C17564 Pin Configuration Diagram                              | .1-9 |

|   |         | 1.3.3 Pin Descriptions                                                | 1-12 |

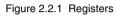

| 2 | CPU     |                                                                       | .2-1 |

|   |         | Features of the S1C17 Core                                            |      |

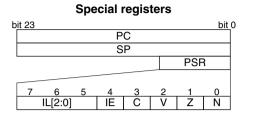

|   | 2.2     | CPU Registers                                                         | .2-2 |

|   | 2.3     | Instruction Set                                                       | .2-2 |

|   | 2.4     | Reading PSR                                                           | .2-5 |

|   |         | Processor Information                                                 |      |

| 3 | Memor   | y Map, Bus Control                                                    | 3-1  |

| Ŭ |         | Bus Cycle                                                             |      |

|   | 0.1     | 3.1.1 Restrictions on Access Size                                     |      |

|   |         | 3.1.2 Restrictions on Instruction Execution Cycles                    |      |

|   | 3.2     | Flash Area                                                            |      |

|   |         | 3.2.1 Embedded Flash Memory                                           | .3-2 |

|   |         | 3.2.2 Flash Programming                                               |      |

|   |         | 3.2.3 Protect Bits                                                    |      |

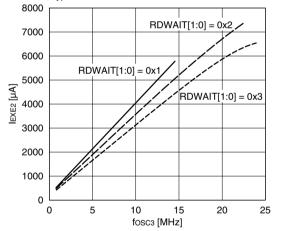

|   |         | 3.2.4 Flash Memory Read Wait Cycle Setting                            |      |

|   |         | FLASHC Read Wait Control Register (FLASHC_WAIT)                       |      |

|   | 3.3     | Internal RAM Area                                                     |      |

|   |         | 3.3.1 Embedded RAM<br>IRAM Size Register (MISC_IRAMSZ)                |      |

|   | 3.4     | Internal Peripheral Area                                              |      |

|   | 0.4     | 3.4.1 Internal Peripheral Area 1 (0x4000–)                            |      |

|   |         | 3.4.2 Internal Peripheral Area 2 (0x5000–)                            |      |

|   | 3.5     | S1C17 Core I/O Area                                                   |      |

| л |         | Supply                                                                |      |

| 4 |         |                                                                       |      |

|   |         | Core Power Supply Voltage (LVDD)                                      |      |

|   |         |                                                                       |      |

|   |         | Analog Power Supply Voltage (AVDD)                                    |      |

|   |         | Flash Programming Power Supply Voltage (VPP)                          |      |

|   |         | Embedded Regulator (S1C17564)                                         |      |

|   | 4.6     | Control Register Details (S1C17564)<br>VD1 Control Register (VD1_CTL) |      |

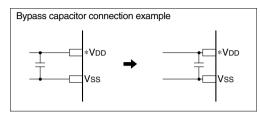

|   | 47      | Precautions on Power Supply                                           |      |

| _ |         |                                                                       |      |

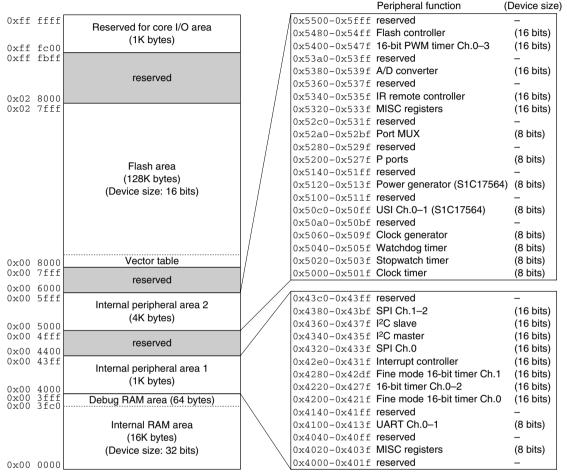

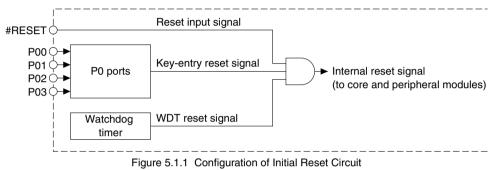

| 5 |         | Reset                                                                 |      |

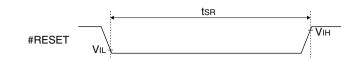

|   | 5.1     | Initial Reset Sources                                                 |      |

|   |         | 5.1.1 #RESET Pin<br>5.1.2 P0 Port Key-Entry Reset                     |      |

|   |         | 5.1.3 Resetting by the Watchdog Timer                                 |      |

|   | 5.0     | Initial Reset Sequence                                                |      |

|   |         | Initial Settings After an Initial Reset                               |      |

|   | 5.5     |                                                                       | .0-2 |

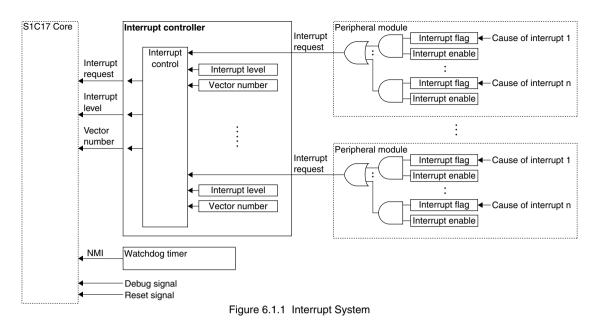

| 6 | Interru | pt Controller (ITC)                                                                     | 6-1  |

|---|---------|-----------------------------------------------------------------------------------------|------|

|   | 6.1     | ITC Module Overview                                                                     | 6-1  |

|   | 6.2     | Vector Table                                                                            | 6-2  |

|   |         | Vector Table Address Low/High Registers (MISC_TTBRL, MISC_TTBRH)                        | 6-4  |

|   | 6.3     | Control of Maskable Interrupts                                                          | 6-4  |

|   |         | 6.3.1 Interrupt Control Bits in Peripheral Modules                                      | 6-4  |

|   |         | 6.3.2 ITC Interrupt Request Processing                                                  | 6-4  |

|   |         | 6.3.3 Interrupt Processing by the S1C17 Core                                            | 6-5  |

|   | 6.4     | NMI                                                                                     | 6-6  |

|   | 6.5     | Software Interrupts                                                                     | 6-6  |

|   | 6.6     | HALT and SLEEP Mode Cancellation                                                        | 6-6  |

|   | 6.7     | Control Register Details                                                                | 6-6  |

|   |         | Interrupt Level Setup Register x (ITC_LVx)                                              |      |

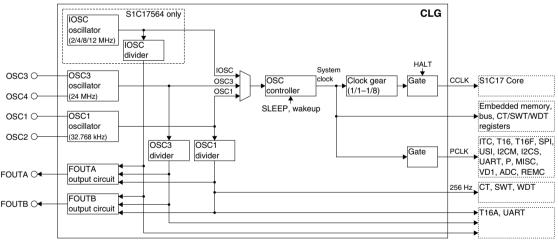

| 7 | Clock   | Generator (CLG)                                                                         | 7-1  |

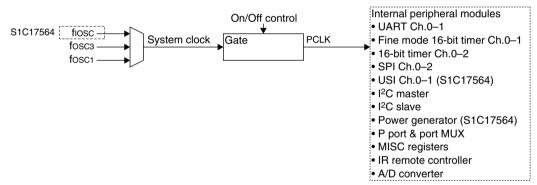

| • |         | CLG Module Overview                                                                     |      |

|   |         | CLG Input/Output Pins                                                                   |      |

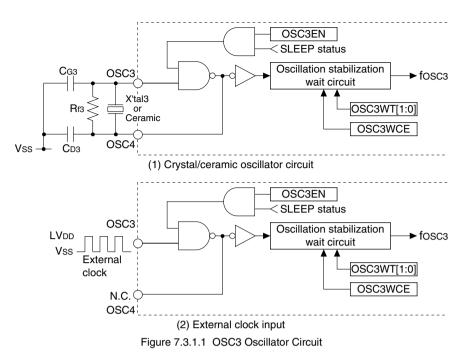

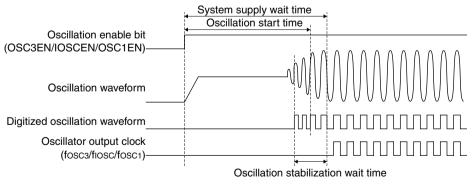

|   |         | Oscillators                                                                             |      |

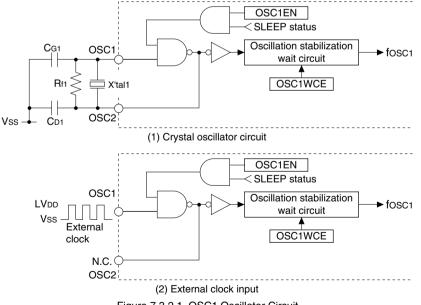

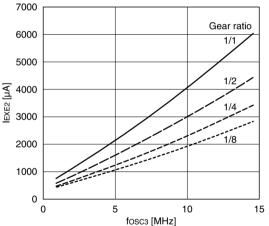

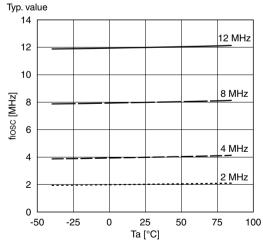

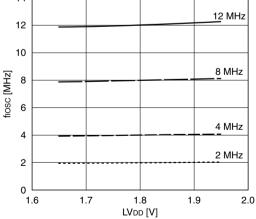

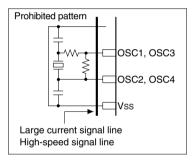

|   | 7.5     | 7.3.1 OSC3 Oscillator                                                                   |      |

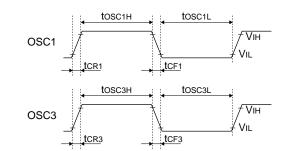

|   |         | 7.3.2 OSC1 Oscillator                                                                   |      |

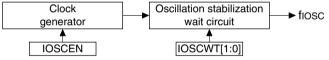

|   |         | 7.3.3 IOSC Oscillator (S1C17564)                                                        |      |

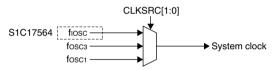

|   | 7.4     | System Clock Switching                                                                  |      |

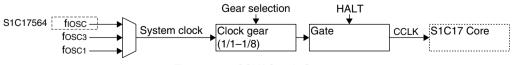

|   |         | CPU Core Clock (CCLK) Control                                                           |      |

|   |         | Peripheral Module Clock (PCLK) Control                                                  |      |

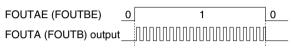

|   |         | Clock External Output (FOUTA, FOUTB)                                                    |      |

|   |         | Control Register Details                                                                |      |

|   | 7.0     | Clock Source Select Register (CLG_SRC)                                                  |      |

|   |         | Oscillation Control Register (CLG_CTL)                                                  |      |

|   |         | Noise Filter Enable Register (CLG_NFEN)                                                 |      |

|   |         | FOUTA Control Register (CLG_FOUTA)                                                      |      |

|   |         | FOUTB Control Register (CLG_FOUTB)                                                      |      |

|   |         | IOSC Control Register (CLG_IOSC)                                                        |      |

|   |         | PCLK Control Register (CLG_PCLK)<br>CCLK Control Register (CLG_CCLK)                    |      |

|   |         |                                                                                         |      |

| 8 |         | ts (P)                                                                                  |      |

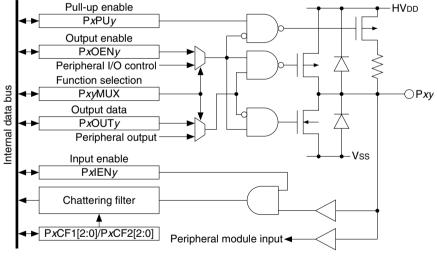

|   |         | P Module Overview                                                                       |      |

|   |         | Input/Output Pin Function Selection (Port MUX)                                          |      |

|   | 8.3     | Data Input/Output                                                                       | 8-3  |

|   | 8.4     | Pull-up Control                                                                         | 8-3  |

|   | 8.5     | P0–P3 Port Chattering Filter Function                                                   | 8-4  |

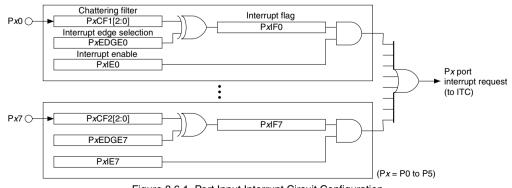

|   | 8.6     | Port Input Interrupt                                                                    | 8-4  |

|   | 8.7     | P0 Port Key-Entry Reset                                                                 | 8-5  |

|   | 8.8     | Control Register Details                                                                | 8-5  |

|   |         | Px Port Input Data Registers (Px_IN)                                                    |      |

|   |         | Px Port Output Data Registers (Px_OUT)                                                  |      |

|   |         | Px Port Output Enable Registers (Px_OEN)                                                |      |

|   |         | Px Port Pull-up Control Registers (Px_PU)<br>Px Port Interrupt Mask Registers (Px_IMSK) |      |

|   |         | Px Port Interrupt Edge Select Registers (Px_EDGE)                                       |      |

|   |         | Px Port Interrupt Flag Registers (Px_IFLG)                                              |      |

|   |         | Px Port Chattering Filter Control Registers (Px_CHAT)                                   | 8-10 |

|   |         | P0 Port Key-Entry Reset Configuration Register (P0_KRST)                                |      |

|   |         | Px Port Input Enable Registers (Px_IEN)                                                 | 8-11 |

|                                                                                                                  | P0[3:0] Port Function Select Register (P00_03PMUX)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              |

|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

|                                                                                                                  | P1[3:0] Port Function Select Register (P10_13PMUX)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              |

|                                                                                                                  | P1[7:4] Port Function Select Register (P14_17PMUX)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              |

|                                                                                                                  | P2[3:0] Port Function Select Register (P20_23PMUX)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              |

|                                                                                                                  | P2[7:4] Port Function Select Register (P24_27PMUX)<br>P3[3:0] Port Function Select Register (P30_33PMUX)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                              |

|                                                                                                                  | P3[5:0] Fort Function Select Register (P34_37PMUX)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              |

|                                                                                                                  | P4[3:0] Port Function Select Register (P40_43PMUX)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              |

|                                                                                                                  | P4[5:4] Port Function Select Register (P44_45PMUX)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              |

|                                                                                                                  | P5[3:0] Port Function Select Register (P50_53PMUX)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              |

|                                                                                                                  | P5[5:4] Port Function Select Register (P54_55PMUX)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8-21                         |

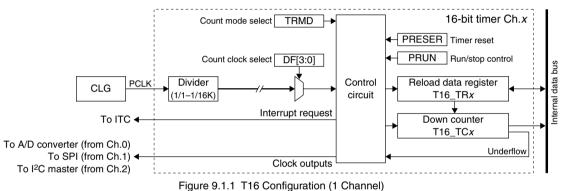

| 9 16-bit 7                                                                                                       | ïmers (T16)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                              |

|                                                                                                                  | T16 Module Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                              |

|                                                                                                                  | Count Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                              |

|                                                                                                                  | Count Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                              |

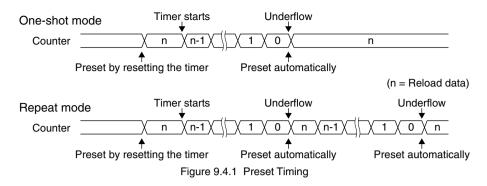

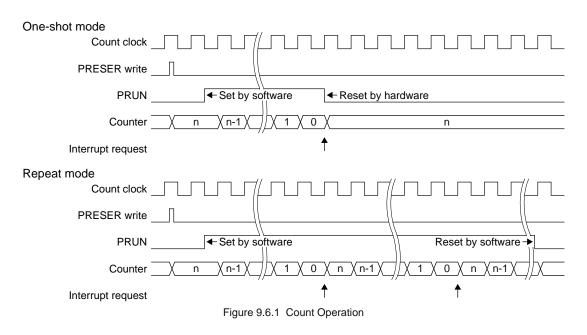

|                                                                                                                  | Reload Data Register and Underflow Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                              |

|                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                              |

|                                                                                                                  | Timer Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                              |

|                                                                                                                  | Timer RUN/STOP Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                              |

|                                                                                                                  | T16 Output Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              |

|                                                                                                                  | T16 Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                              |

| 9.9                                                                                                              | Control Register Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                              |

|                                                                                                                  | T16 Ch.x Count Clock Select Registers (T16_CLKx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                              |

|                                                                                                                  | T16 Ch.x Reload Data Registers (T16_TRx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                              |

|                                                                                                                  | T16 Ch.x Counter Data Registers (T16_TCx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              |

|                                                                                                                  | T16 Ch. <i>x</i> Control Registers (T16_CTL <i>x</i> )<br>T16 Ch. <i>x</i> Interrupt Control Registers (T16_INT <i>x</i> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                              |

|                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                              |

|                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                              |

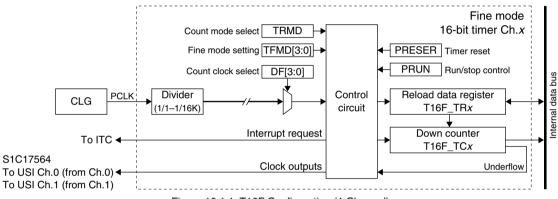

|                                                                                                                  | Node 16-bit Timers (T16F)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              |

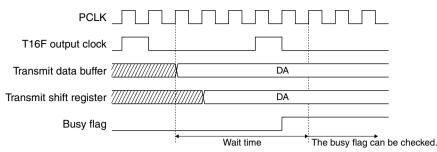

| 10.1                                                                                                             | T16F Module Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10-1                         |

| 10.1                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10-1                         |

| 10. <sup>-</sup><br>10.2                                                                                         | T16F Module Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10-1<br>10-2                 |

| 10. <sup>-</sup><br>10.2<br>10.3                                                                                 | T16F Module Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10-1<br>10-2<br>10-2         |

| 10. <sup>-</sup><br>10.2<br>10.3<br>10.4                                                                         | T16F Module Overview         Count Clock         Count Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10-1<br>10-2<br>10-2<br>10-2 |

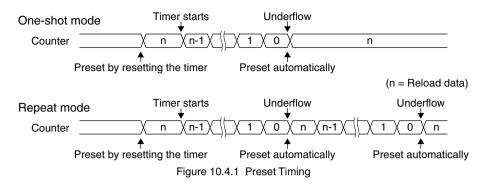

| 10. <sup>-</sup><br>10.2<br>10.3<br>10.4<br>10.4                                                                 | T16F Module Overview         Count Clock         Count Mode         Reload Data Register and Underflow Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                              |

| 10. <sup>-</sup><br>10.2<br>10.3<br>10.4<br>10.4<br>10.6                                                         | T16F Module Overview         Count Clock         Count Mode         Reload Data Register and Underflow Cycle         Timer Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                              |

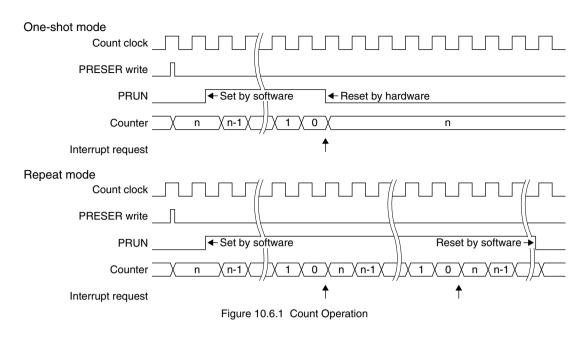

| 10. <sup>-</sup><br>10.2<br>10.3<br>10.4<br>10.4<br>10.6<br>10.6                                                 | T16F Module Overview         Count Clock         Count Mode         Reload Data Register and Underflow Cycle         Timer Reset         Timer RUN/STOP Control         T16F Output Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                              |

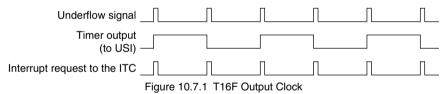

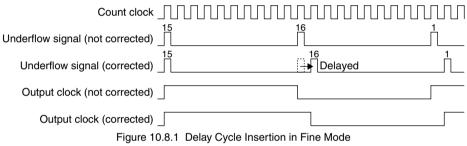

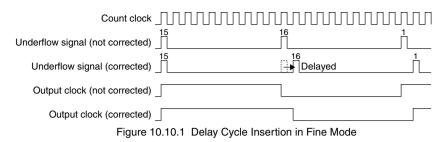

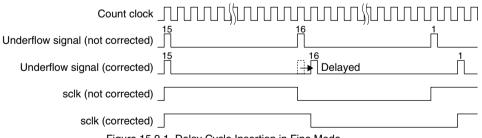

| 10. <sup>-</sup><br>10.2<br>10.3<br>10.4<br>10.4<br>10.5<br>10.7<br>10.7                                         | T16F Module Overview         Count Clock         Count Mode         Reload Data Register and Underflow Cycle         Timer Reset         Timer RUN/STOP Control         T16F Output Signals         Fine Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                              |

| 10. <sup>-</sup><br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>10.7<br>10.8<br>10.5                                 | T16F Module Overview         Count Clock         Count Mode         Reload Data Register and Underflow Cycle         Timer Reset         Timer RUN/STOP Control         T16F Output Signals         Fine Mode         T16F Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                              |

| 10. <sup>-</sup><br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>10.7<br>10.8<br>10.5                                 | T16F Module Overview         Count Clock         Count Mode         Reload Data Register and Underflow Cycle         Timer Reset         Timer RUN/STOP Control         T16F Output Signals         Fine Mode         T16F Interrupts         0 Control Register Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                              |

| 10. <sup>-</sup><br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>10.7<br>10.8<br>10.5                                 | T16F Module Overview         2 Count Clock.         3 Count Mode.         4 Reload Data Register and Underflow Cycle.         5 Timer Reset.         5 Timer RUN/STOP Control         7 T16F Output Signals         8 Fine Mode         9 T16F Interrupts.         0 Control Register Details         T16F Ch.x Count Clock Select Registers (T16F_CLKx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                              |

| 10. <sup>-</sup><br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>10.7<br>10.8<br>10.5                                 | T16F Module Overview         Count Clock         Count Mode         Reload Data Register and Underflow Cycle         Timer Reset         Timer RUN/STOP Control         T16F Output Signals         Fine Mode         T16F Interrupts         0 Control Register Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                              |

| 10. <sup>-</sup><br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>10.7<br>10.8<br>10.5                                 | T16F Module Overview         2 Count Clock.         3 Count Mode.         4 Reload Data Register and Underflow Cycle.         5 Timer Reset.         5 Timer Reset.         6 Timer RUN/STOP Control         7 T16F Output Signals         8 Fine Mode         9 T16F Interrupts.         0 Control Register Details         T16F Ch.x Count Clock Select Registers (T16F_CLKx)         T16F Ch.x Counter Data Registers (T16F_TRx)         T16F Ch.x Control Registers (T16F_TCx)         T16F Ch.x Control Registers (T16F_CLX)                                                                                                                                                                                                                                                                                        |                              |

| 10. <sup>-</sup><br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>10.7<br>10.8<br>10.5                                 | T16F Module Overview         2 Count Clock.         3 Count Mode.         4 Reload Data Register and Underflow Cycle.         5 Timer Reset.         5 Timer Reset.         6 Timer RUN/STOP Control .         7 T16F Output Signals .         8 Fine Mode .         9 T16F Interrupts.         0 Control Register Details .         T16F Ch.x Count Clock Select Registers (T16F_CLKx)                                                                                                                                                                                                                                                                                                                                                                                                                                  |                              |

| 10. <sup>-</sup><br>10.2<br>10.4<br>10.4<br>10.4<br>10.6<br>10.7<br>10.8<br>10.5                                 | T16F Module Overview         2 Count Clock.         3 Count Mode.         4 Reload Data Register and Underflow Cycle.         5 Timer Reset.         5 Timer RUN/STOP Control         7 T16F Output Signals         9 Fine Mode         9 T16F Interrupts.         0 Control Register Details         T16F Ch.x Count Clock Select Registers (T16F_CLKx)         T16F Ch.x Reload Data Registers (T16F_TRx)         T16F Ch.x Counter Data Registers (T16F_TCx).         T16F Ch.x Control Registers (T16F_CTLx).         T16F Ch.x Interrupt Control Registers (T16F_INTx)                                                                                                                                                                                                                                              |                              |

| 10. <sup>-</sup><br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>10.7<br>10.8<br>10.5<br>10.5                         | T16F Module Overview         2 Count Clock.         3 Count Mode.         4 Reload Data Register and Underflow Cycle.         5 Timer Reset.         5 Timer Reset.         6 Timer RUN/STOP Control         7 T16F Output Signals         8 Fine Mode         9 T16F Interrupts.         0 Control Register Details         T16F Ch.x Count Clock Select Registers (T16F_CLKx)         T16F Ch.x Counter Data Registers (T16F_TRx)         T16F Ch.x Control Registers (T16F_TCx)         T16F Ch.x Control Registers (T16F_CLX)                                                                                                                                                                                                                                                                                        |                              |

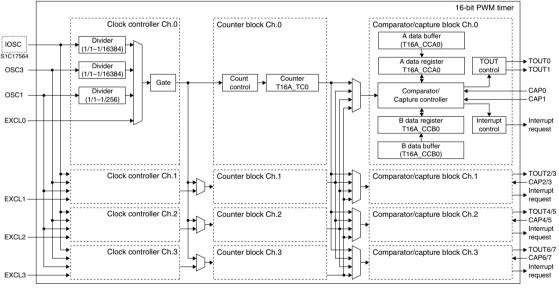

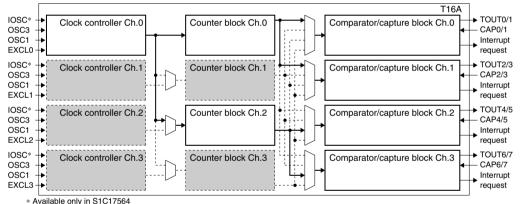

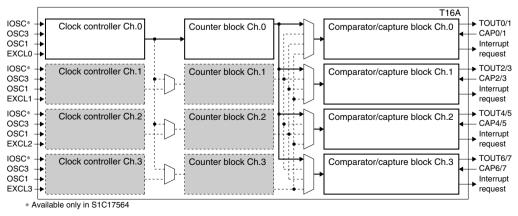

| 10. <sup>-</sup><br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>10.7<br>10.8<br>10.7<br>10.5<br>10                   | T16F Module Overview         2 Count Clock.         3 Count Mode         4 Reload Data Register and Underflow Cycle.         5 Timer Reset.         5 Timer Reset.         6 Timer RUN/STOP Control         7 T16F Output Signals         8 Fine Mode         9 T16F Interrupts.         0 Control Register Details         T16F Ch.x Count Clock Select Registers (T16F_CLKx)         T16F Ch.x Counter Data Registers (T16F_TRx)         T16F Ch.x Control Registers (T16F_TCx)         T16F Ch.x Control Registers (T16F_CLX)         T16F Ch.x Counter Data Registers (T16F_TCx)         T16F Ch.x Control Registers (T16F_CLX)         T16F Ch.x Interrupt Control Registers (T16F_INTx)         PWM Timers (T16A)         T16A Module Overview                                                                     |                              |

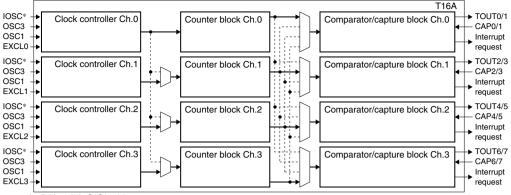

| 10. <sup>-</sup><br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>10.7<br>10.8<br>10.7<br>10.8<br>10.7                 | T16F Module Overview         2 Count Clock.         3 Count Mode.         4 Reload Data Register and Underflow Cycle.         5 Timer Reset.         5 Timer Reset.         6 Timer RUN/STOP Control         7 T16F Output Signals         8 Fine Mode         9 T16F Interrupts.         0 Control Register Details         T16F Ch.x Count Clock Select Registers (T16F_CLKx)         T16F Ch.x Reload Data Registers (T16F_TRx)         T16F Ch.x Counter Data Registers (T16F_TCx).         T16F Ch.x Control Registers (T16F_CLX).         T16F Ch.x Counter Data Registers (T16F_TCx).         T16F Ch.x Control Registers (T16F_CLX).         T16F Ch.x Interrupt Control Registers (T16F_INTx)         PWM Timers (T16A).         T16A Module Overview         2 T16A Input/Output Pins                          |                              |

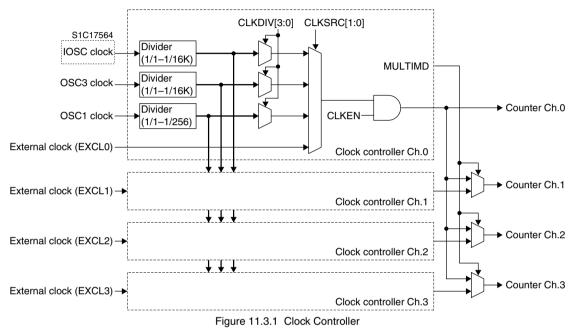

| 10. <sup>-</sup><br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>10.7<br>10.8<br>10.5<br>10.5<br>11.1<br>11.2<br>11.2 | T16F Module Overview         Count Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                              |

| 10. <sup>-</sup><br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>10.7<br>10.8<br>10.5<br>10.5<br>11.1<br>11.2<br>11.2 | T16F Module Overview         Count Clock         Count Mode         Reload Data Register and Underflow Cycle         Timer Reset         Timer RUN/STOP Control         T16F Output Signals         Fine Mode         T16F Interrupts         0 Control Register Details         T16F Ch.x Count Clock Select Registers (T16F_CLKx)         T16F Ch.x Counter Data Registers (T16F_TRx)         T16F Ch.x Control Registers (T16F_CLX)         T16F Ch.x Control Registers (T16F_CLX)         T16F Ch.x Interrupt Control Registers (T16F_INTx)         PWM Timers (T16A)         T16A Module Overview         T16A Input/Output Pins         Count Clock         T16A Operating Modes                                                                                                                                   |                              |

| 10. <sup>-</sup><br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>10.7<br>10.8<br>10.5<br>10.5<br>11.1<br>11.2<br>11.2 | T16F Module Overview         Count Clock         Count Mode         Reload Data Register and Underflow Cycle         Timer Reset         Timer Reset         Timer RUN/STOP Control         T16F Output Signals         Fine Mode         T16F Interrupts         0 Control Register Details         T16F Ch.x Count Clock Select Registers (T16F_CLKx)         T16F Ch.x Count Clock Select Registers (T16F_TRx)         T16F Ch.x Counter Data Registers (T16F_TCx)         T16F Ch.x Control Registers (T16F_CLX)         T16F Ch.x Control Registers (T16F_CLX)         T16F Ch.x Interrupt Control Registers (T16F_INTx)         PWM Timers (T16A)         T16A Module Overview         2 T16A Input/Output Pins         3 Count Clock         T16A Operating Modes         11.4.1 Comparator Mode and Capture Mode |                              |

| 10. <sup>-</sup><br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>10.7<br>10.8<br>10.5<br>10.5<br>11.1<br>11.2<br>11.2 | T16F Module Overview         Count Clock         Count Mode         Reload Data Register and Underflow Cycle         Timer Reset         Timer RUN/STOP Control         T16F Output Signals         Fine Mode         T16F Interrupts         0 Control Register Details         T16F Ch.x Count Clock Select Registers (T16F_CLKx)         T16F Ch.x Counter Data Registers (T16F_TRx)         T16F Ch.x Control Registers (T16F_CLX)         T16F Ch.x Control Registers (T16F_CLX)         T16F Ch.x Interrupt Control Registers (T16F_INTx)         PWM Timers (T16A)         T16A Module Overview         T16A Input/Output Pins         Count Clock         T16A Operating Modes                                                                                                                                   |                              |

### CONTENTS

|     | 11.5   | Counter Control                                                                                                                           | 11-8   |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------|--------|

|     |        | 11.5.1 Counter Reset                                                                                                                      | 11-8   |

|     |        | 11.5.2 Counter RUN/STOP Control                                                                                                           | 11-8   |

|     |        | 11.5.3 Reading Counter Values                                                                                                             | 11-8   |

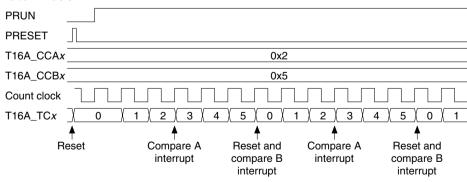

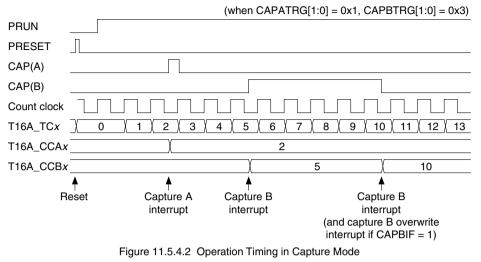

|     |        | 11.5.4 Timing Charts                                                                                                                      | 11-8   |

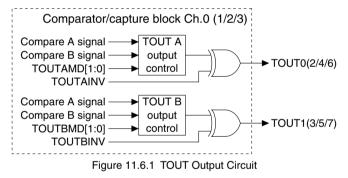

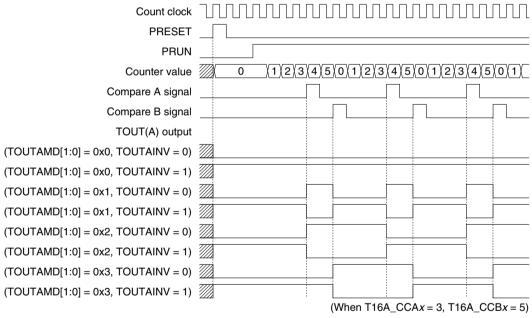

|     | 11.6   | Timer Output Control                                                                                                                      | 11-9   |

|     | 11.7   | T16A Interrupts                                                                                                                           | .11-10 |

|     |        | Control Register Details                                                                                                                  |        |

|     |        | T16A Clock Control Register Ch.x (T16A_CLKx)                                                                                              |        |

|     |        | T16A Counter Ch.x Control Registers (T16A_CTLx)                                                                                           |        |

|     |        | T16A Counter Ch.x Data Registers (T16A_TCx)                                                                                               |        |

|     |        | T16A Comparator/Capture Ch.x Control Registers (T16A_CCCTLx)                                                                              |        |

|     |        | T16A Comparator/Capture Ch.x A Data Registers (T16A_CCAx)                                                                                 |        |

|     |        | T16A Comparator/Capture Ch.x B Data Registers (T16A_CCBx)                                                                                 |        |

|     |        | T16A Comparator/Capture Ch.x Interrupt Enable Registers (T16A_IENx)<br>T16A Comparator/Capture Ch.x Interrupt Flag Registers (T16A_IFLGx) |        |

|     |        |                                                                                                                                           |        |

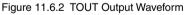

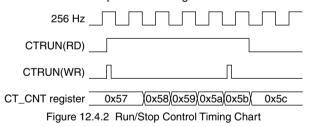

| 12  | Clock  | Гіmer (СТ)                                                                                                                                | .12-1  |

|     | 12.1   | CT Module Overview                                                                                                                        | 12-1   |

|     | 12.2   | Operation Clock                                                                                                                           | 12-1   |

|     | 12.3   | Timer Reset                                                                                                                               | 12-1   |

|     | 12.4   | Timer RUN/STOP Control                                                                                                                    | 12-1   |

|     |        | CT Interrupts                                                                                                                             |        |

|     |        | Control Register Details                                                                                                                  |        |

|     | 12.0   | Clock Timer Control Register (CT_CTL)                                                                                                     |        |

|     |        | Clock Timer Counter Register (CT_CNT)                                                                                                     |        |

|     |        | Clock Timer Interrupt Mask Register (CT_IMSK)                                                                                             | 12-4   |

|     |        | Clock Timer Interrupt Flag Register (CT_IFLG)                                                                                             | 12-4   |

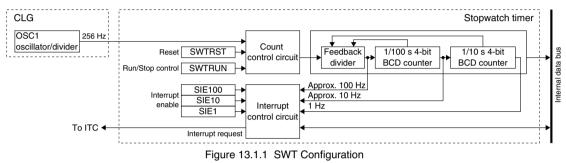

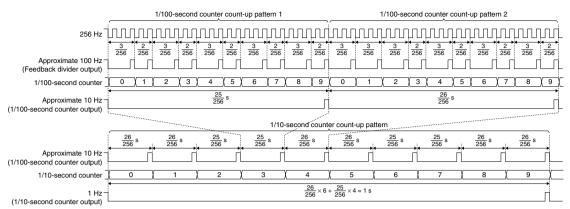

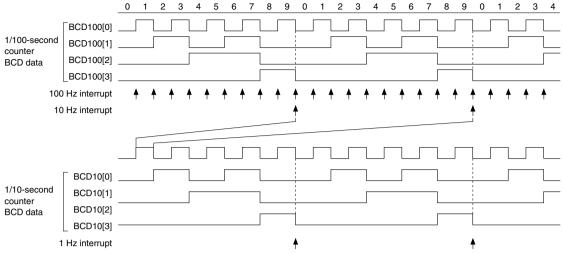

| 13  | Stopwa | atch Timer (SWT)                                                                                                                          | .13-1  |

|     | -      | SWT Module Overview                                                                                                                       |        |

|     |        | Operation Clock                                                                                                                           |        |

|     |        | BCD Counters                                                                                                                              |        |

|     |        | Timer Reset                                                                                                                               |        |

|     |        |                                                                                                                                           |        |

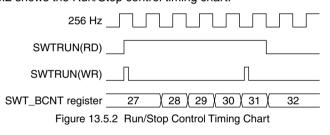

|     |        | Timer RUN/STOP Control                                                                                                                    |        |

|     |        | SWT Interrupts                                                                                                                            |        |

|     | 13.7   | Control Register Details                                                                                                                  | 13-4   |

|     |        | Stopwatch Timer Control Register (SWT_CTL)<br>Stopwatch Timer BCD Counter Register (SWT_BCNT)                                             |        |

|     |        | Stopwatch Timer Interrupt Mask Register (SWT_IMSK)                                                                                        |        |

|     |        | Stopwatch Timer Interrupt Flag Register (SWT_INDR)                                                                                        |        |

| 4.4 | Wataba |                                                                                                                                           |        |

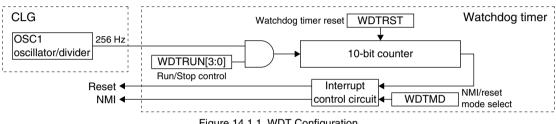

| 14  |        | dog Timer (WDT)                                                                                                                           |        |

|     |        | WDT Module Overview                                                                                                                       |        |

|     |        | Operation Clock                                                                                                                           |        |

|     | 14.3   | WDT Control.                                                                                                                              |        |

|     |        | 14.3.1 NMI/Reset Mode Selection                                                                                                           |        |

|     |        | 14.3.2 WDT Run/Stop Control                                                                                                               |        |

|     |        | 14.3.3 WDT Reset                                                                                                                          |        |

|     |        | 14.3.4 Operations in HALT and SLEEP Modes                                                                                                 |        |

|     | 14.4   | Control Register Details                                                                                                                  |        |

|     |        | Watchdog Timer Control Register (WDT_CTL)<br>Watchdog Timer Status Register (WDT_ST)                                                      |        |

|     |        |                                                                                                                                           | +-0    |

| 15 | UART.               |                                                                                                                        | 15-1  |

|----|---------------------|------------------------------------------------------------------------------------------------------------------------|-------|

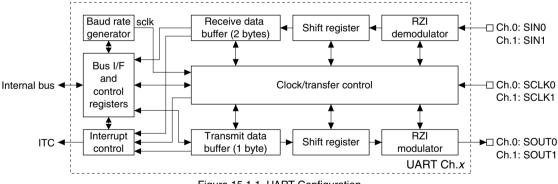

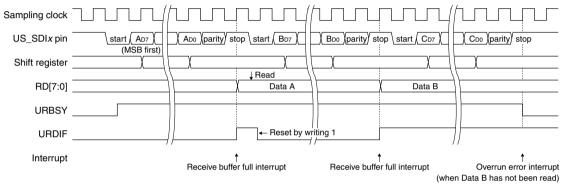

|    | 15.1                | UART Module Overview                                                                                                   | .15-1 |

|    | 15.2                | UART Input/Output Pins                                                                                                 | .15-2 |

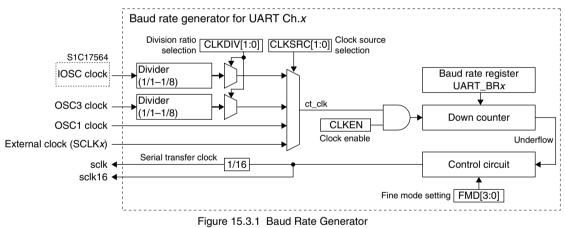

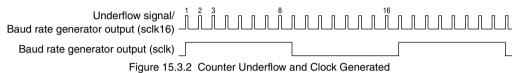

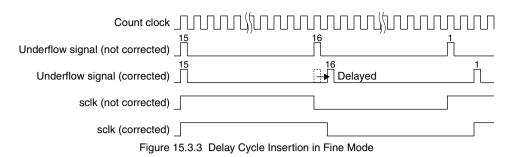

|    | 15.3                | Baud Rate Generator                                                                                                    | .15-2 |

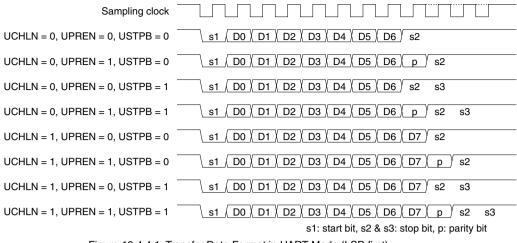

|    | 15.4                | Transfer Data Settings                                                                                                 | .15-4 |

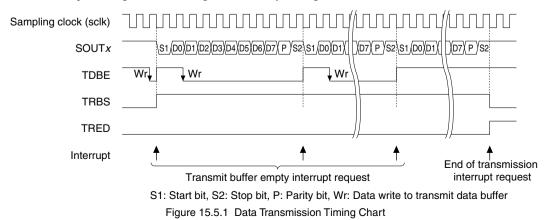

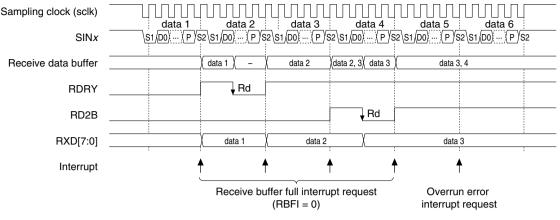

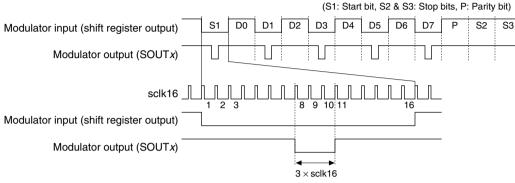

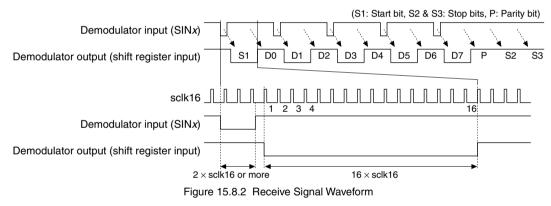

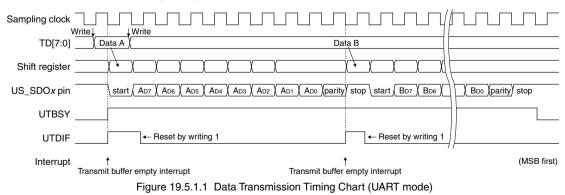

|    | 15.5                | Data Transfer Control                                                                                                  | .15-5 |

|    | 15.6                | Receive Errors                                                                                                         | .15-7 |

|    | 15.7                | UART Interrupts                                                                                                        | .15-8 |

|    |                     | IrDA Interface                                                                                                         |       |

|    |                     | Control Register Details                                                                                               |       |

|    |                     | UART Ch.x Status Registers (UART_STx)                                                                                  |       |

|    |                     | UART Ch.x Transmit Data Registers (UART_TXDx)                                                                          |       |

|    |                     | UART Ch.x Receive Data Registers (UART_RXDx)                                                                           |       |

|    |                     | UART Ch.x Mode Registers (UART_MODx)                                                                                   |       |

|    |                     | UART Ch. <i>x</i> Control Registers (UART_CTL <i>x</i> )<br>UART Ch. <i>x</i> Expansion Registers (UART_EXP <i>x</i> ) |       |

|    |                     | UART Ch.x Expansion registers (UART_EARX)                                                                              |       |

|    |                     | UART Ch.x Fine Mode Registers (UART_FMDx)                                                                              |       |

|    |                     | UART Ch.x Clock Control Registers (UART_CLKx)                                                                          | 15-16 |

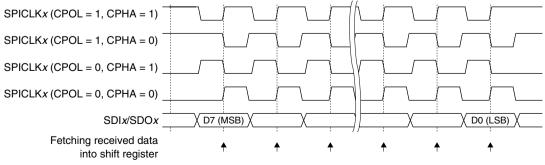

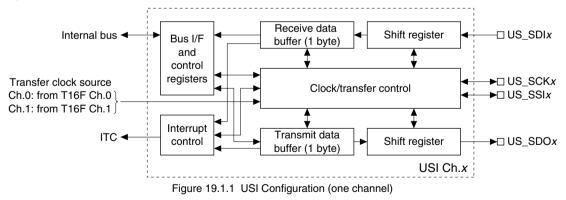

| 16 | SPI                 |                                                                                                                        | 16-1  |

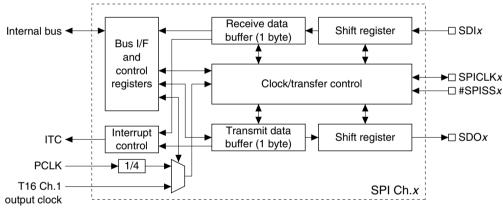

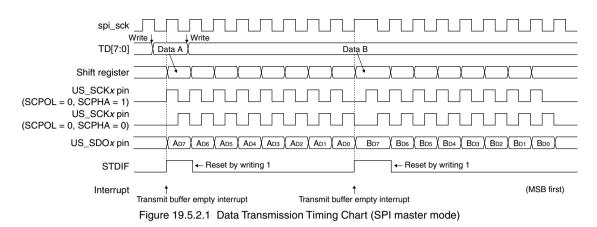

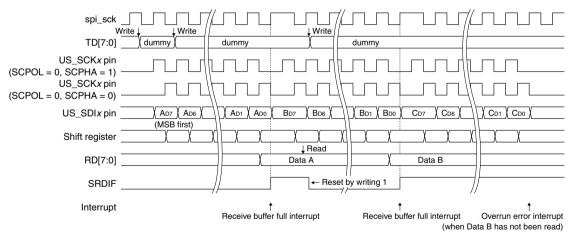

|    |                     | SPI Module Overview                                                                                                    |       |

|    |                     | SPI Input/Output Pins                                                                                                  |       |

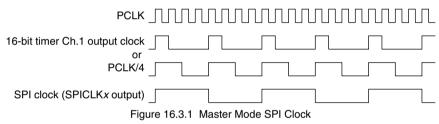

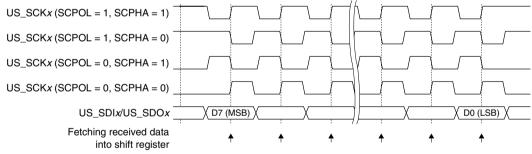

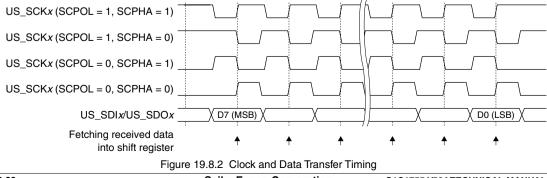

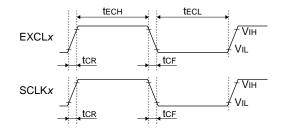

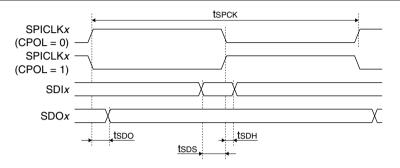

|    |                     | SPI Clock                                                                                                              |       |

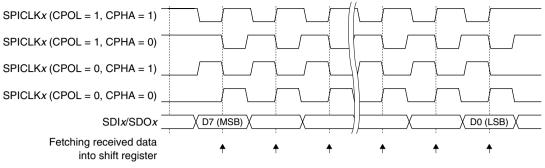

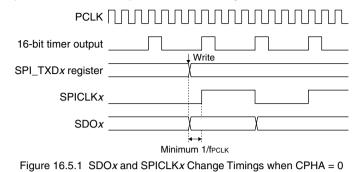

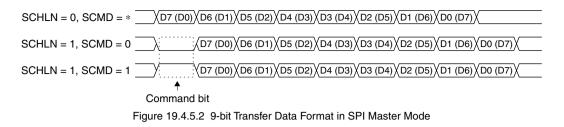

|    |                     | Data Transfer Condition Settings                                                                                       |       |

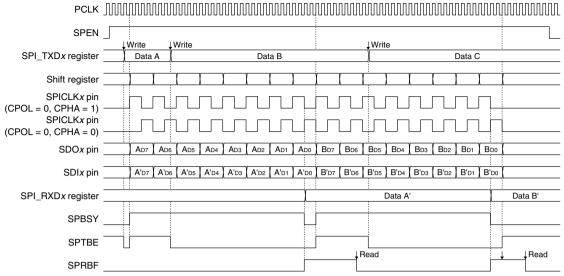

|    |                     | Data Transfer Control                                                                                                  |       |

|    |                     | SPI Interrupts                                                                                                         |       |

|    |                     | Control Register Details                                                                                               |       |

|    | 10.7                | SPI Ch.x Status Registers (SPI_STx)                                                                                    |       |

|    |                     | SPI Ch.x Transmit Data Registers (SPI_TXDx)                                                                            |       |

|    |                     | SPI Ch.x Receive Data Registers (SPI_RXDx)                                                                             |       |

|    |                     | SPI Ch.x Control Registers (SPI_CTLx)                                                                                  | 16-7  |

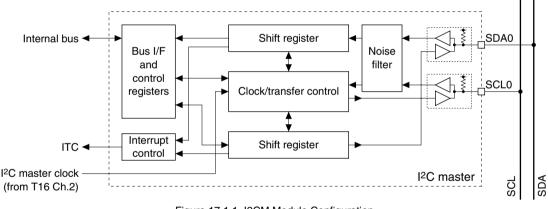

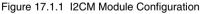

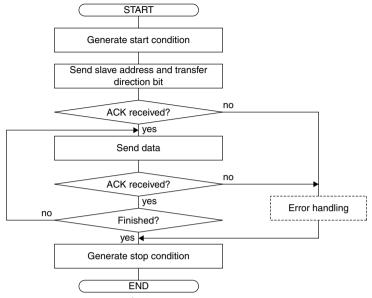

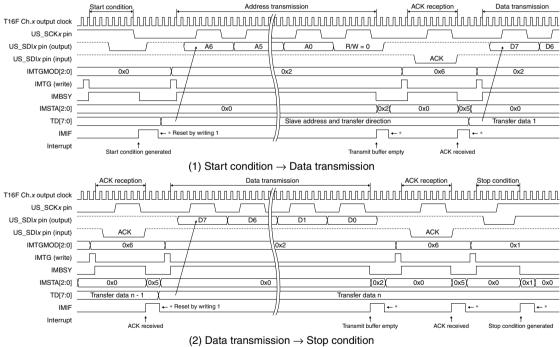

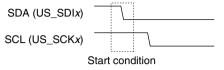

| 17 | I <sup>2</sup> C Ma | ster (I2CM)                                                                                                            | 17-1  |

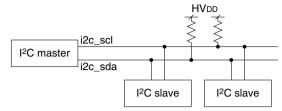

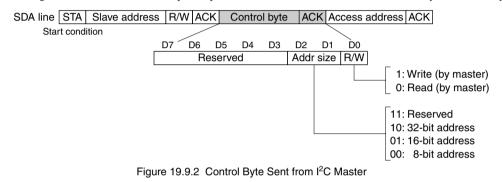

|    | 17.1                | I2CM Module Overview                                                                                                   | .17-1 |

|    | 17.2                | I2CM Input/Output Pins                                                                                                 | .17-1 |

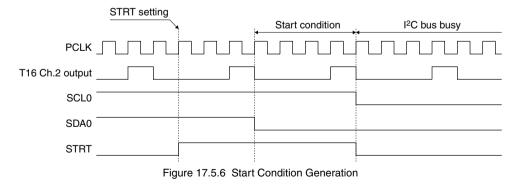

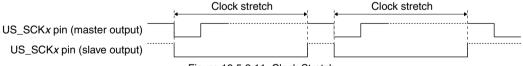

|    | 17.3                | Synchronization Clock                                                                                                  | .17-2 |

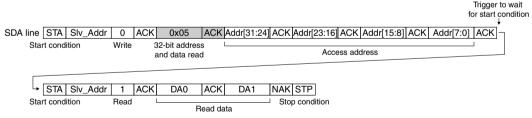

|    | 17.4                | Settings Before Data Transfer                                                                                          | .17-2 |

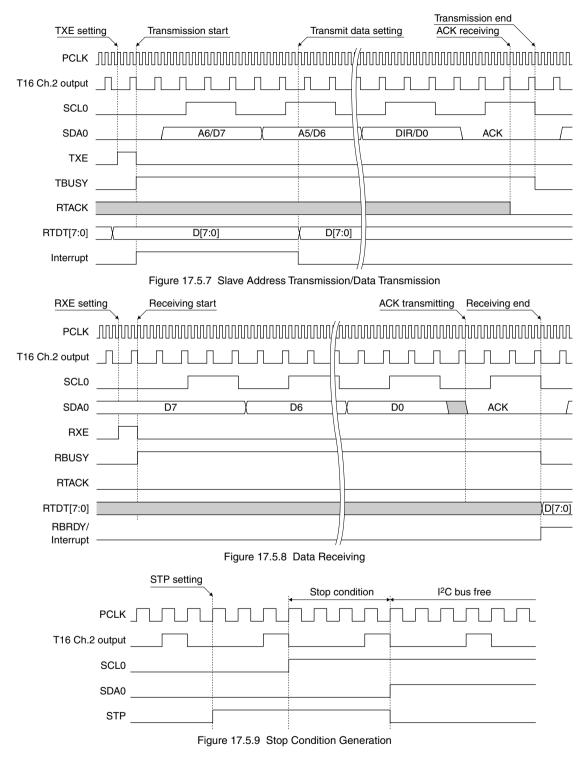

|    |                     | Data Transfer Control                                                                                                  |       |

|    |                     | I2CM Interrupts                                                                                                        |       |

|    |                     | Control Register Details                                                                                               |       |

|    |                     | I <sup>2</sup> C Master Enable Register (I2CM_EN)                                                                      |       |

|    |                     | I <sup>2</sup> C Master Control Register (I2CM_CTL)                                                                    |       |

|    |                     | I <sup>2</sup> C Master Data Register (I2CM_DAT)                                                                       |       |

|    |                     | I <sup>2</sup> C Master Interrupt Control Register (I2CM_ICTL)                                                         |       |

| 18 |                     | ve (I2CS)                                                                                                              |       |

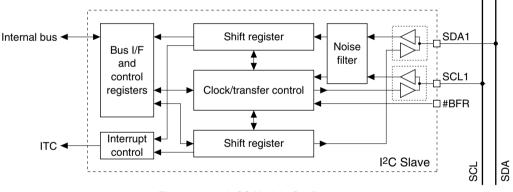

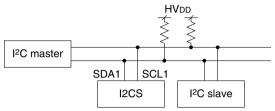

|    | 18.1                | I2CS Module Overview                                                                                                   | .18-1 |

|    | 18.2                | I2CS Input/Output Pins                                                                                                 | .18-1 |

|    | 18.3                | Operation Clock                                                                                                        | .18-2 |

|    | 18.4                | Initializing I2CS                                                                                                      | .18-2 |

|    |                     | 18.4.1 Reset                                                                                                           |       |

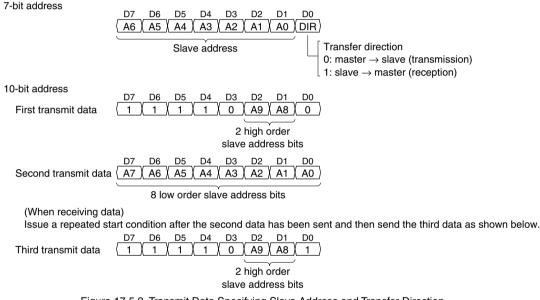

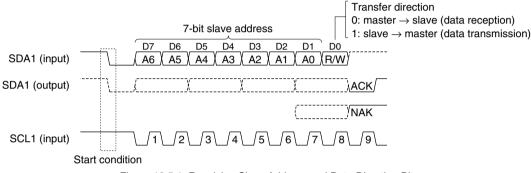

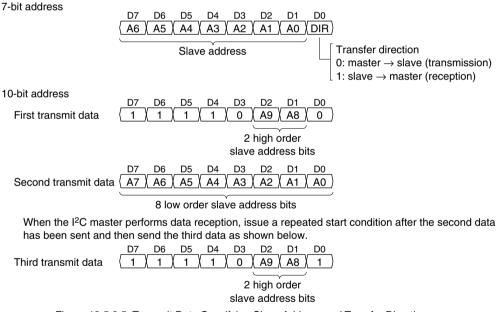

|    |                     | 18.4.2 Setting Slave Address                                                                                           | .18-3 |

|    |        | 18.4.3 Optional Functions                                                                                          | 18-3    |

|----|--------|--------------------------------------------------------------------------------------------------------------------|---------|

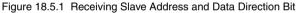

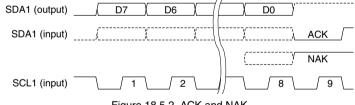

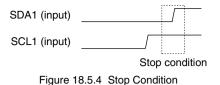

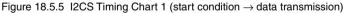

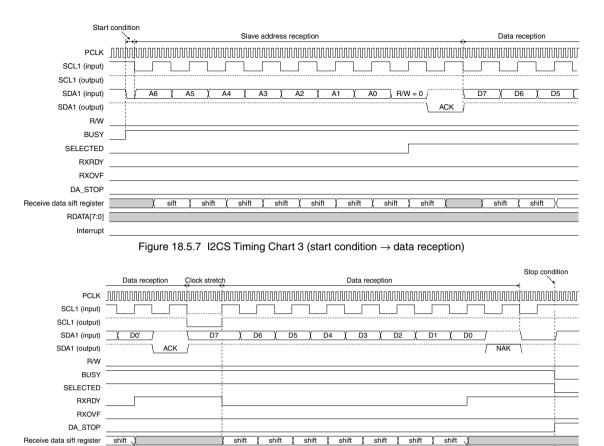

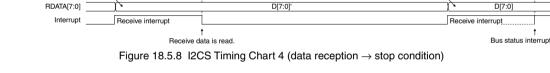

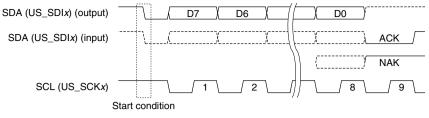

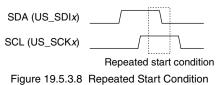

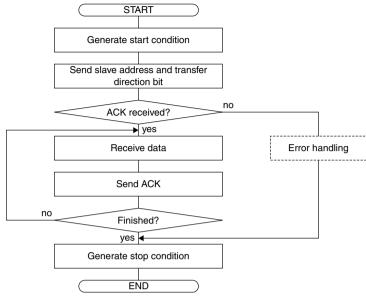

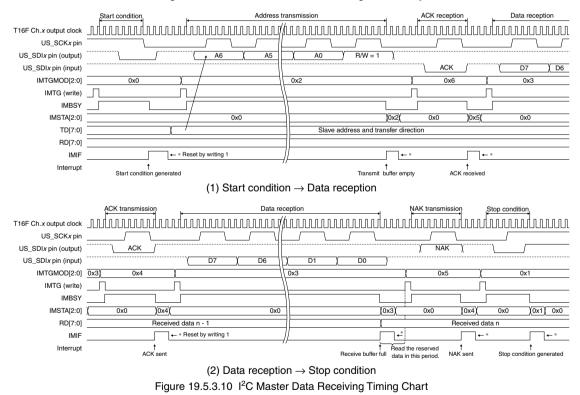

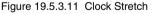

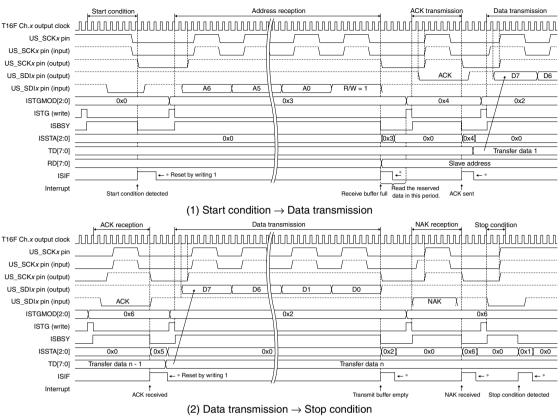

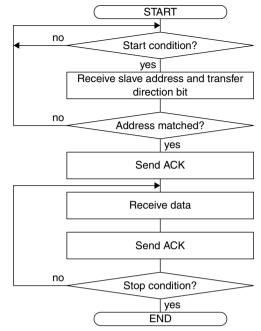

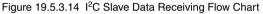

|    | 18.5   | Data Transfer Control                                                                                              | 18-3    |

|    | 18.6   | I2CS Interrupts                                                                                                    | 18-8    |

|    |        | Control Register Details                                                                                           |         |

|    | 10.7   | I <sup>2</sup> C Slave Transmit Data Register (I2CS_TRNS)                                                          |         |

|    |        | I <sup>2</sup> C Slave Receive Data Register (I2CS_RECV)                                                           |         |

|    |        | I <sup>2</sup> C Slave Address Setup Register (I2CS_SADRS)                                                         |         |