# S2S65A00 Technical Manual

#### **NOTICE**

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of Economy, Trade and Industry or other approval from another government agency.

is a registered trademark of ARM.

CompactFlash is a registered trademark of Sandisk.

All other product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

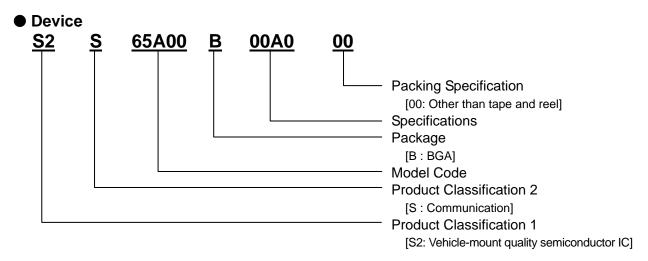

## Configuration of product number

#### **Precautions in Use**

For descriptions of the registers in this document, be careful with the following:

For descriptions of the registers in this document, the following abbreviations may be used.

R/W: Read and Write RO: Read Only WO: Write Only

RSV: Reserved bit/register (write down "0", if not otherwise specified)

n/a: not available (write down "0", if not otherwise specified)

If not otherwise specified, set "0" in the reserved bits for the registers. If a write operation performed on a reserved bit, unexpected results may occur. The bits specified as "n/a" have no impact on the hardware.

Some of the resisters can be accessed only under certain conditions. Read/write to the non-accessible registers is ineffective.

## **Table of Contents**

| 1. DESCRIPTION                                                          | 1  |

|-------------------------------------------------------------------------|----|

| 1.1 Features                                                            | 1  |

| 1.2 Built-In Functions                                                  | 1  |

| 2. BLOCK DIAGRAM                                                        | 4  |

| 3. PIN                                                                  | 5  |

| 3.1 Pin Assignment                                                      | 5  |

| 3.2 Pin Description                                                     | 7  |

| 3.3 Multiplex Pin Function of GPIO Pins, Pin Function Right after Reset |    |

| 3.4 Pin Status during Reset                                             | 20 |

| 4. FUNCTIONAL DESCRIPTION                                               |    |

| 4.1 System Configuration                                                |    |

| 4.2 Memory Map                                                          |    |

| 4.2.1 Memory Map (AHB1)                                                 |    |

| 4.3 I/O Map                                                             |    |

| 4.4 Interrupt Controller                                                |    |

| 4.5 Built-in Functions of S2S65A00                                      |    |

| 5. CPU                                                                  | 27 |

| 5.1 Description                                                         | 27 |

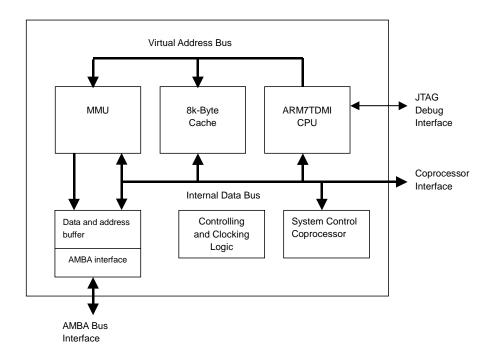

| 5.2 ARM720T Block Diagram                                               | 27 |

| 6. DMA CONTROLLER 1 (DMAC1)                                             | 28 |

| 6.1 Description                                                         | 28 |

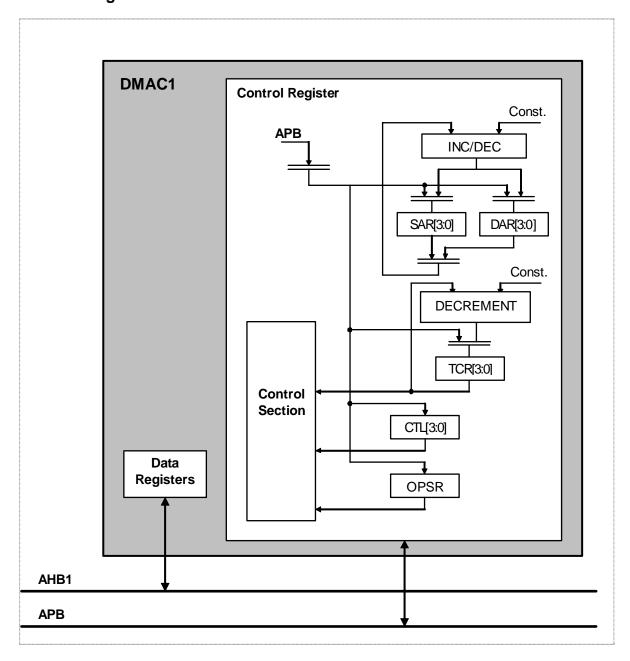

| 6.2 Block Diagram                                                       | 28 |

| 6.3 External Pins                                                       |    |

| 6.4 Registers                                                           |    |

| 6.4.1 List of Registers                                                 |    |

| 7. CAMERA INTERFACE [2:1] (CAM[2:1])                                    |    |

|                                                                         |    |

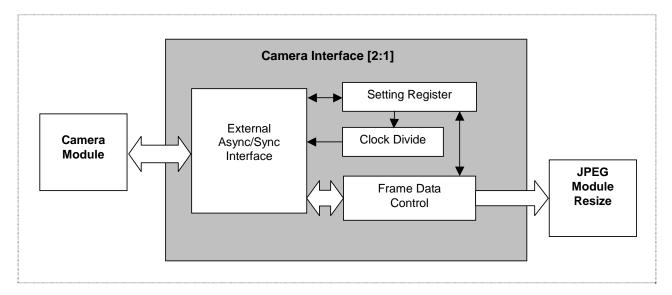

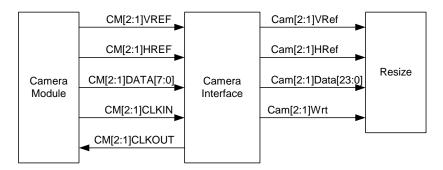

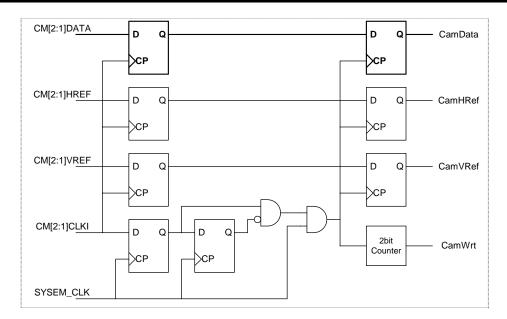

| 7.1 Description7.2 Block Diagram                                        |    |

| 7.3 External Pins                                                       |    |

| 7.4 Registers                                                           |    |

| 7.4.1 List of Registers                                                 | 37 |

| 7.4.2 Detailed Description of Registers                                 |    |

| 7.5 Explanation of Operation                                            |    |

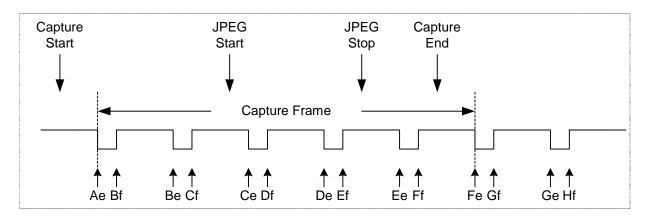

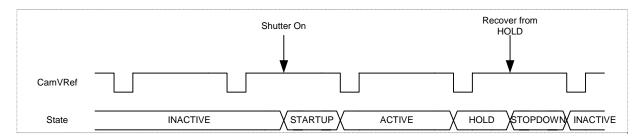

| 7.5.1 Frame Capture Interrupt                                           |    |

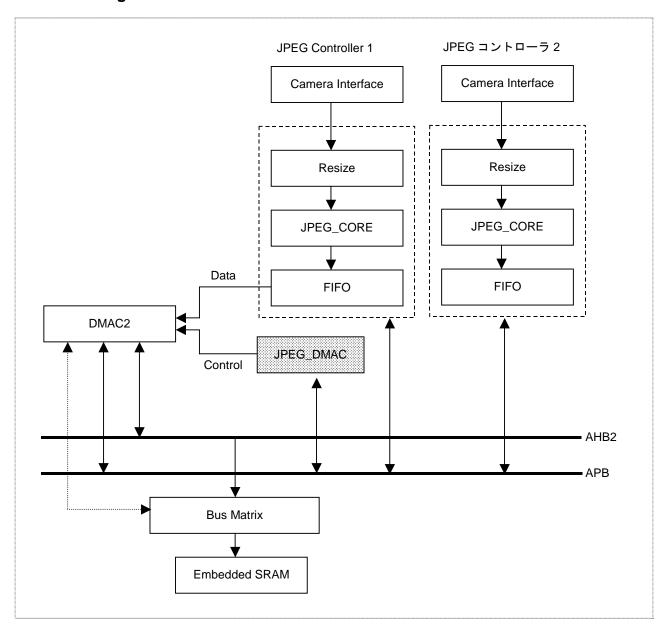

| 8. JPEG CONTROLLER (JPG[2:1])                                           |    |

| 8.1 Description                                                         |    |

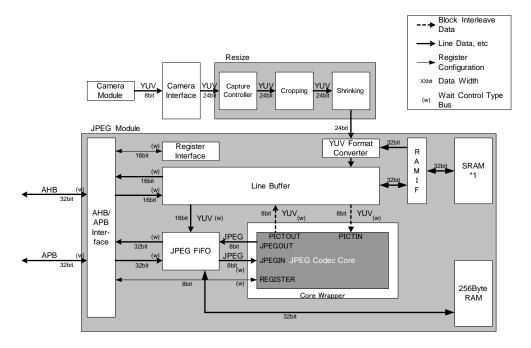

| 8.2 Block Diagram8.3 External Pins                                      |    |

| 8.4 Registers                                                           |    |

| 8.4.1 List of Registers                                                 |    |

|                                                                         |    |

| 8.4.2 Resizer Operation Registers (RSZ[2:1])                   |     |

|----------------------------------------------------------------|-----|

| 8.4.3 JPEG Module Registers (JCTL[2:1])                        |     |

| 8.4.4 JPEG FIFO Setting Register (JFIFO[2:1])                  |     |

| 8.4.5 JPEG Line Buffer Setting Register (JLB[2:1])             |     |

| 8.4.6 JPEG Codec Registers (JCODEC[2:1])                       |     |

| 8.5 Explanation of Operations                                  | 81  |

| 8.5.1 Capture Control                                          | 81  |

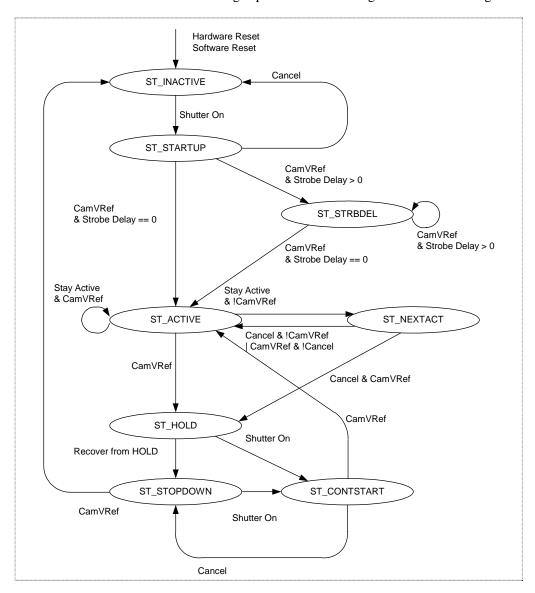

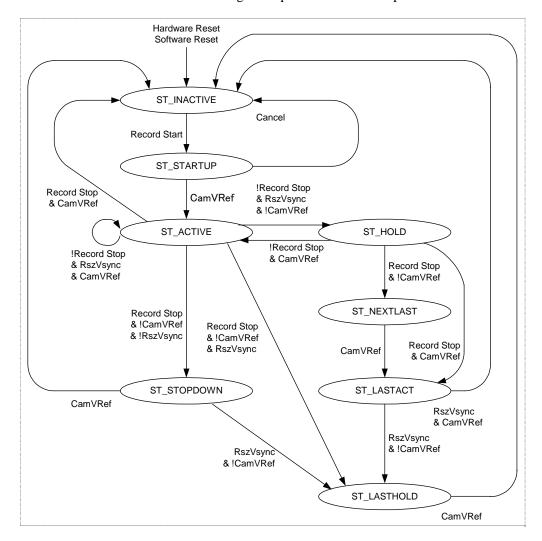

| 8.5.1.1 State Machine for JPEG Encoding of Camera Image        | 81  |

| 8.5.1.2 State Machine for YUV Capture                          |     |

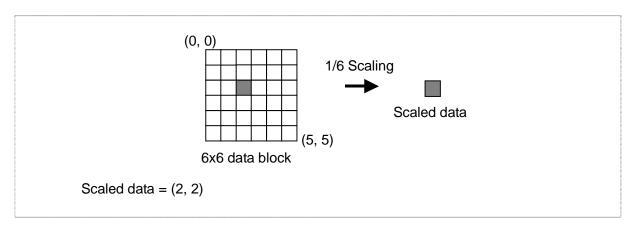

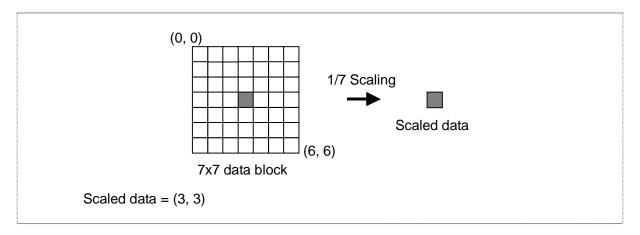

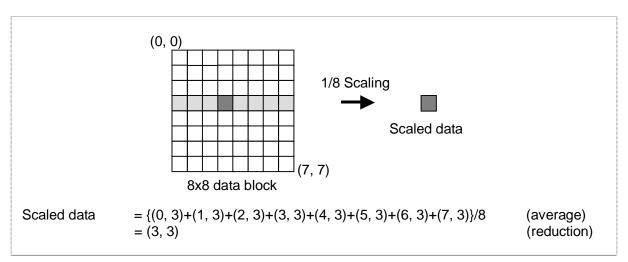

| 8.5.2 Resizing                                                 |     |

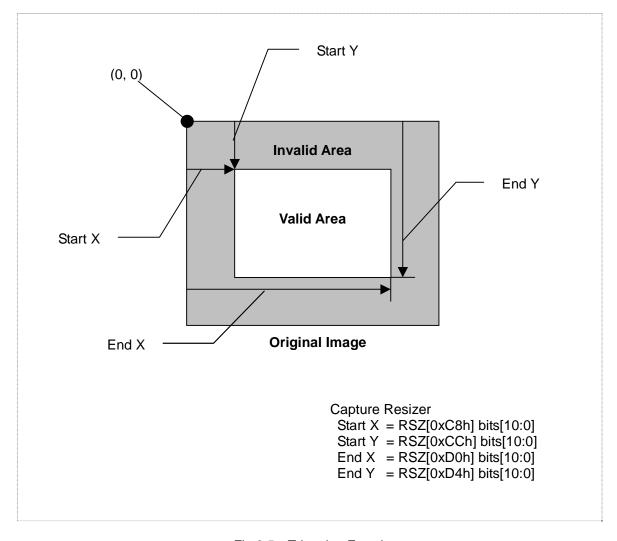

| 8.5.2.1 Trimming                                               |     |

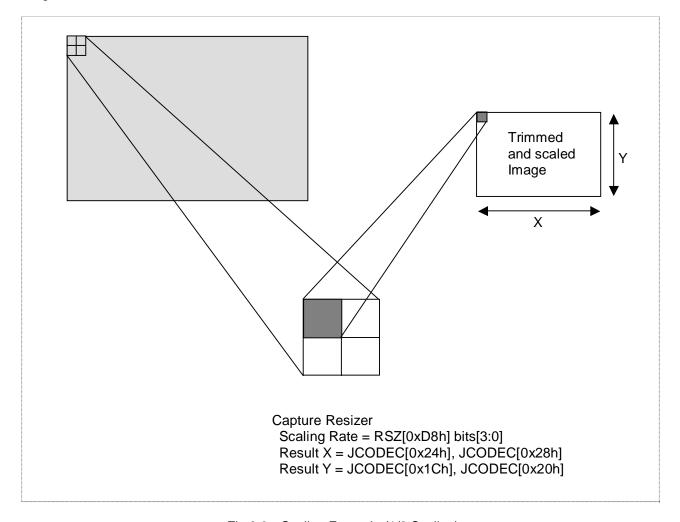

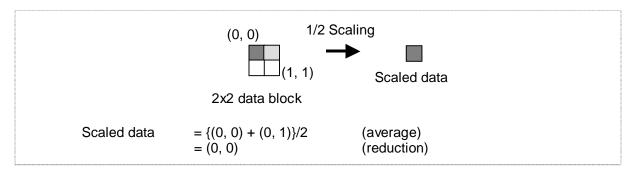

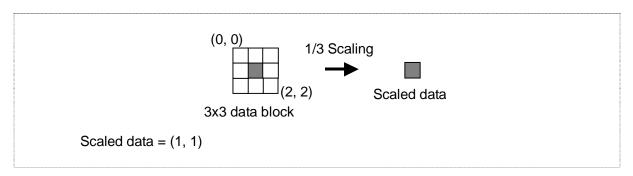

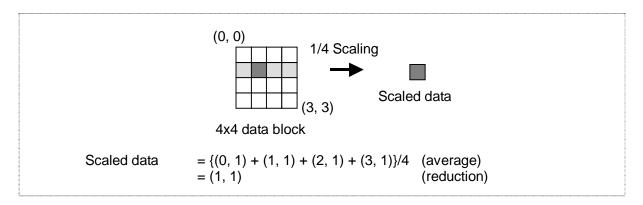

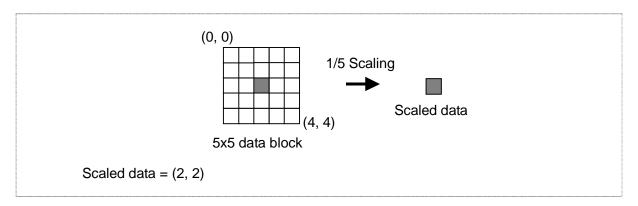

| 8.5.2.2 Scaling                                                |     |

| 8.5.2.3 Restrictions on the Use of Resizer                     |     |

| 8.5.3 Data Flow of Image Processing                            |     |

| 8.5.3.1 Camera Image JPEG Encoding                             |     |

| 8.5.3.2 YUV Data Capture                                       |     |

| 8.5.4 JPEG Codec.                                              |     |

| 8.5.4.1 Restrictions on JPEG Codec Registers                   |     |

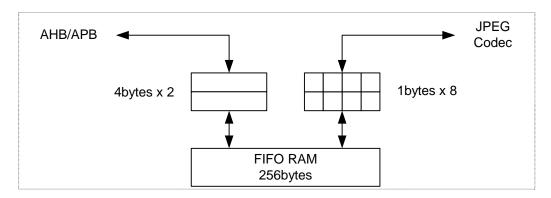

| 8.5.5.1 JPEG FIFO                                              |     |

| 8.5.5.2 JPEG Line Buffer                                       |     |

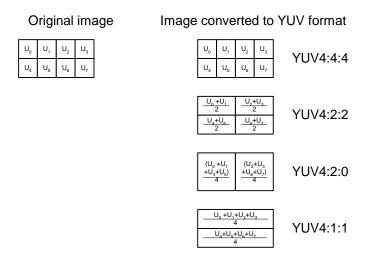

| 8.5.5.3 YUV Format Converter                                   |     |

| 8.5.5.4 JPEG Module Interrupts                                 |     |

| 8.5.5.5 JPEG 180° Rotation Encode                              |     |

| 8.5.5.6 Software Reset                                         |     |

| 8.5.5.7 Marker Fast Output Mode                                |     |

| 8.5.6 Example of Sequence                                      |     |

| 8.5.6.1 JPEG Encoding of Camera Image (Single Frame)           | 99  |

| 8.5.6.2 Termination                                            | 101 |

| 9. JPEG_DMAC (JDMA)                                            | 102 |

| 9.1 Description                                                |     |

| 9.2 Block Diagram                                              |     |

| 9.3 External Pins                                              |     |

|                                                                |     |

| 9.4 Registers                                                  |     |

| 9.4.1 List of Registers9.4.2 Detailed Description of Registers |     |

| ·                                                              |     |

| 10. DMA Controller 2 (DMAC2)                                   | 108 |

| 10.1 Description                                               | 108 |

| 10.2 Block Diagram                                             |     |

| 10.3 External Pins                                             |     |

| 10.4 Registers                                                 |     |

| 10.4.1 List of Registers                                       |     |

| 10.4.2 Detailed Description of Registers                       |     |

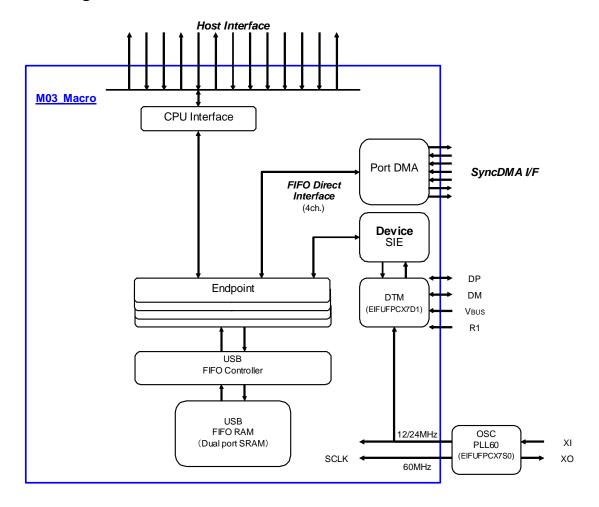

| 11. USB HS-Device                                              |     |

|                                                                |     |

| 11.1 Description                                               |     |

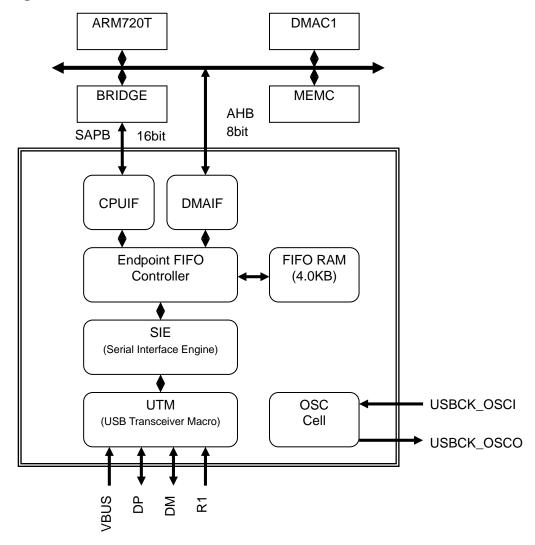

| 11.2 Block Diagram                                             | 115 |

| 11.3 Features                                                  | 116 |

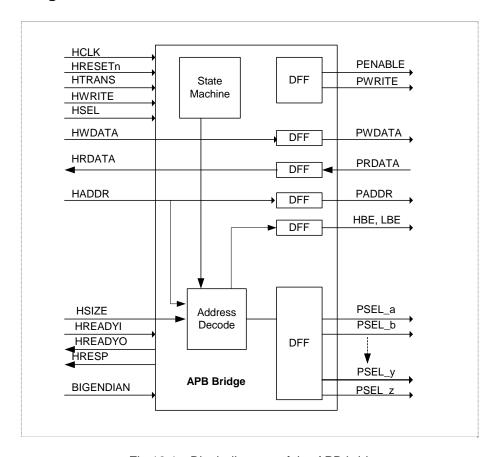

| 12. APB BRIDGE (APB)                                           | 117 |

| 12.1 Description                                               |     |

| 12.2 Block Diagram                                             |     |

| 12.3 External Pins                                             |     |

|                                                                |     |

| 12.4 Registers1                                      |     |

|------------------------------------------------------|-----|

| 12.4.1 List of Registers                             |     |

| 12.4.2 Detailed Description of Registers             |     |

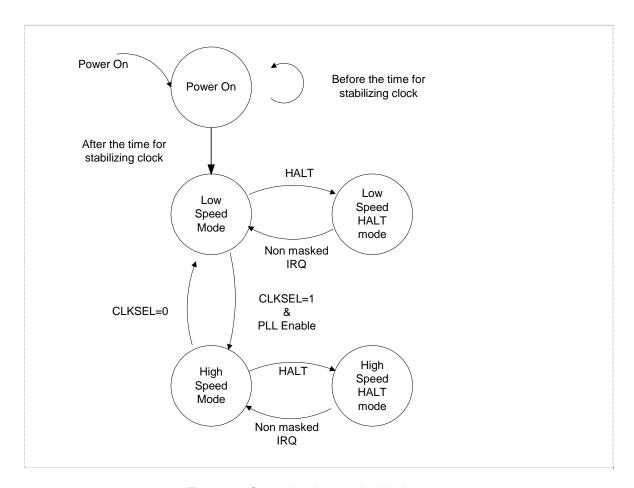

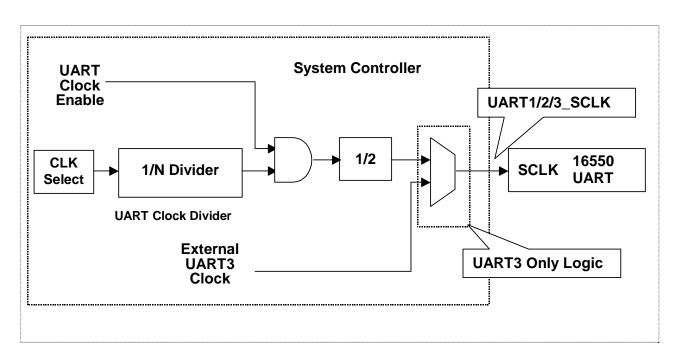

| 13. System Controller (SYS)1                         | 21  |

| 13.1 Description1                                    |     |

| 13.2 Operation mode                                  |     |

| 13.2.1 Power-On State                                |     |

| 13.2.2 Low-Speed Mode                                |     |

| 13.2.3 Low-Speed HALT Mode1                          | 122 |

| 13.2.4 High-Speed Mode1                              |     |

| 13.2.5 High-Speed HALT Mode1                         | 122 |

| 13.3 External Pins1                                  | 123 |

| 13.4 Registers1                                      | 123 |

| 13.4.1 List of Registers1                            |     |

| 13.4.2 Detailed Description of Registers1            |     |

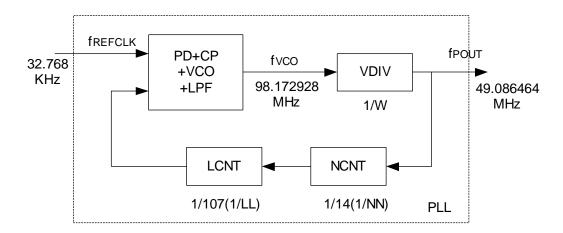

| 13.5 Appendix A: PLL Setting Example1                | 137 |

| 13.6 Appendix B: PLL Parameter table1                | 138 |

| 13.7 Appendix C: Memory Map after Remapping1         | 139 |

| 13.7.1 Memory Map after Remapping (AHB1)1            |     |

| 13.7.2 Memory Map after Remapping (AHB2)1            | 141 |

| 13.8 Appendix D: Clock Control Block Diagram1        | 143 |

| 13.9 Appendix D: Example of Settings for UART Clock1 | 144 |

| •                                                    |     |

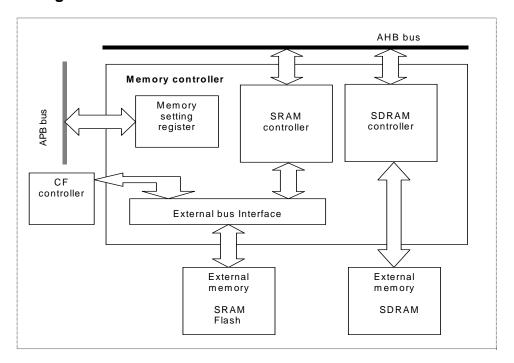

| 14. MEMORY CONTROLLER (MEMC)1                        |     |

| 14.1 Description                                     |     |

| 14.1.1 SRAM Controller                               |     |

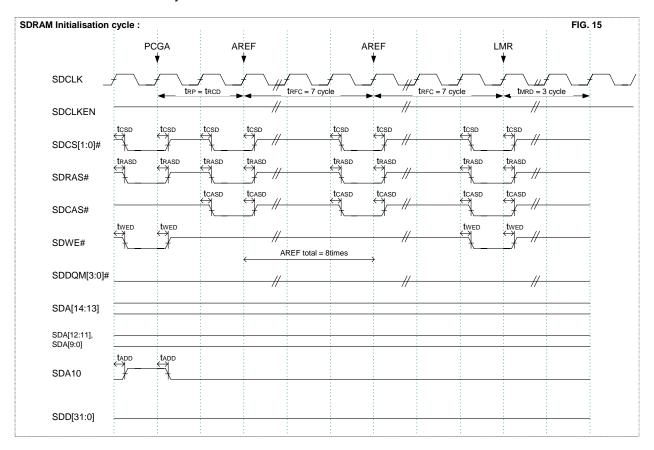

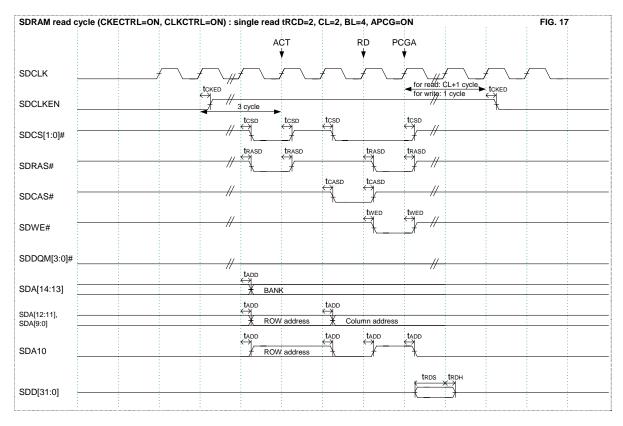

| 14.1.2 SDRAM Controller                              |     |

| 14.1.3 External Bus interface Module                 |     |

| _                                                    |     |

| 14.3 External Pins                                   |     |

| 14.4 Memory controller                               |     |

| 14.4.1 Number of Devices                             |     |

| 14.4.2 External Memory Width                         |     |

|                                                      |     |

| <b>14.5 SRAM control</b>                             |     |

| 14.5.1 Setting of Timing                             |     |

|                                                      |     |

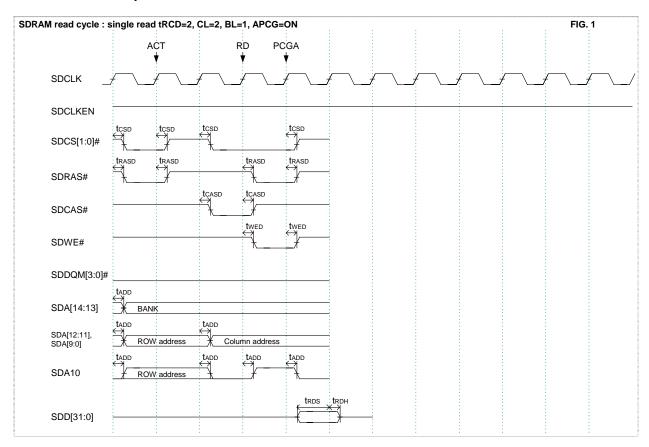

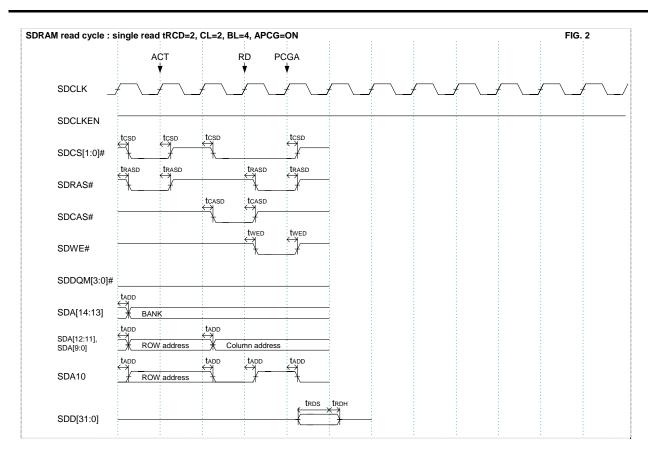

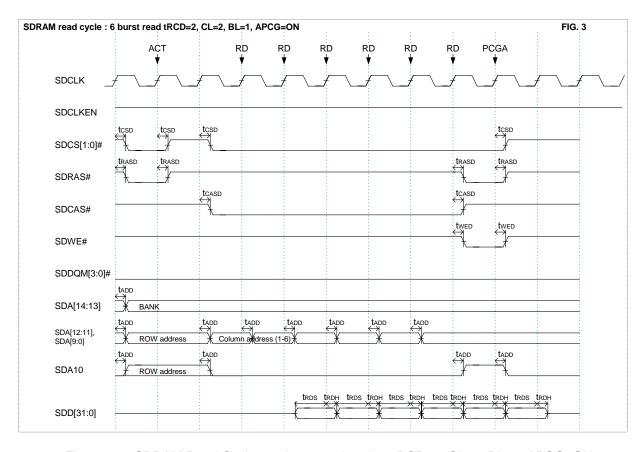

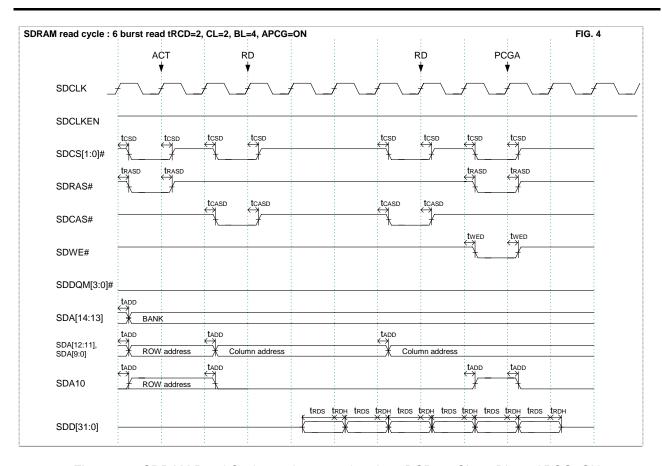

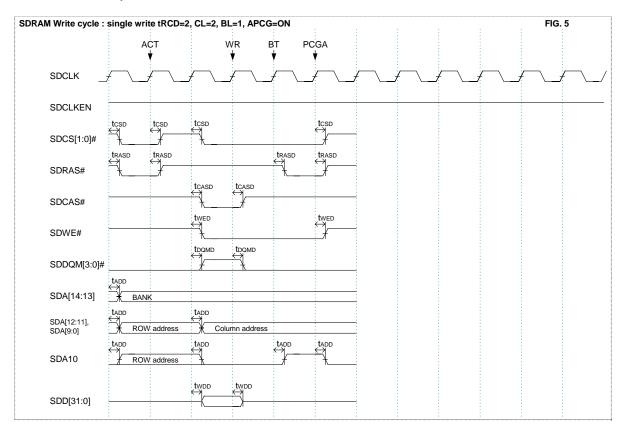

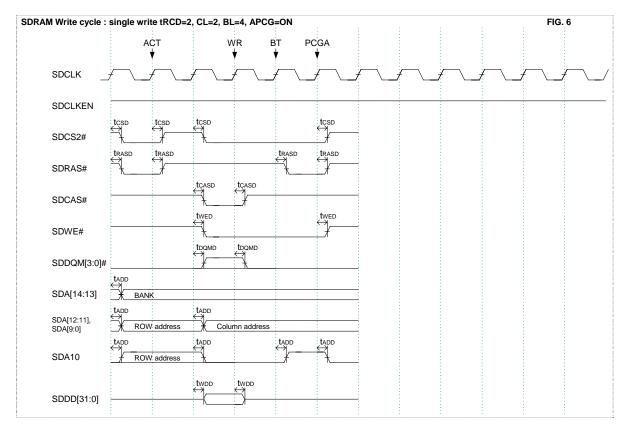

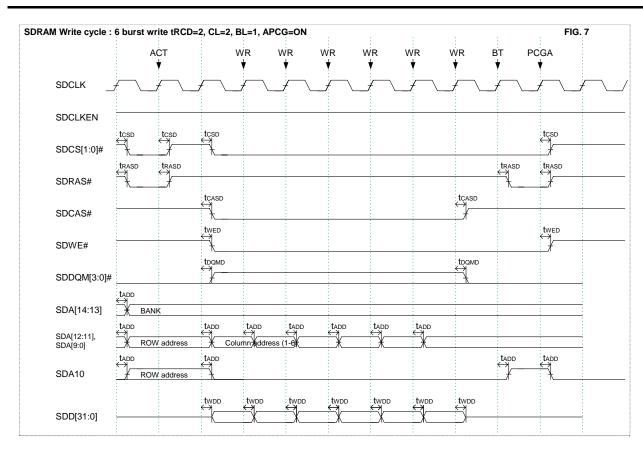

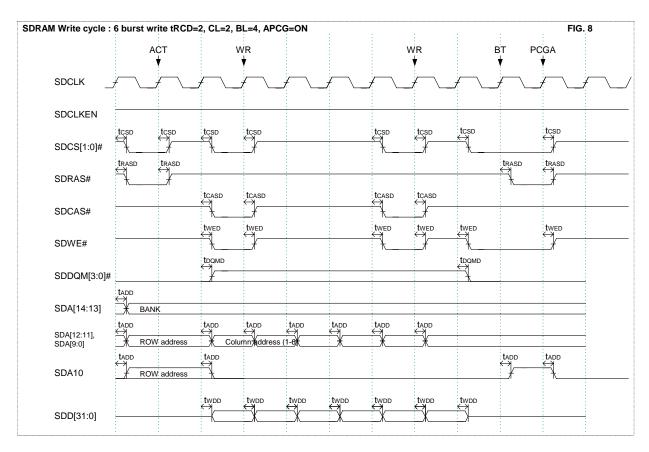

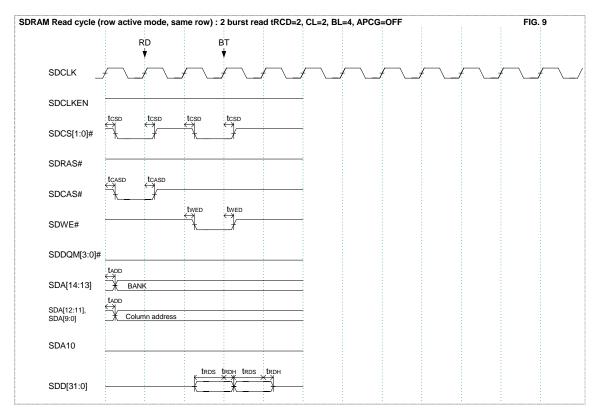

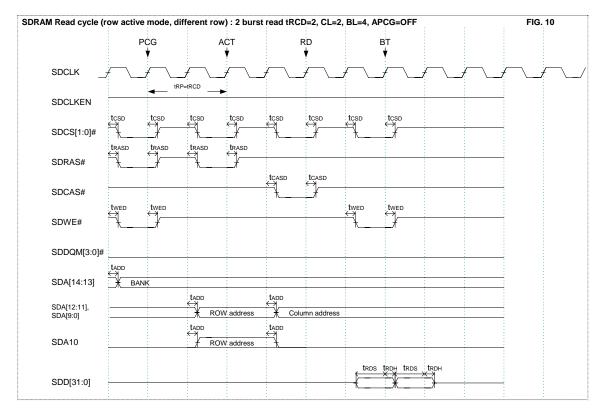

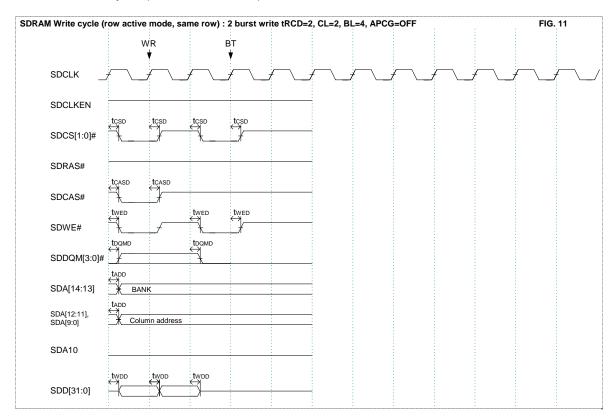

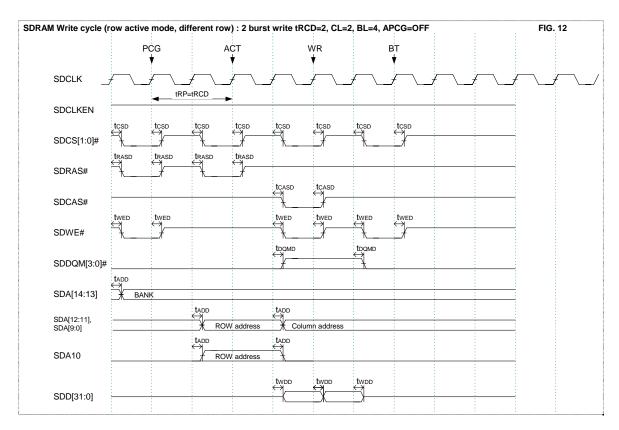

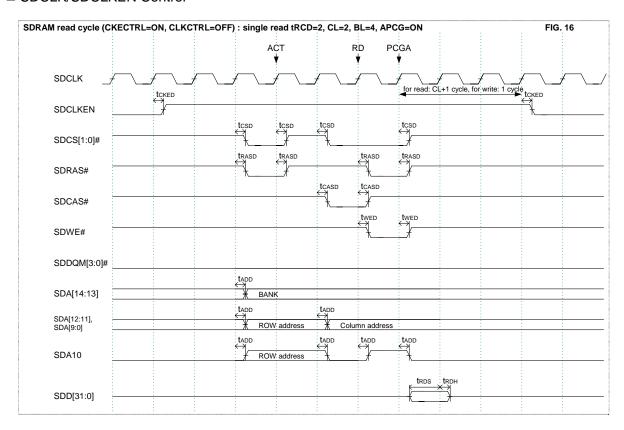

| 14.6 SDRAM control                                   |     |

| 14.6.2 Compatibility with Burst                      |     |

| 14.6.3 Setting of Auto-Precharge                     |     |

| 14.6.4 Reduction of Power Consumption                |     |

| 14.6.5 Stopping Memory Clock1                        |     |

| 14.6.6 Support of Energy-Saving Mode1                |     |

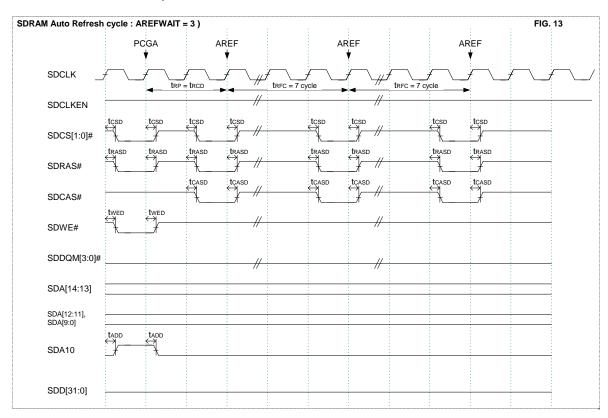

| 14.6.7 Control of Auto-Refresh1                      |     |

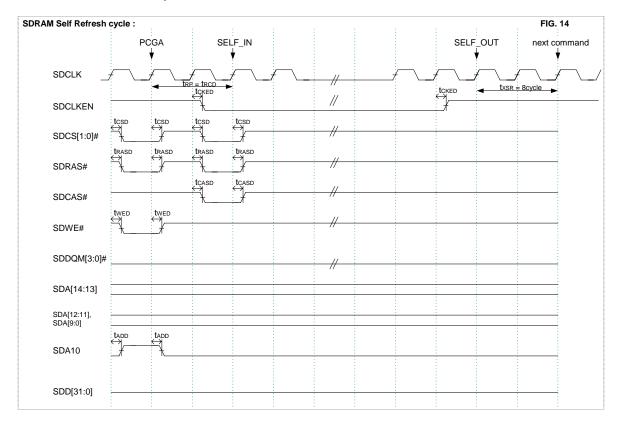

| 14.6.8 Control of Self-Refresh                       |     |

| 14.6.9 Status Register1                              |     |

| 14.7 Registers1                                      |     |

| 14.7.1 List of Registers                             |     |

| 14.7.2 Detailed Description of Registers1            | 151 |

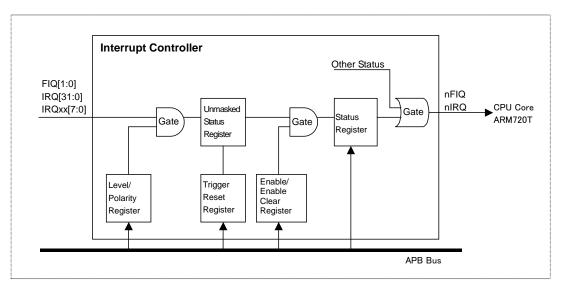

| 15. INTERRUPT CONTROLLER (INT)1                      | 58  |

| 15.1 Description1                                    |     |

| •                                                    | 160 |

| 15.3 FIQ                                                                                       | 160               |

|------------------------------------------------------------------------------------------------|-------------------|

| 15.4 IRQ                                                                                       | 160               |

| 15.5 External Pins                                                                             | 161               |

| 15.6 Registers                                                                                 | 161               |

| 15.6.1 List of Registers                                                                       |                   |

| 15.6.2 Detailed Description of Registers                                                       | 162               |

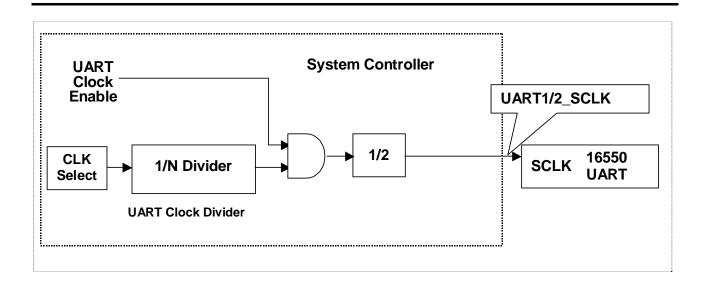

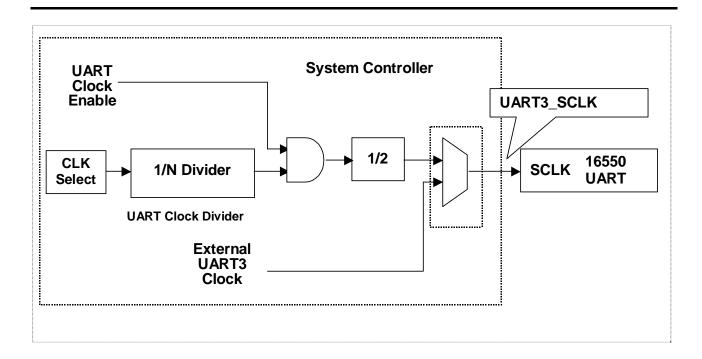

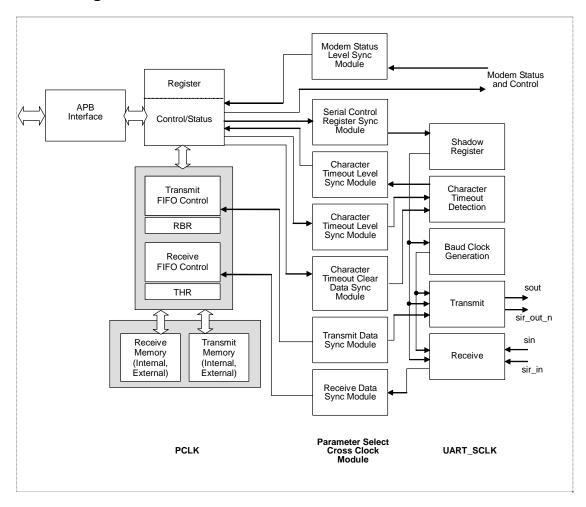

| I6. UART1/2/3                                                                                  | 173               |

| 16.1 Description                                                                               | 173               |

| 16.2 Block Diagram                                                                             | 173               |

| 16.3 External Pins                                                                             | 174               |

| 16.4 Description of Registers                                                                  | 175               |

| 16.4.1 List of Registers                                                                       |                   |

| 16.4.2 Precautions on Register Access                                                          |                   |

| 16.4.3 Detailed Description of Registers                                                       |                   |

| 16.5 Usage Restrictions for This UART1/2/3                                                     |                   |

| _                                                                                              |                   |

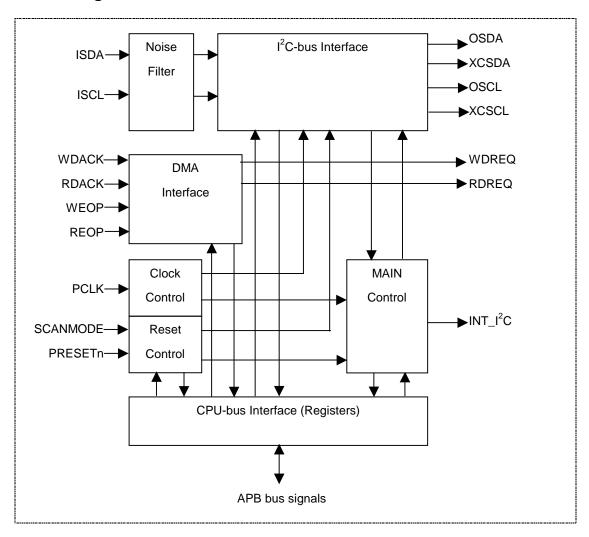

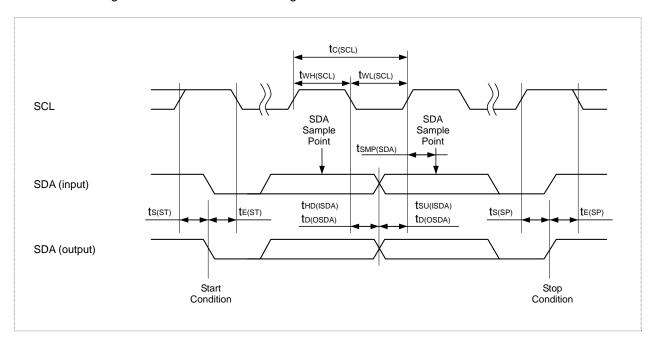

| 17. I <sup>2</sup> C Single Master Core Module (I <sup>2</sup> C)                              |                   |

| 17.1 Description                                                                               |                   |

| 17.1.1 Master Mode                                                                             |                   |

| 17.1.2 Glave Mode                                                                              |                   |

| 17.3 External Pins                                                                             |                   |

| 17.4 Registers                                                                                 | _                 |

| 17.4.1 List of Registers                                                                       |                   |

| 17.4.2 Detailed Description of Registers                                                       |                   |

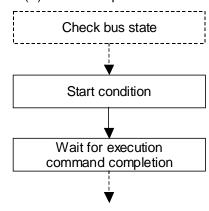

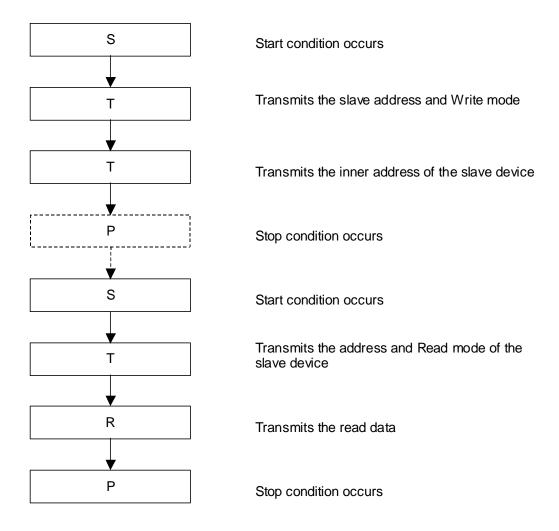

| 17.5 Explanation of Operation (Example of Use: Bus Control Command)                            | 202               |

| 17.5.1 Start (S) Flow Example                                                                  |                   |

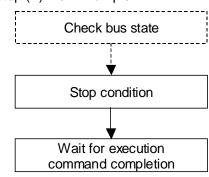

| 17.5.2 Stop (P) Flow Example                                                                   |                   |

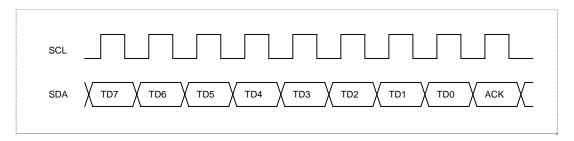

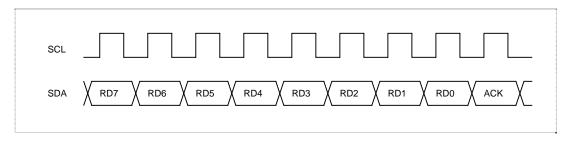

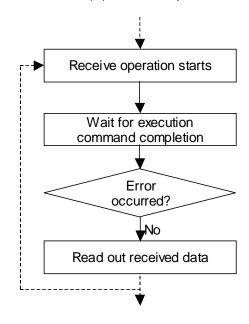

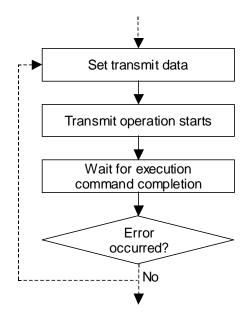

| 17.5.4 Transfer (T) Flow Example                                                               |                   |

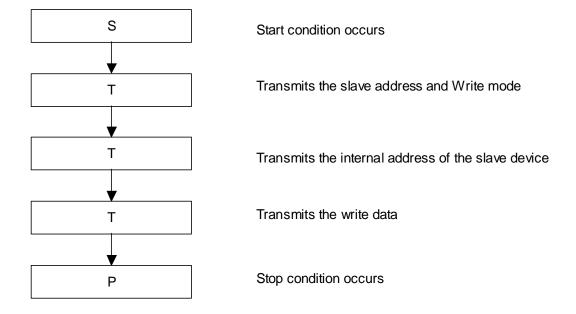

| 17.5.5 Example of Sequence When Writing to Slave Device                                        |                   |

| 17.5.6 Example of Sequence When Reading from Slave                                             |                   |

| 17.6 Usage Restrictions for This I <sup>2</sup> C Single Master Core Module (I <sup>2</sup> C) | 204               |

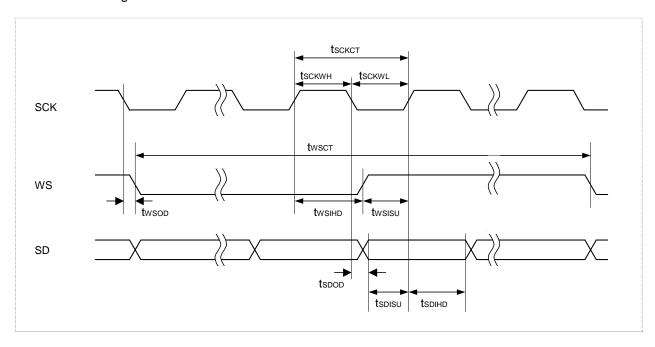

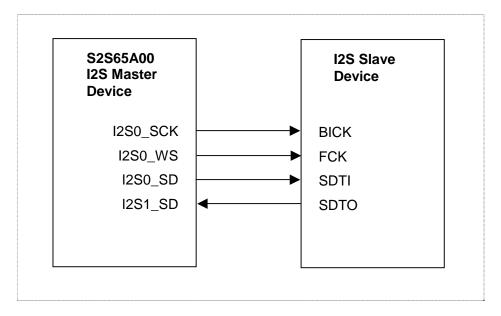

| 18. I <sup>2</sup> S (I2S)                                                                     | 205               |

| 18.1 Description                                                                               |                   |

| 18.1.1 Function                                                                                |                   |

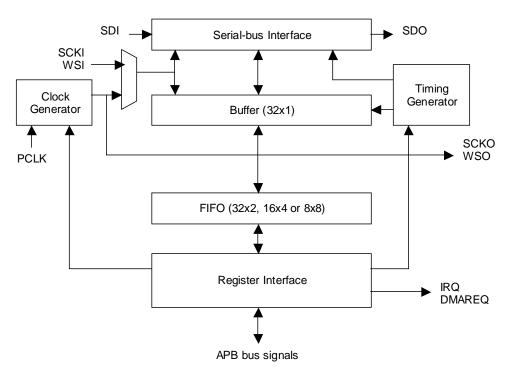

| 18.2 Block Diagram                                                                             | 205               |

| 18.3 External Pins                                                                             | 206               |

| 18.4 Description of Registers                                                                  | 206               |

| 18.4.1 List of Registers                                                                       |                   |

| 18.4.2 Detailed Description of Registers                                                       |                   |

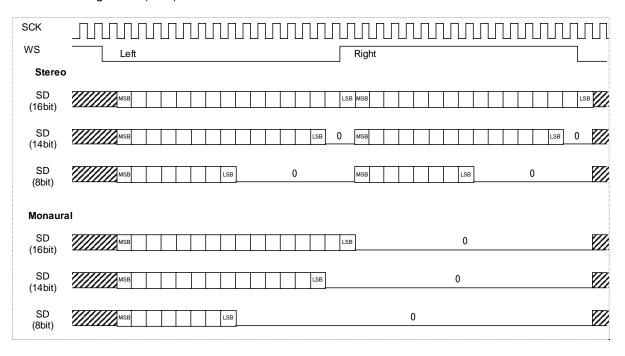

| 18.5 Functional description                                                                    | 214               |

| 18.5.1 I <sup>2</sup> S Timing Chart (32fs)                                                    | 14<br>21 <i>4</i> |

| 18.5.3 DMA Transfer                                                                            |                   |

| 18.5.4 Interrupt to INTC                                                                       | 215               |

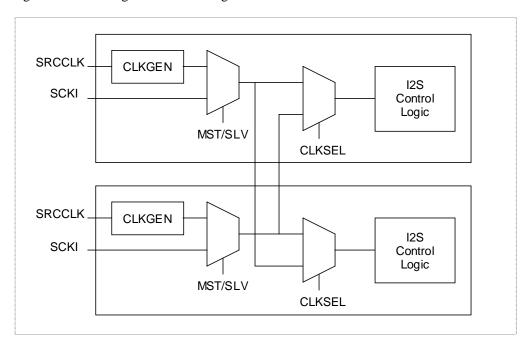

| 18.5.5 Clock Select (Clock Sharing)                                                            | 215               |

| 18.5.6 Monaural-to-Stereo Conversion Function                                                  |                   |

| 18.6 Setup example                                                                             | 216               |

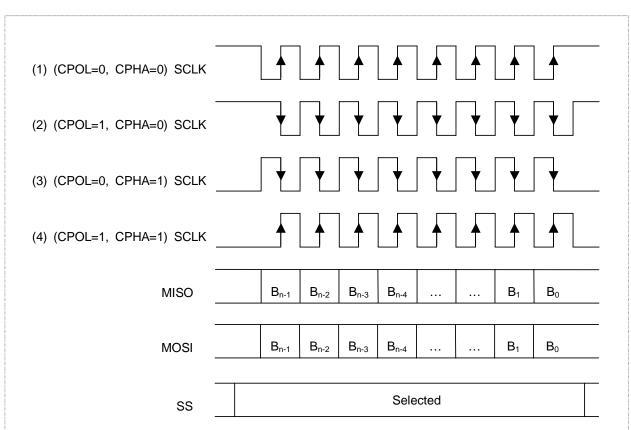

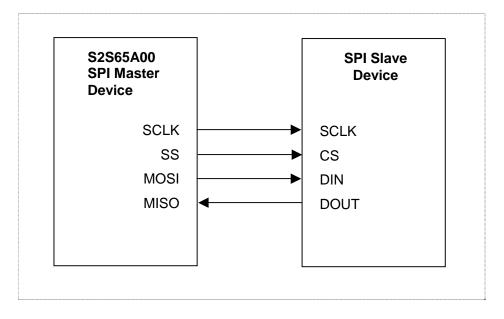

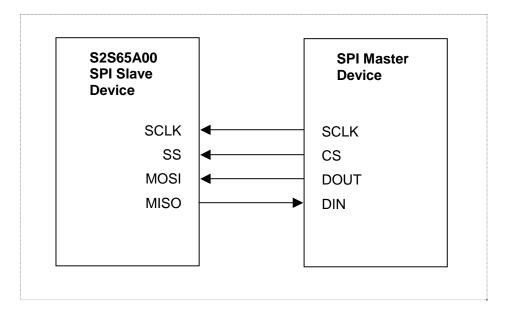

| 19. SERIAL PERIPHERAL INTERFACE (SPI)                                                          | 047               |

| 19.1 Description                                          |     |

|-----------------------------------------------------------|-----|

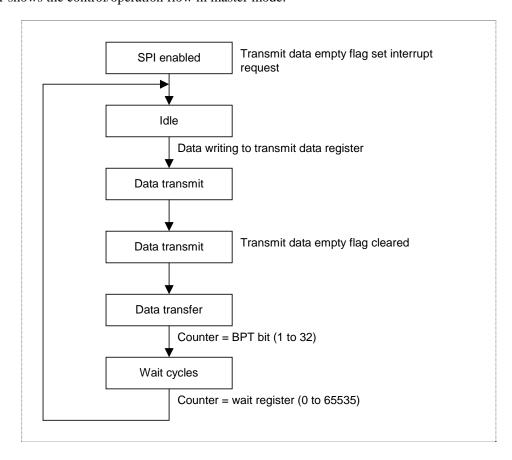

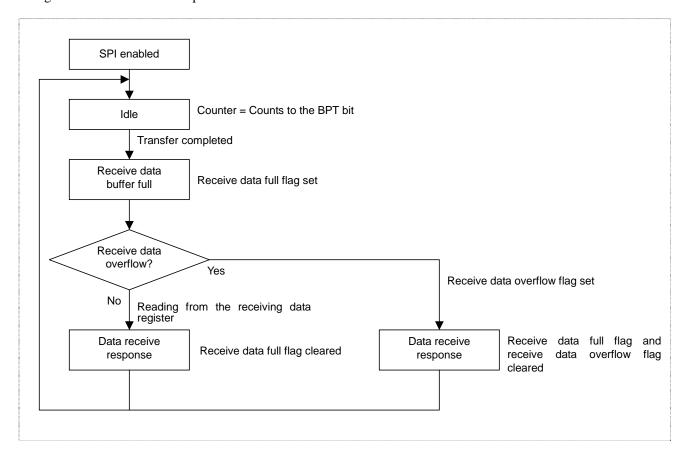

| 19.1.1 Master Mode                                        |     |

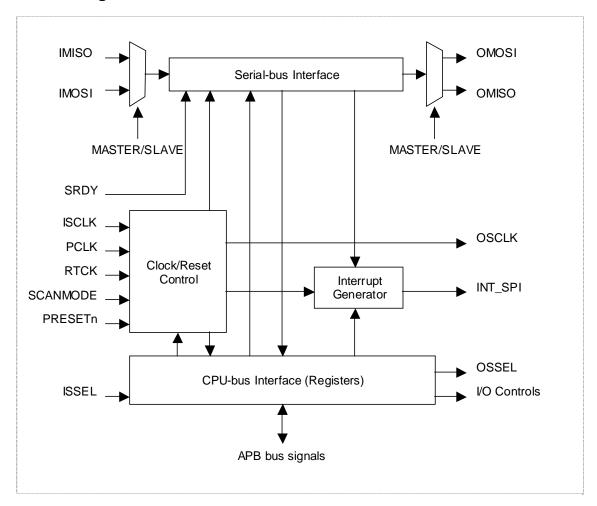

| 19.2 Block Diagram                                        |     |

| 19.3 External Pins                                        |     |

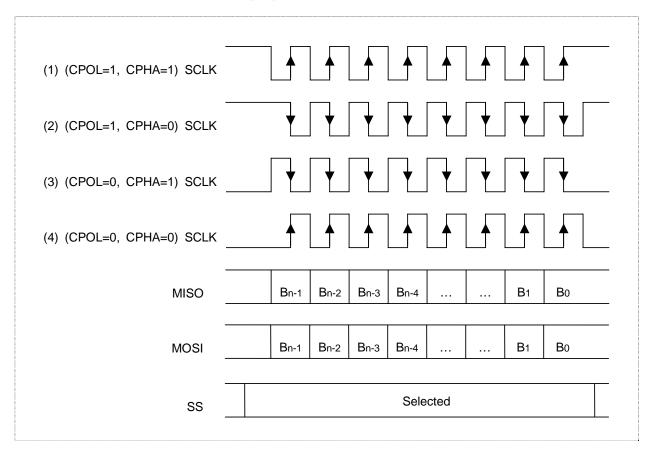

| 19.4 Clock and Data Transfer Timing                       |     |

| 19.5 Description of Registers                             |     |

| 19.5.1 List of Registers                                  |     |

| 19.5.2 Detailed Description of Registers                  | 222 |

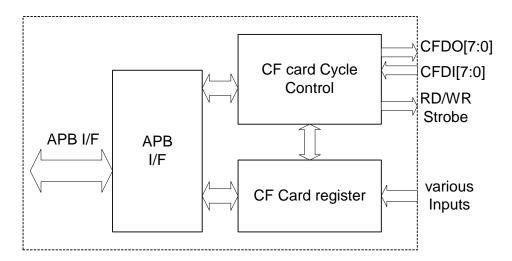

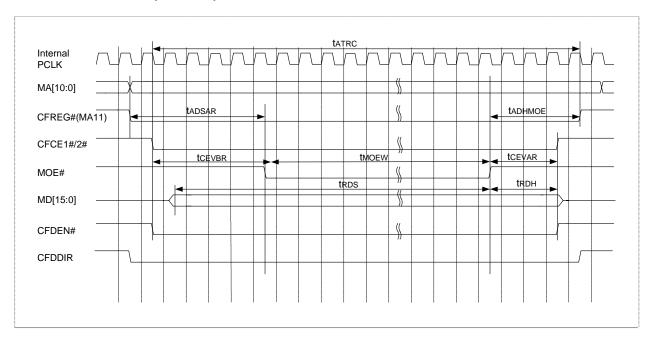

| 20. Compact Flash (CF) Card Interface                     | 228 |

| 20.1 Overview                                             | 228 |

| 20.2 Block Diagram                                        |     |

| 20.3 CF Card I/F Space Assignment                         |     |

| 20.4 External Pins                                        |     |

| 20.5 Registers                                            |     |

| 20.5.1 List of Registers                                  |     |

| 20.6 Application Restrictions of CF Card Interface        |     |

| 21. SD Memory Card Interface                              |     |

| 21. 3D Memory Card Interface                              |     |

|                                                           |     |

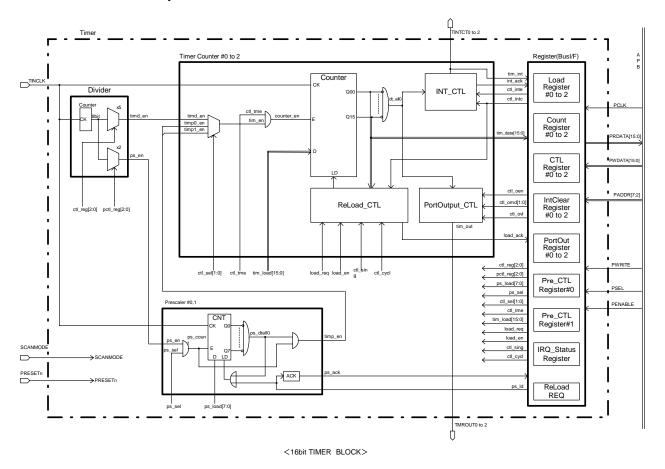

| 22. Timer A (TIMA)                                        |     |

| 22.1 Overview                                             |     |

| 22.2 Block Diagram                                        |     |

| 22.3 External Pins                                        |     |

| 22.4 Registers                                            |     |

| 22.4.2 Detailed Description of Registers                  |     |

| 22.5 Setting the Load Value in Each Mode                  | 247 |

| 22.5.1 Timer Counter Modes                                |     |

| 22.6 Timer Internal Clock Setting Examples (1 KHz, 1 MHz) |     |

| 22.6.1 Divider and Prescaler Settings                     |     |

| 22.7 Timing Diagrams                                      |     |

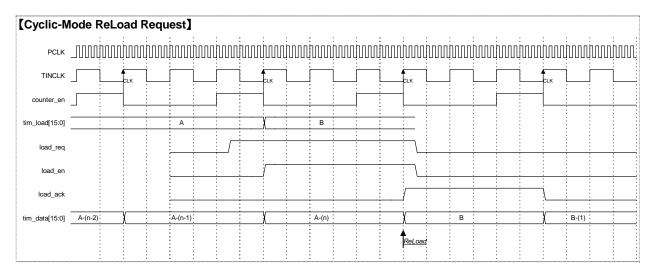

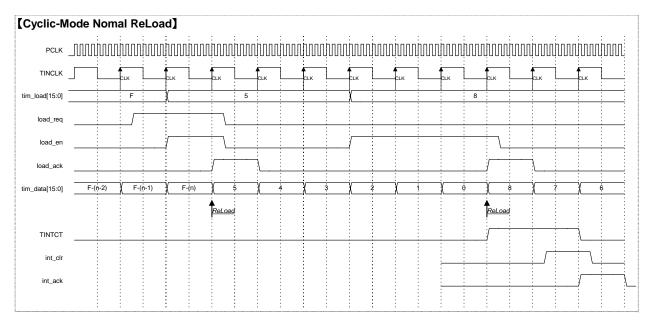

| 22.7.2 Normal Reloading in Cyclic Mode                    | 249 |

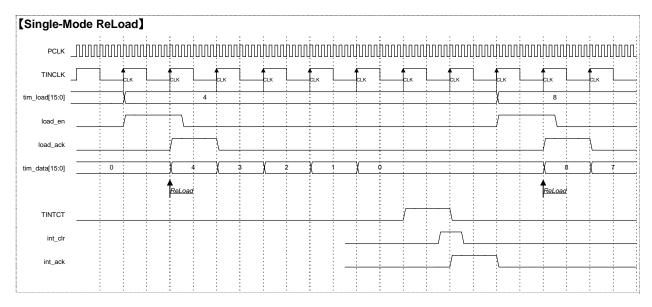

| 22.7.3 Normal Reloading in Single Mode                    |     |

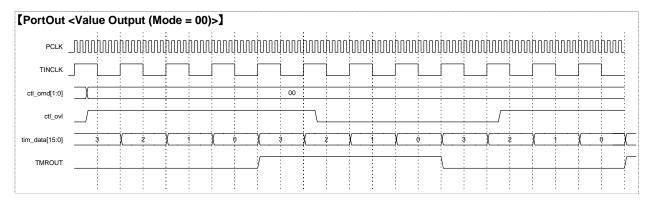

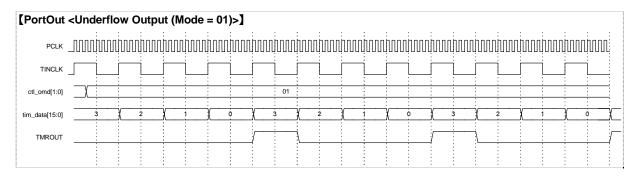

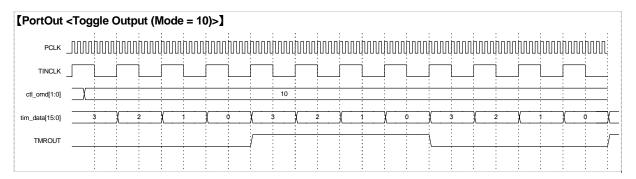

| 22.7.4 Port Outputs                                       |     |

| 23. Timer B (TIMB)                                        |     |

| 23.1 Description                                          |     |

| 23.2 Features                                             |     |

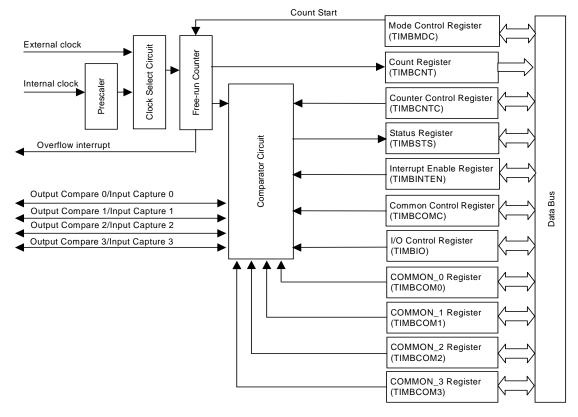

| 23.3 Block Diagram                                        |     |

| 23.4 External Pins                                        |     |

| 23.5 Registers                                            |     |

| 23.5.2 Detailed Description of Registers                  |     |

| 23.6 Explanation of Operations                            |     |

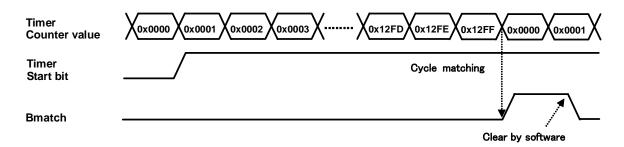

| 23.6.1 Count Operations                                   | 262 |

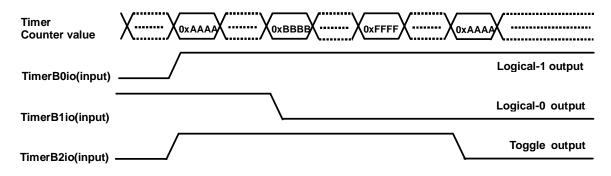

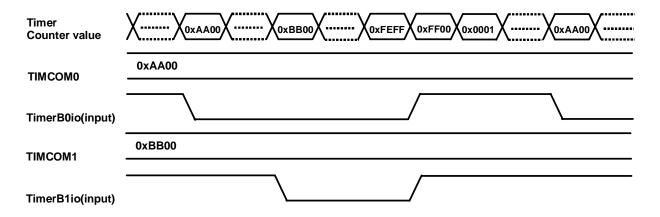

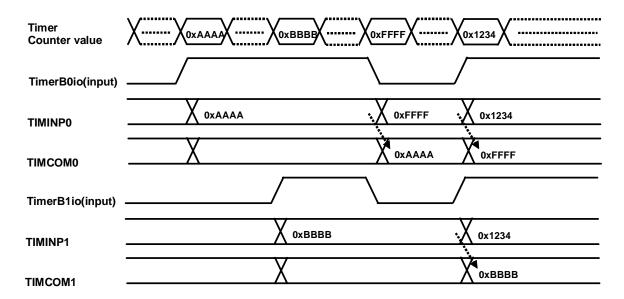

| 23.6.2 Timer I/O Functions                                | 263 |

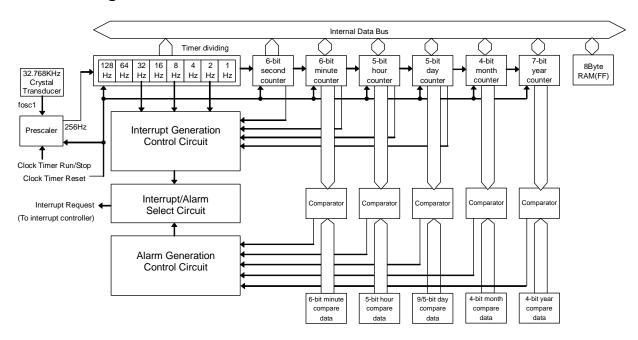

| 24 Real-Time Clock (RTC)                                  | 266 |

| 24.1 Description                                            | 266 |

|-------------------------------------------------------------|-----|

| 24.2 Block Diagram                                          | 266 |

| 24.3 External Pins                                          | 266 |

| 24.4 Registers                                              | 267 |

| 24.4.1 List of Registers                                    |     |

| 24.4.2 Detailed Description of Registers                    |     |

| 24.5 Setting RTC Registers                                  | 275 |

| 24.5.1 Initialization after Power-On                        |     |

| 24.5.2 Stop and Restart of Operations                       |     |

| 24.5.3 Repeated Setting without Operation Stop              |     |

| 24.5.4 Repeated Setting during Operation after System Reset | 276 |

| 24.5.5 Cautions during Programming                          | 276 |

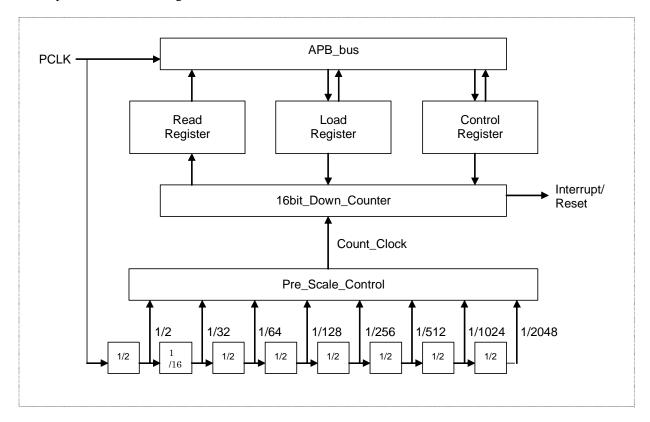

| 25. Watchdog Timer (WDT)                                    | 277 |

| 25.1 Description                                            |     |

| 25.2 Block Diagram                                          |     |

|                                                             |     |

| 25.3 External Pins                                          | _   |

| 25.4 Registers                                              |     |

| 25.4.1 List of Registers                                    |     |

| 25.4.2 Detailed Description of Registers                    | 278 |

| 26. GPIO                                                    | 281 |

| 26.1 Description                                            | 281 |

| 26.2 External Pins                                          |     |

|                                                             |     |

| 26.3 Registers                                              |     |

| 26.3.2 Detailed Description of Registers                    |     |

| 26.3.2.1 GPIOA Registers                                    |     |

| 26.3.2.2 GPIOA Register                                     |     |

| 26.3.2.3 GPIOC Register                                     |     |

| 26.3.2.4 GPIOD Register                                     |     |

| 26.3.2.5 GPIOE Register                                     |     |

| 26.3.2.6 GPIOF Register                                     |     |

| 26.3.2.7 GPIOG Register                                     |     |

| 26.3.2.8 GPIOH Register                                     |     |

| 26.3.2.9 GPIOI Registers                                    |     |

| 26.3.2.10 GPIOJ Register                                    |     |

| 26.3.2.11 GPIOK Register                                    |     |

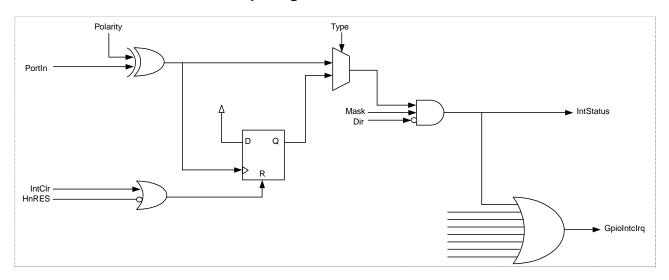

| 26.4 GPIOA and GPIOB Interrupt Logic                        | 298 |

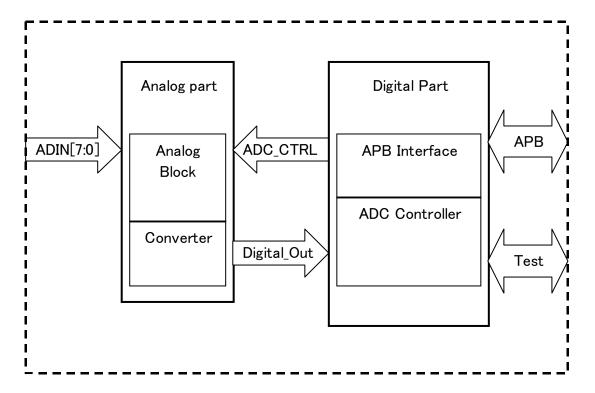

| 27. A/D Controller (ADC)                                    | 200 |

| 27.1 Description                                            |     |

| •                                                           |     |

| 27.2 Block Diagram                                          |     |

| 27.3 External Pins                                          |     |

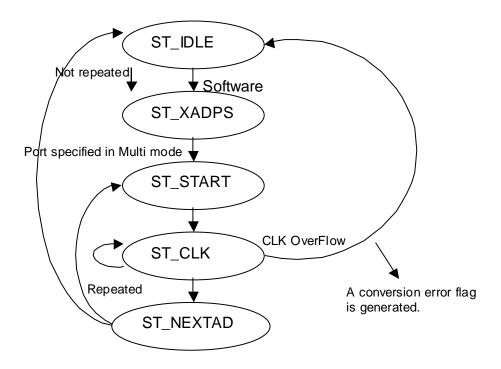

| 27.4 Operation State                                        | 300 |

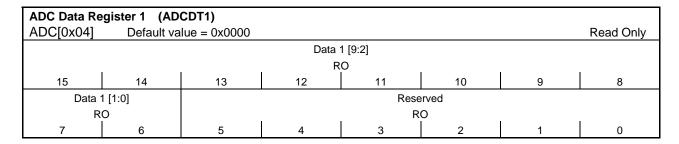

| 27.5 Registers                                              | 301 |

| 27.5.1 List of Registers                                    |     |

| 27.5.2 Detailed Description of Registers                    | 301 |

| 27.6 Application Examples                                   | 306 |

| 27.7 Input Voltages and Converted Data Values               |     |

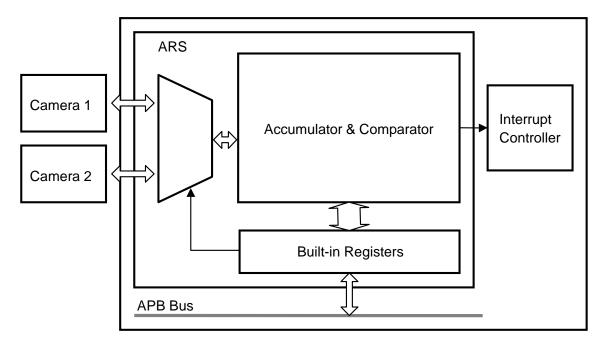

| 28. Area Sensor (ARS)                                       |     |

|                                                             |     |

| 28.1 Description                                            |     |

| 28.1.1 Functions                                            | 308 |

| 28.2 Block Diagram                                                            | 309 |

|-------------------------------------------------------------------------------|-----|

| 28.3 External Pins                                                            | 309 |

| 28.4 Description of Registers                                                 |     |

| 28.4.1 List of Registers                                                      |     |

| 28.4.2 Detailed Description of Registers                                      |     |

| 29. Absolute Maximum Ratings                                                  | 313 |

| 29.1 Absolute Maximum Ratings                                                 |     |

|                                                                               |     |

| 29.2 Recommended Operating Conditions (Dual Power Supplies, 3.3V I/O Buffers) |     |

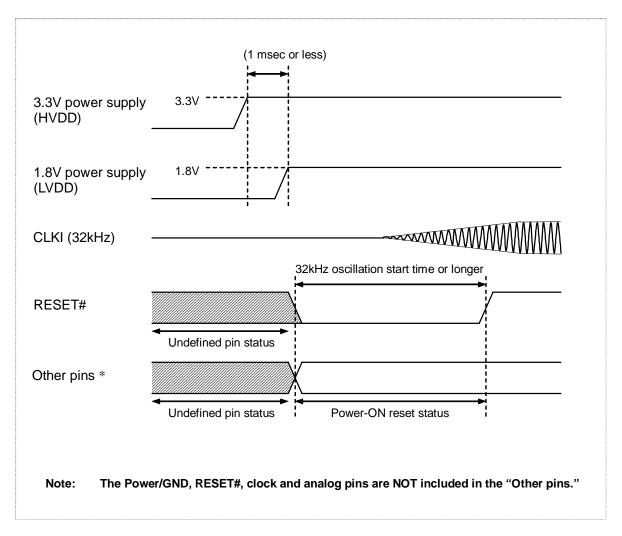

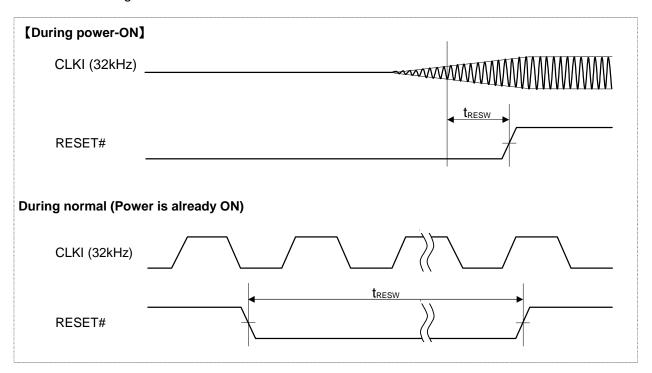

| 29.3 Power-ON Timing                                                          |     |

| 29.4 Power-OFF Timing                                                         | 314 |

| 30. Electrical Characteristics                                                | 315 |

| 30.1 DC Characteristics                                                       | 315 |

| 30.2 AC Characteristics                                                       | 316 |

| 30.2.1 AC Characteristics Measuring Conditions                                |     |

| 30.2.2 AC Characteristics Signal Timing List                                  |     |

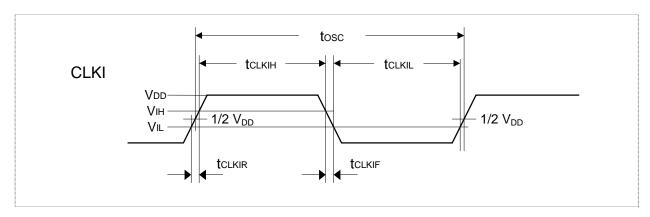

| 30.2.2.1 Clock Timing                                                         | 316 |

| 30.2.2.2 CPU Control Signal Timing                                            |     |

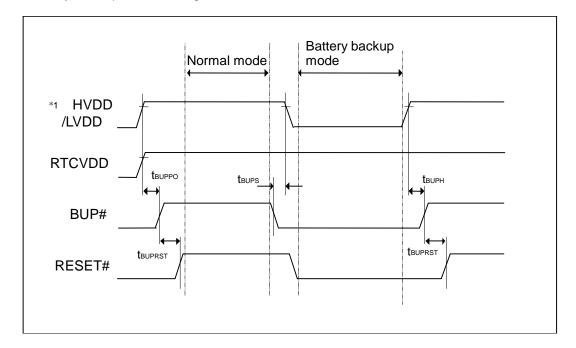

| 30.2.2.3 Battery Backup Mode Timing                                           |     |

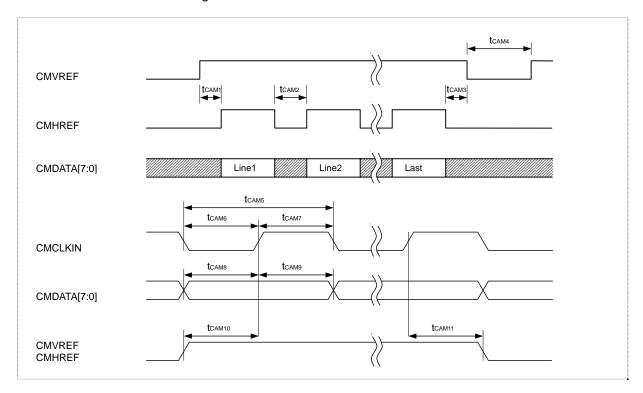

| 30.2.2.4 Camera Interface (CAM) Timing                                        |     |

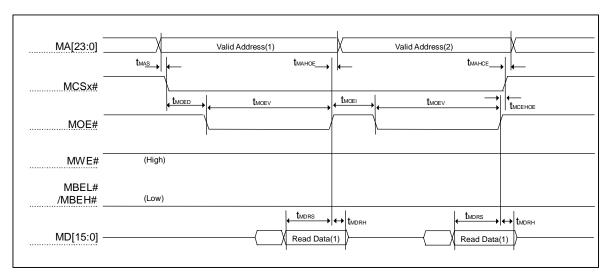

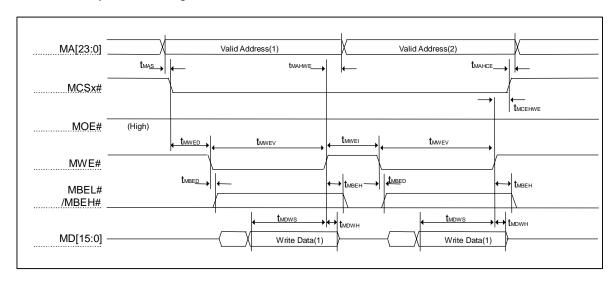

| 30.2.2.5 Memory Controller (MEMC) Timing                                      |     |

| 30.2.2.6 I <sup>2</sup> C Single Master Core Module (I2C) Timing              |     |

| 30.2.2.7 I <sup>2</sup> STiming                                               |     |

| 30.2.2.8 Serial Peripheral Device Interface (SPI) Timing                      |     |

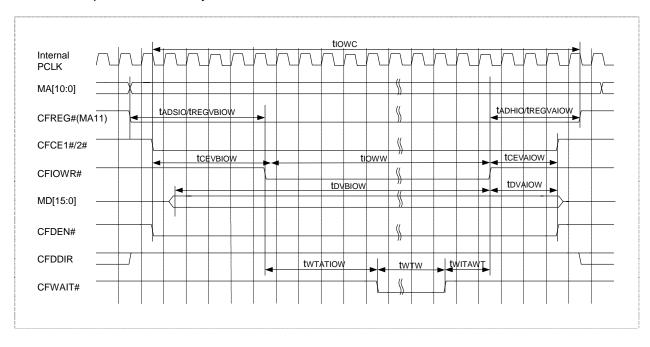

| 30.2.2.9 Compact Flash Memory Interface (CF) Timing                           |     |

| 30.2.3 Timing Charts                                                          |     |

| 30.2.3.2 CPU Control Signal Timing                                            |     |

| 30.2.3.3 Battery Backup Mode Timing                                           |     |

| 30.2.3.4 Camera Interface Timing                                              |     |

| 30.2.3.5 Memory Interface Controller                                          |     |

| 30.2.3.6 I2C Single Master Core Module Timing                                 |     |

| 30.2.3.7 I2STiming                                                            |     |

| 30.2.3.8 Serial Peripheral Device Interface Timing                            |     |

| 30.2.3.9 Compact Flash Memory Interface (CF) Timing                           | 340 |

| 31. External Connection Examples (Reference)                                  | 343 |

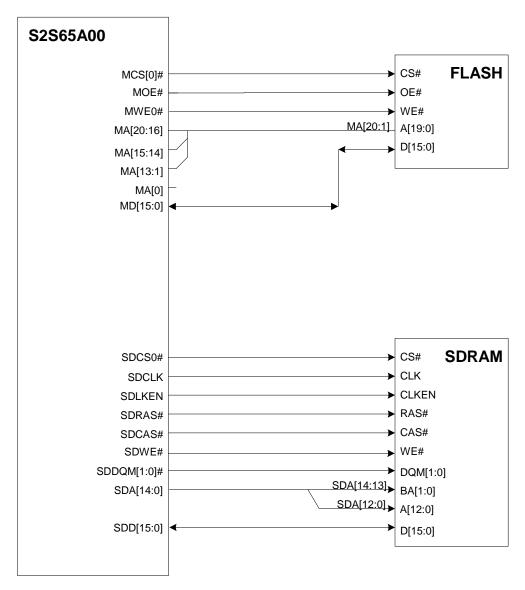

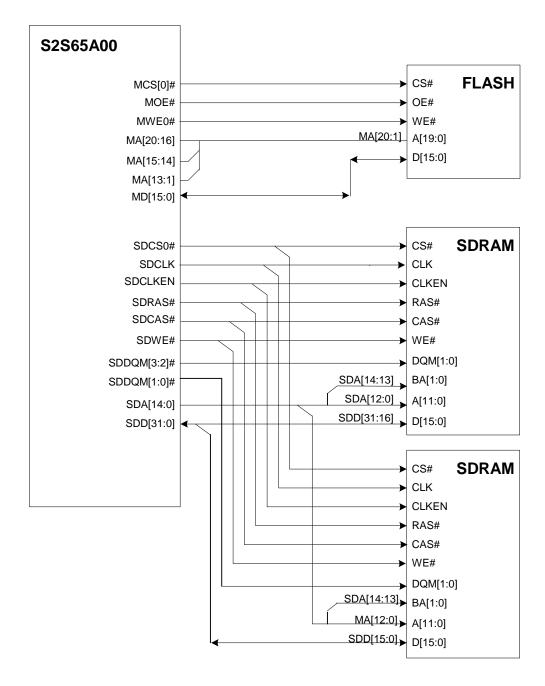

| 31.1 Memory Connection Examples                                               |     |

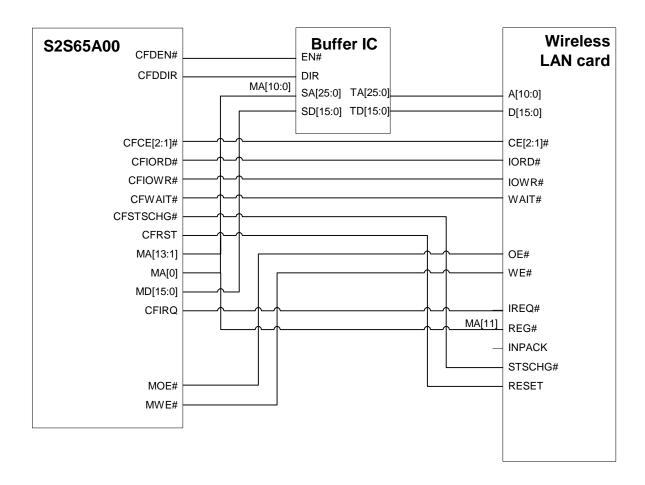

| 31.2 Compact Flash Memory Connection Example (for 16-Bit Bus Support Model)   |     |

| 31.3 Serial Peripheral Device Interface (SPI) Connection Examples             |     |

| 31.3.1 Master Mode                                                            |     |

| 31.3.2 Slave Mode                                                             |     |

| 31.4 I <sup>2</sup> S Connection Examples                                     |     |

| 31.4.1 Master Mode                                                            |     |

| 31.4.2 Slave Mode                                                             |     |

|                                                                               |     |

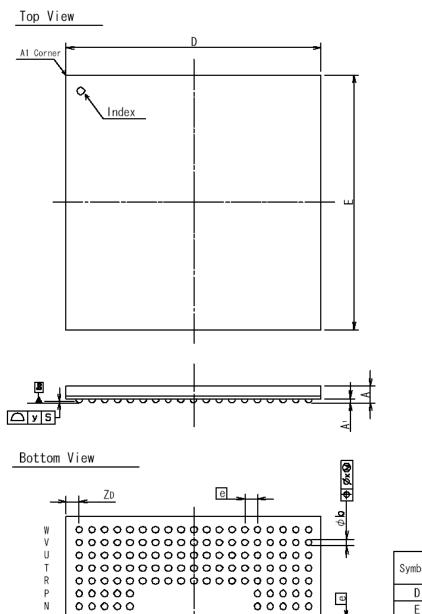

| 32. External Dimensions                                                       |     |

| 32.1 Plastic TFBGA 280pin Body size 16x16x1.2mm (PFBGA16U-280)                |     |

| 33. Revision History                                                          | 349 |

| Annandiy 1 S2S65A00 Internal Pagister List                                    | 359 |

# **Appendix 2 USB Device Controller**

## < Table of Contents >

| A2.1 Sc       | ope                                   | 376 |

|---------------|---------------------------------------|-----|

| A2.2 Overvi   | ew                                    | 376 |

| A2.3 Block I  | Diagram                               | 376 |

| A2.4 Pin Lis  | st                                    | 377 |

| A2.5 Registe  | er                                    | 378 |

| A2.5.1        | Register List                         | 378 |

| A2.5.2        | Register Detail Description           | 382 |

| A2.5.2.1      | Notes on Register Access              |     |

| A2.5.2.2      | Interrupt control register            |     |

| A2.5.2.3      | Power Management Control Register     |     |

| A2.5.2.4      | MISC register                         |     |

| A2.5.2.5      | DMA Control Register                  |     |

| A2.5.2.6      | USB Control Register                  | 394 |

| A2.5.2.7      | USB FIFO Setting Register             | 423 |

| A2.6 Function | onal description                      | 432 |

| A2.6.1        | Default setting                       | 432 |

| A2.6.1.1      | Access setting to the USB controller  | 432 |

| A2.6.1.2      | Interrupt setting                     | 432 |

| A2.6.1.3      | Notes on Macro Config1[0x37]          | 432 |

| A2.6.2        | USB Device Control                    | 433 |

| A2.6.2.1      | Endpoint                              | 433 |

| A2.6.2.2      | Transaction                           | 434 |

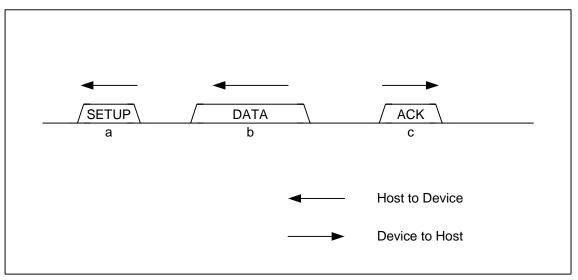

| A2.6.2.2.     | 1 SETUP Transaction                   | 436 |

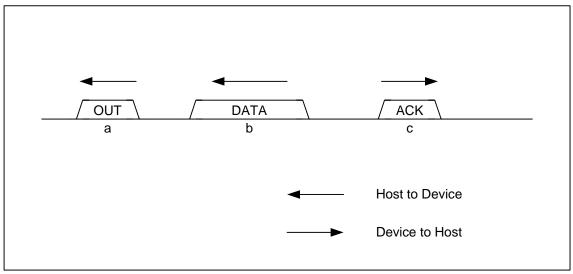

| A2.6.2.2.2    | 2 Bulk/interrupt OUT transaction      | 437 |

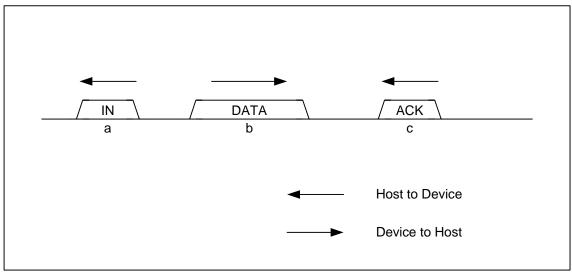

| A2.6.2.2.3    | 3 Bulk/Interrupt IN transaction       | 438 |

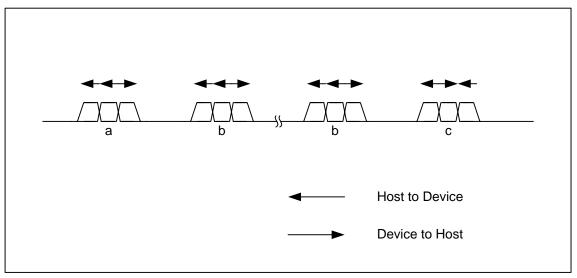

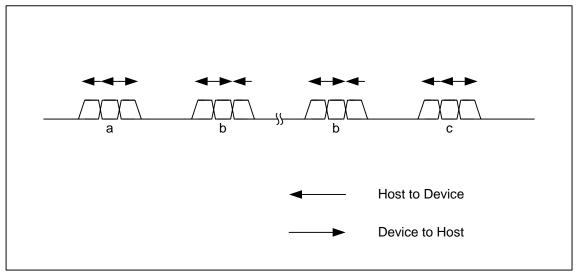

| A2.6.2.2.4    | 4 PING Transaction                    | 439 |

| A2.6.2.3      | Control Transfer                      | 440 |

| A2.6.2.3.     | 1 Setup Stage                         | 441 |

| A2.6.2.3.2    | 2 Data Stage and Status Stage         | 441 |

| A2.6.2.3.3    | <b>S</b>                              |     |

| A2.6.2.3.     |                                       |     |

| A2.6.2.4      | Bulk Transfer and Interrupt Transfer  |     |

| A2.6.2.5      | Data Flow                             |     |

| A2.6.2.5.     |                                       |     |

| A2.6.2.5.2    |                                       |     |

| A2.6.2.6      | Bulk Only Support                     |     |

| A2.6.2.6.     | • •                                   |     |

| A2.6.2.6.2    | · · · · · · · · · · · · · · · · · · · |     |

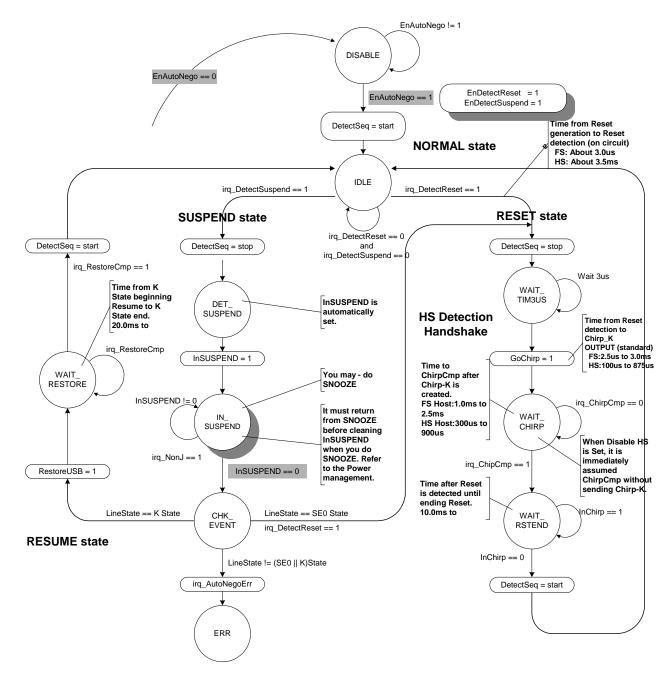

| A2.6.2.7      | Auto Negotiation Function             |     |

| A2.6.2.7.     |                                       |     |

| A2.6.2.7.     |                                       |     |

| A2.6.2.7.3    | <del>-</del>                          |     |

| A2.6.2.7.4    | <del>_</del>                          |     |

| A2.6.2.7.     | <del>_</del>                          |     |

| A2.6.2.7.0    | <del>_</del>                          |     |

| A2.6.2.7.     | <del>-</del>                          |     |

| A2.6.2.7.8    | <del>-</del>                          |     |

| A2.6.2.7.9    | 9 WAIT_RESTORE                        |     |

| A2.6.2.7.10 ERR                                                        | 447              |

|------------------------------------------------------------------------|------------------|

| A2.6.2.7.11 Individual Negotiation Functions                           | 447              |

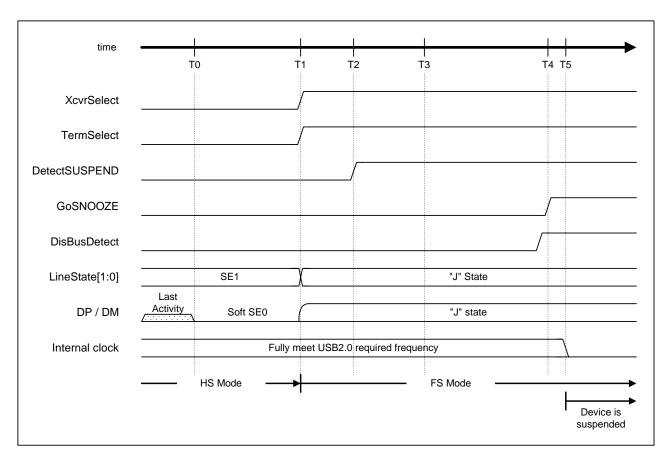

| A2.6.2.7.11.1 Suspend Detection (in HS Mode)                           | 447              |

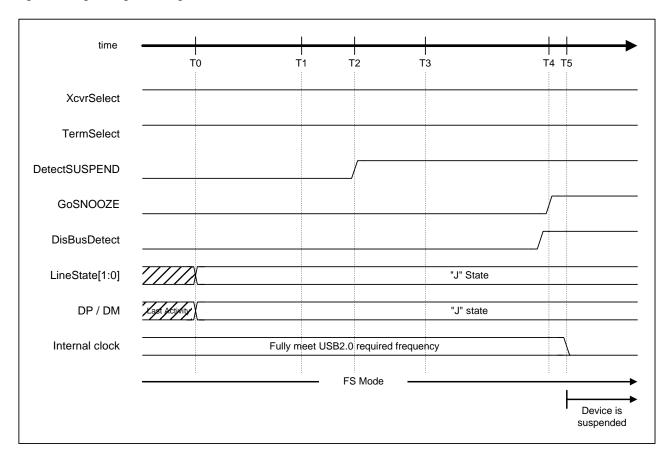

| A2.6.2.7.11.2 Suspend Detection (in FS Mode)                           | 449              |

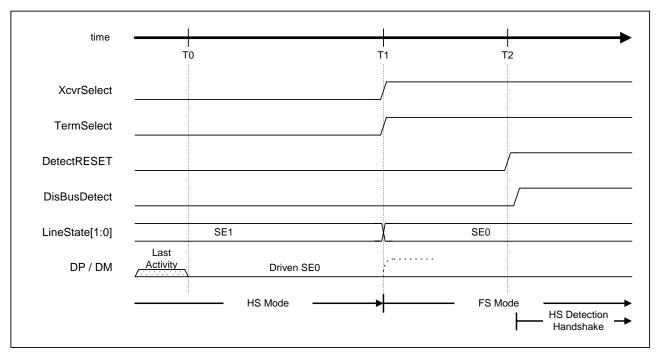

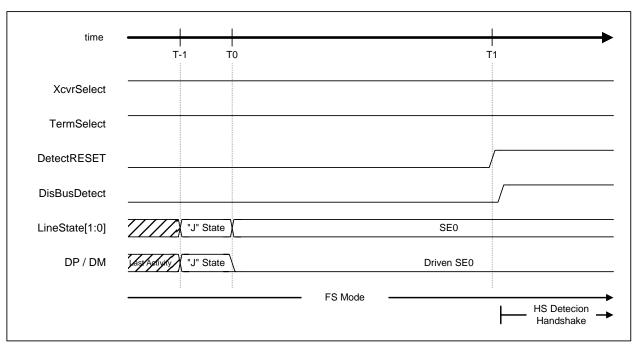

| A2.6.2.7.11.3 Reset Detection (in HS Mode)                             | 450              |

| A2.6.2.7.11.4 HS Detection Handshake                                   | 452              |

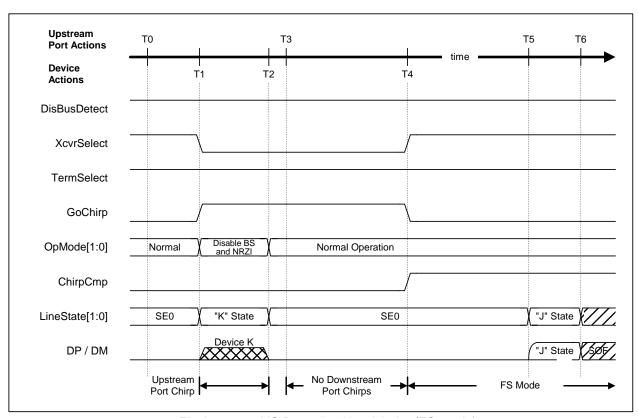

| A2.6.2.7.11.5 If connected to a Downstream Port supporting FS M        | Mode         452 |

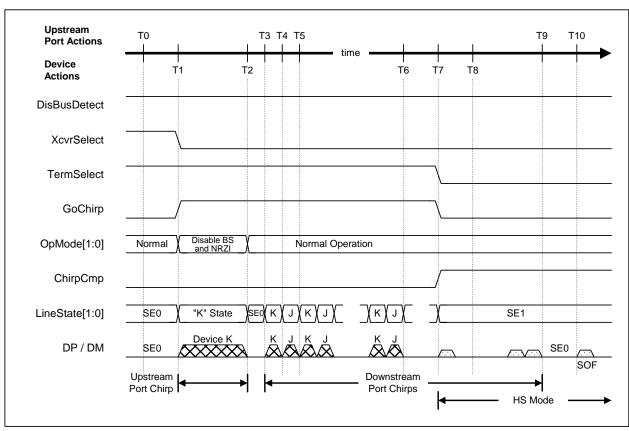

| A2.6.2.7.11.6 If connected to a Downstream Port supporting HS I        | Mode454          |

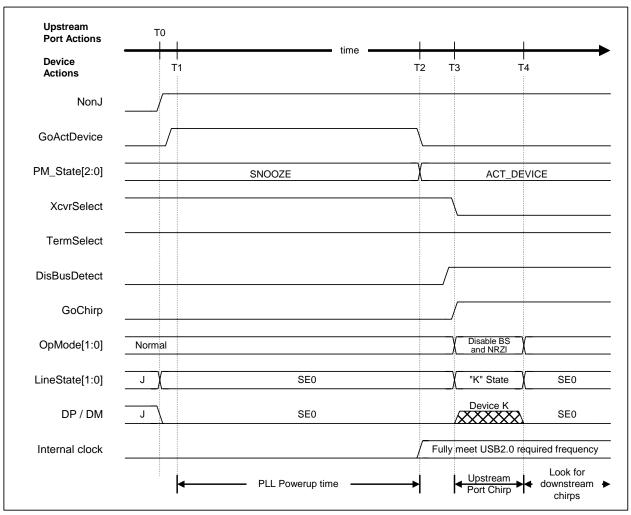

| A2.6.2.7.11.7 If Device is Reset during SNOOZE State                   | 456              |

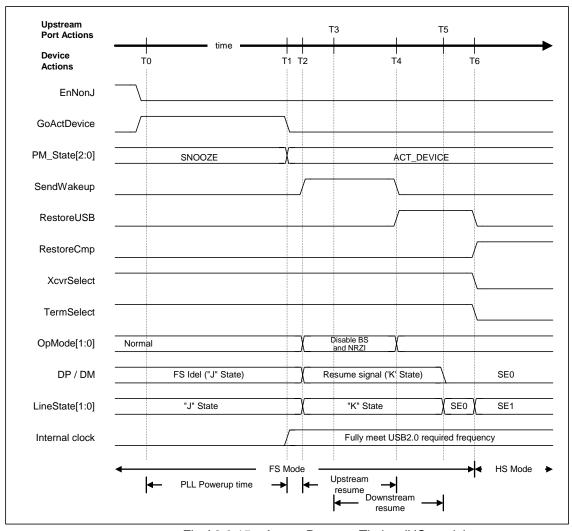

| A2.6.2.7.11.8 Issue of Resume Signal                                   | 457              |

| A2.6.2.7.11.9 Detection of Resume Signal                               |                  |

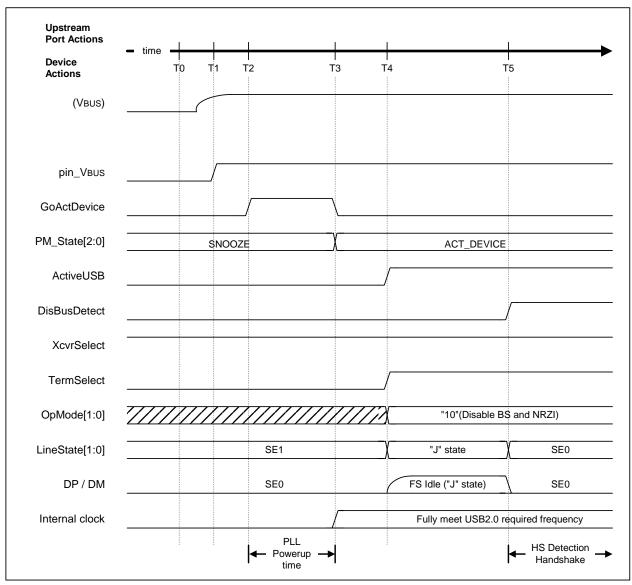

| A2.6.2.7.11.10 Cable Insertion                                         | 460              |

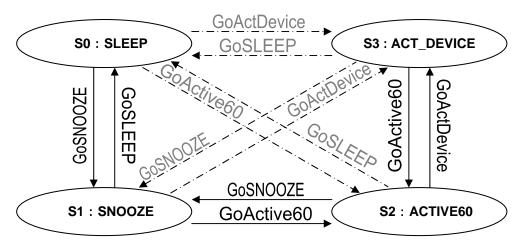

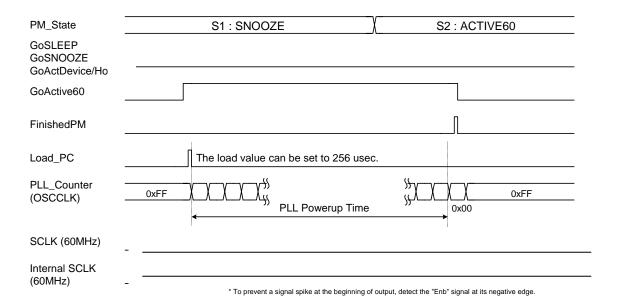

| A2.6.3 Power Management Function                                       | 462              |

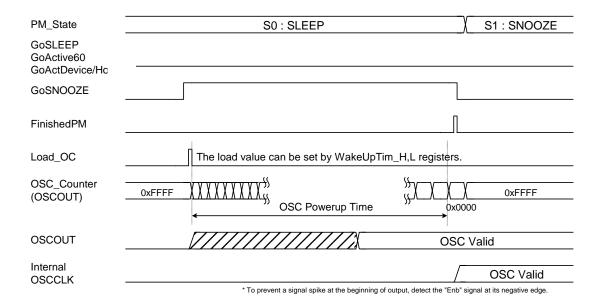

| A2.6.3.1 SLEEP State                                                   | 463              |

| A2.6.3.2 SNOOZE State                                                  | 464              |

| A2.6.3.3 ACTIVE60 State                                                | 464              |

| A2.6.3.4 ACT_DEVICE State                                              | 464              |

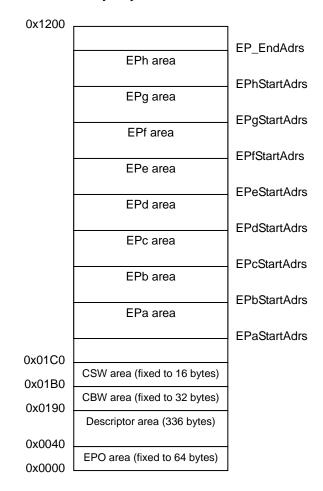

| A2.6.4 FIFO Memory Management                                          | 465              |

| A2.6.4.1 FIFO Memory Map                                               |                  |

| A2.6.4.2 Using the Descriptor Area                                     |                  |

| A2.6.4.2.1 Writing Data in Descriptor Area                             |                  |

| A2.6.4.2.2 Executing the Data Stage (IN-Direction) in Descriptor Area. | 466              |

| A2.6.4.3 Using the CBW Area                                            | 466              |

| A2.6.4.3.1 Receiving Data in CBW Area                                  | 467              |

| A2.6.4.3.2 Reading Data from CBW Area                                  | 467              |

| A2.6.4.4 Using the CSW Area                                            | 467              |

| A2.6.4.4.1 Sending Data from CSW Area                                  | 467              |

| A2.6.4.4.2 Writing Data in CSW Area                                    | 467              |

| A2.6.4.5 Accessing to FIFO Memory                                      | 467              |

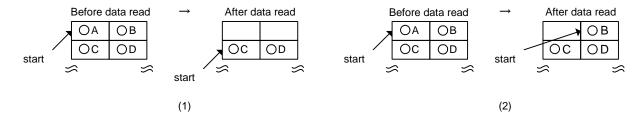

| A2.6.4.5.1 Accessing to FIFO Memory (RAM_Rd)                           |                  |

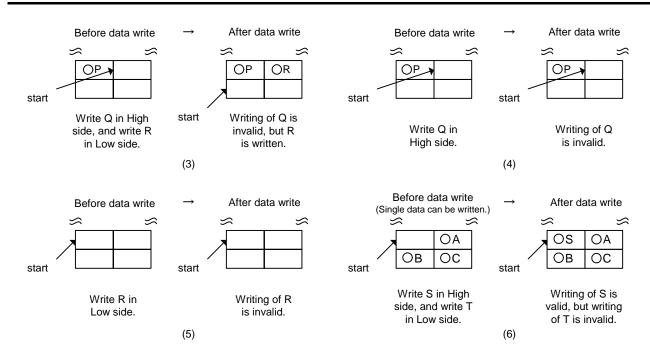

| A2.6.4.5.2 Accessing to FIFO Memory (RAM_WrDoor)                       |                  |

| A2.6.4.5.3 Register Access to FIFO Memory                              |                  |

| A2.6.4.5.3.1 Write Access to FIFO Memory                               |                  |

| A2.6.4.5.3.2 Read Access to FIFO Memory                                |                  |

| A2.6.4.5.3.3 Rounding of FIFO Access                                   |                  |

| A2.6.4.5.4 DMA Access to FIFO Memory                                   |                  |

| A2.6.4.5.5 Restricted Access to FIFO Memory                            | 471              |

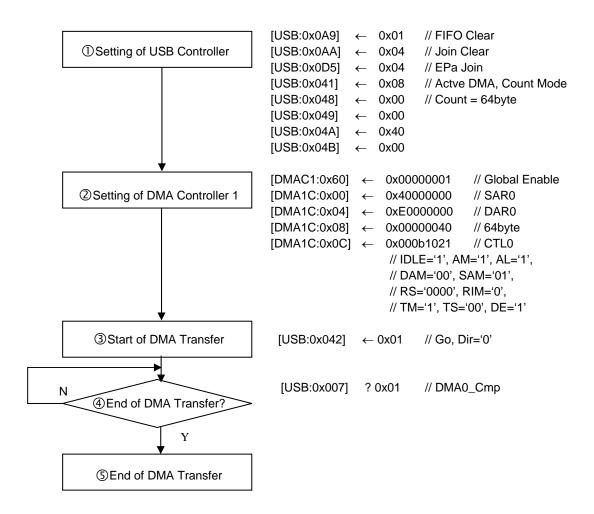

| A2.6.5 DMA Transfer                                                    |                  |

| A2.6.5.1 Description                                                   |                  |

| A2.6.5.2 Basic Functions                                               | 472              |

| A2.6.5.2.1 Count Mode                                                  |                  |

| A2.6.5.2.2 Free-Running Mode                                           |                  |

| A2.6.5.3 Operation Procedure                                           |                  |

| A2.6.5.4 Forced Termination                                            | 171              |

# <List of Figures>

| Fig. A2.3.1  | S2S65A00 USB Controller Block Diagram                      | 366 |

|--------------|------------------------------------------------------------|-----|

| Fig. A2.4.2  | USB External Terminal                                      | 367 |

| Fig. A2.6.1  | SETUP Transaction                                          | 427 |

| Fig. A2.6.2  | OUT Transaction                                            | 428 |

| Fig. A2.6.3  | IN Transaction                                             | 429 |

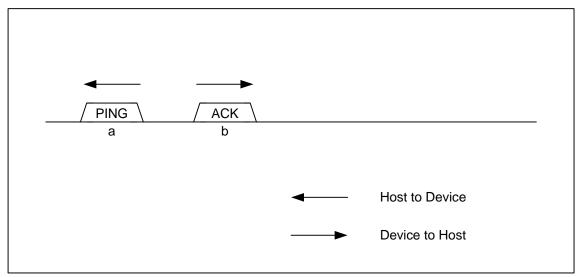

| Fig. A2.6.4  | PING Transaction                                           | 429 |

| Fig. A2.6.5  | Control transfer if the data stage is in the OUT direction | 430 |

| Fig. A2.6.6  | Control transfer if the data stage is in IN direction      |     |

| Fig. A2.6.7  | Auto-Negotiator                                            |     |

| Fig. A2.6.8  | Suspend Timing (HS mode)                                   |     |

| Fig. A2.6.9  | Suspend Timing (FS mode)                                   |     |

| Fig. A2.6.10 |                                                            |     |

| Fig. A2.6.11 | Reset Timing (FS mode)                                     |     |

| Fig. A2.6.12 | HS Detection Handshake (FS mode)                           |     |

| Fig. A2.6.13 | HS Detection Handshake Timing (HS mode)                    |     |

| Fig. A2.6.14 | HS Detection Handshake Timing from Suspend                 |     |

| Fig. A2.6.15 | Assert Resume Timing (HS mode)                             |     |

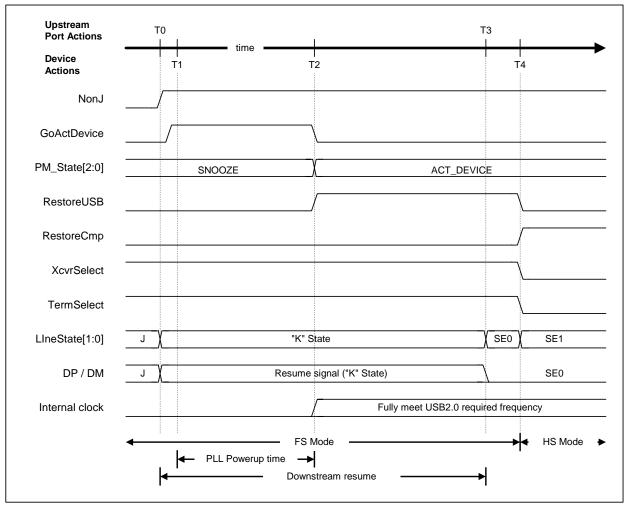

| Fig. A2.6.16 | Detect Resume Timing (HS mode)                             |     |

| Fig. A2.6.17 |                                                            |     |

| Fig. A2.6.18 | Power Management                                           |     |

| Fig. A2.6.19 |                                                            |     |

| Fig. A2.6.20 | Transition from SNOOZE State (GoActive60)                  |     |

| Fig. A2.6.21 | FIFO Memory Map (Example)                                  |     |

| Fig. A2.6.22 | FIFO Write Process (Normal operation)                      |     |

| Fig. A2.6.23 | FIFO Write Process (Operation requiring caution)           |     |

| Fig. A2.6.24 | FIFO Read Process (Normal operation)                       |     |

| Fig. A2.6.25 |                                                            |     |

| Fig. A2.6.26 |                                                            |     |

|              | <list of="" tables=""></list>                              |     |

| Tbl. A2.5.1  | USB Register List (1/4)                                    | 368 |

| Tbl. A2.5.2  | USB Register List (2/4)                                    | 369 |

| Tbl. A2.5.3  | USB Register List (3/4)                                    | 370 |

| Tbl. A2.5.4  | USB Register List (4/4)                                    | 371 |

| Tbl. A2.6.1  | Basic setting items of the end point EP0                   | 423 |

| Tbl. A2.6.2  | Basic setting items of the universal point                 | 424 |

| Tbl. A2.6.3  | Control items and statuses of the end point EP0            | 425 |

| Tbl. A2.6.4  | Control items and statuses of the universal point          |     |

| Tbl. A2.6.5  | Suspend Timing Values (HS mode)                            | 438 |

| Tbl. A2.6.6  | Suspend Timing Values (FS mode)                            | 439 |

| Tbl. A2.6.7  | Reset Timing Values (HS mode)                              | 440 |

| Tbl. A2.6.8  | Reset Timing Values (FS mode)                              |     |

| Tbl. A2.6.9  | HS Detection Handshake Timing Values (FS mode)             |     |

| Tbl. A2.6.10 | HS Detection Handshake Timing Values (HS mode)             |     |

| Tbl. A2.6.11 | HS Detection Handshake Timing Values from Suspend          |     |

| Tbl. A2.6.12 | Assert Resume Timing Values (HS mode)                      | 448 |

| Tbl. A2.6.13 | Detect Resume Timing Values (HS mode)                      |     |

| Tbl. A2.6.14 | Device Attach Timing Values                                | 451 |

|              |                                                            |     |

#### 1. DESCRIPTION

This product, S2S65A00, is an IC specifically for a drive recorder. It has camera interfaces and JPEG encoder functions, as well as embedded CF, SD memory, USB 2.0 device (High-Speed supported) interfaces, and 8-ch ADC. A drive recorder can easily be configured by connecting S2S65A00 with camera modules, SDRAM, an external storage (CF or SD memory card), and Flash ROM containing firmware. For example, JPEG data generated by the embedded encoder may constantly be accumulated into the SDRAM. In response to an external trigger, such as detection of a rapid change in speed by the acceleration sensor IC, the accumulated image data can be transferred to and saved in an external storage (CF or SD memory card). In addition, S2S65A00 is equipped with GPIO and I<sup>2</sup>C bus, which enable you to set cameras and control external devices.

#### 1.1 Features

- One-chip solution, which can reduce system cost.

- Provides JPEG encoding by using 30 fps @VGA hardware (ISO 10918 compliant).

- Up to two camera modules can be connected.

- Each camera module has two hardware JPEG encoders.

- Provides moving-object detection function to support motion detection.

- Supports I<sup>2</sup>S for voice data.

- Has a CompactFlash interface for a CF memory card or a wireless LAN interface (802.11b/g).

- An SD memory interface for SD memory card connection.

- ARM720T 50MHz operation.

- USB 2.0 device (High-Speed) function support, which enables connection to a PC.

- Supports 8-ch ADC for connection with various analog sensors.

- Contains event counter timers.

- Memory bus: 2 ports (6bit-Bus: FROM/SRAM, 16/32bit-Bus: SDRAM).

#### 1.2 Built-In Functions

#### CPU:

- 32-bit RISC ARM720T (maximum of 56MHz).

- 32-bit long command codes and 16-bit long command codes called Efficient Thumb Code can be used by switching them.

- 32-bit general purpose register (×31).

- A multiplier is included in the CPU.

#### RAM:

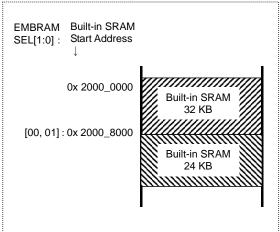

• 56 KB Built-in RAM for CPU/JPEG Work (CPU Work: 32KB Max.).

#### **Standby Function**

- · A HALT function to stop the CPU clock when any CPU operation is not required.

- An I/O clock stop function to stop each clock of the main I/O blocks.

#### Camera Input/JPEG Encoder:

- 8-bit parallel interface × 2 ports

- 2 camera modules can be connected.

- Up to 640×480 resolution (VGA, QVGA, CIF, QCIF).

- Hardware JPEG encoder × 2

- Throughput greater than 30 fps @VGA (when 1 camera module connected).

- YUV4-2-2 progressive (both ports)

- Pixel clock frequency for inputting camera data is less than 2/3 of CPU clock frequency.

#### 1. DESCRIPTION

#### JPEG:

- · Hardware JPEG encoder

- · Resize function (screen can be cut off)

- · Dedicated line buffer

- Variable volume FIFO built in the JPEG encoder output.

- · An enhanced DMA is included in the network.

#### **USB2.0 Device:**

- Supports HS (480Mbps) and FS (12Mbps) transfer.

- Has built-in FS/HS Termination function (external circuit not required).

- VBUS 5V Interface (external protection circuit required).

- · Supports control bulk and interrupt transfer.

- Supports 8 end points shared by control (End Point 0) and bulk/interrupt

- Has a 16-bit or 8-bit width general purpose CPU interface.

- · Littler Endian is supported.

- Addition to and deletion form the register table is performed based on the HS-Device section of S1R72V05.

- 12MHz or 24MHz crystal transducer input is supported as clock input for USB.

- · As internal clock use, the following frequencies are available based on the clock for the input USB.

- · Clock for input USB: 12MHz or 24MHz.

- Clock for internal USB: 60MHz (via PLL for built-in USB).

#### **Memory Controller:**

- · AHB bus interface memory controller.

- Supports up to four SRAM timing devices.

- · Supports up to eight SDRAMs.

- · Refresh interval of SDRAM auto-refresh can be adjusted to the device.

- · SDRAM burst refresh support.

- · Supports SDRAM self-refresh.

#### **CF Card Interface:**

- Complies with CF+ Specification Rev.1.4.

- · Can be used as the interface of wireless LAN, PHS card, etc.

- Supports the True IDE mode.

#### **SD Memory Interface:**

- Complies with SD Memory Card Physical Layer Spec. ver.1.0.

- 1-bit/4-bit interface support

#### **Interrupt Controller:**

• Supports 32 IRQs and 2 FIQs.

#### **Serial interface:**

- UART: Compatible with 16550 software × 3 channel

- SPI: Clock synchronous type × 1 channel

- I<sup>2</sup>C master interface (camera interface and multipurpose use)

- I<sup>2</sup>S interface (voice/audio data supported, I<sup>2</sup>S compliant)

#### Timer A:

- 16-bit timer × 3-channel timer

- · Re-load/cyclic or one shot operation mode

- Supports toggle outputs resulted from underflow output or port outputs.

#### **Timer B: for Event Counter**

- · 16-bit upcount timer

- Four COMMON registers are implemented, each of which can be configured as an output register or an input capture register.

#### **Watchdog Timer**

· Interrupt output or re-settable watchdog timer.

#### **Real Time Clock**

- · Supports year, month, day, hour, minute and second.

- The internal timer tap from 1/128 to 1/2 can be used as the interrupt source as well.

- Supports alarm function and interrupt.

#### **GPIO:**

- General-purpose I/O port (up to 82)

- Programmable setting of directions is possible for all ports.

- Partly selects other I/O functions.

#### **AD Converter:**

- 8-channel analog signal inputs.

- 10-bits resolution AD converter.

- AD conversion time is 20µsec or less.

#### **Power Supply:**

- 3.3V (I/O power supply)

- 3.3V (USB)

- 1.8V (core power supply)

- 2.4 to 3.6V (Camera 1/2 I/O power supply)

- 2.7 to 3.6V (SDRAM I/O power supply)

- 3.3V (A/D power supply)

- 1.8V (USB/PLL/RTC)

#### Package:

• PFBGA 280 Pin (PFBGA16UX280)  $16 \times 16 \times 1.2$  mm, 0.8 mm ball pitch

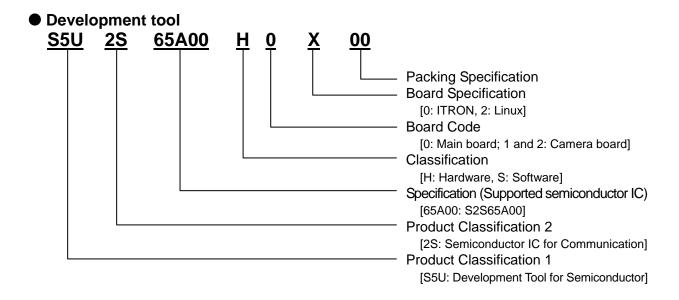

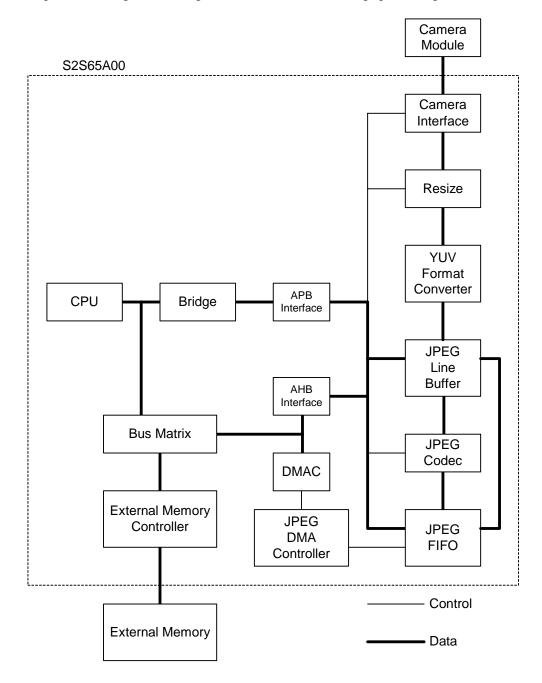

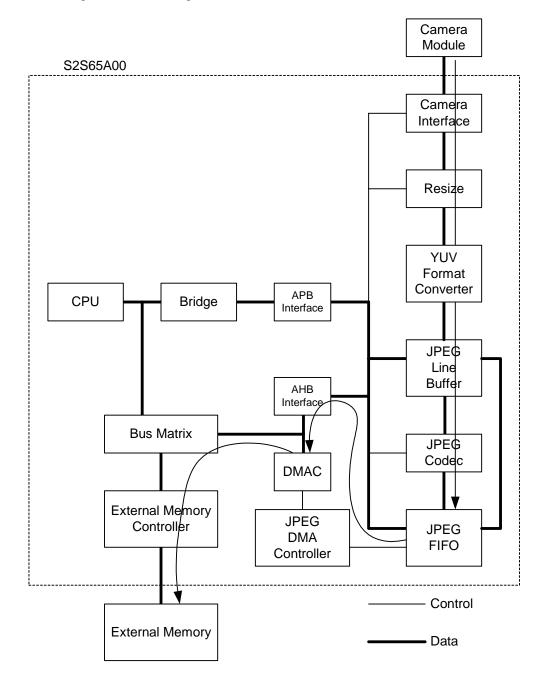

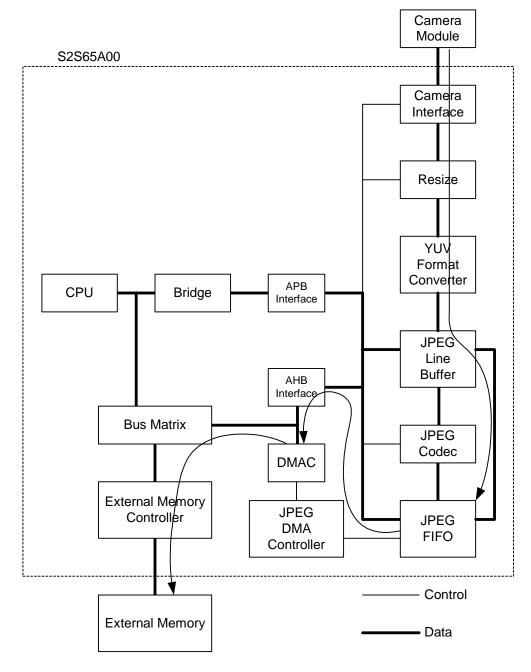

#### 2. BLOCK DIAGRAM

Fig.2.1 S2S65A00 Internal Block Diagram

Note (\*1): Internal SRAM is shared with Line Buffer of JPG[2:1]. When JPG[2:1] is used, CPU-Work cannot be used.

#### 3. PIN

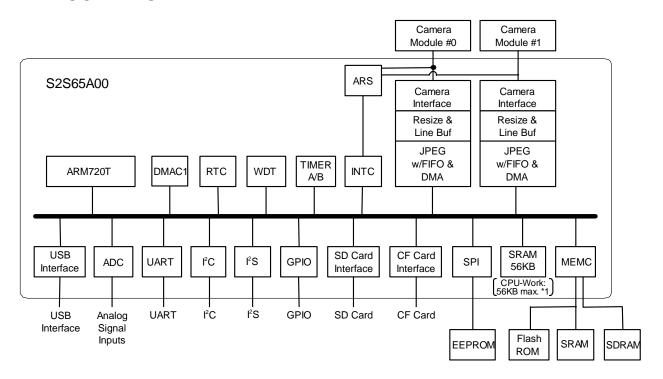

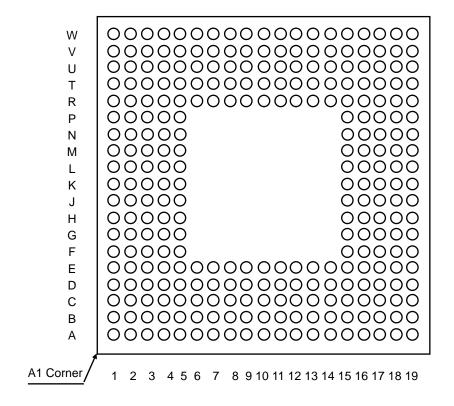

### 3.1 Pin Assignment

Fig.3.1 Pin Assignment (Bottom View)

| Pin No. | Pin Name  | Pin No. | Pin Name | Pin No. | Pin Name  | Pin No. | Pin Name |

|---------|-----------|---------|----------|---------|-----------|---------|----------|

| A1      | NC        | D14     | HVDD     | K15     | LVDD      | T7      | CM2DATA2 |

| A2      | CM1CLKIN  | D15     | GPIOA2   | K16     | CFDEN#    | T8      | GPIOD2   |

| A3      | CM1CLKOUT | D16     | GPIOA4   | K17     | CFDDIR    | Т9      | GPIOD1   |

| A4      | C1VDD     | D17     | GPIOA0   | K18     | LVDD      | T10     | MA17     |

| A5      | SYS_OSCO  | D18     | LVDD     | K19     | CFSTSCHG# | T11     | MA15     |

| A6      | SYS_OSCI  | D19     | GPIOA1   | L1      | Vss       | T12     | MA11     |

| A7      | RTCVDD    | E1      | LVDD     | L2      | GPIOJ6    | T13     | MA7      |

| A8      | PLLVSS    | E2      | Vss      | L3      | GPIOJ3    | T14     | Vss      |

| A9      | SYSVCP    | E3      | SDA6     | L4      | GPIOJ5    | T15     | MA2      |

| A10     | SYSCLKI   | E4      | VSS      | L5      | LVDD      | T16     | MCS1#    |

| A11     | LVDD      | E5      | SDA0     | L15     | HVDD      | T17     | MD13     |

| A12     | Vss       | E6      | GPIOK5   | L16     | CFWAIT#   | T18     | MD12     |

| A13     | UXVDD     | E7      | GPIOK4   | L17     | CFRST     | T19     | MD10     |

| A14     | DP        | E8      | Vss      | L18     | Vss       | U1      | SDD0     |

| A15     | DM        | E9      | CM1DATA0 | L19     | CFIRQ     | U2      | SDDQM1#  |

| A16     | UVDD3     | E10     | TESTEN1  | M1      | GPIOJ0    | U3      | CM2HREF  |

| A17     | R1        | E11     | Vss      | M2      | GPIOJ2    | U4      | Vss      |

| A18     | UPVDD     | E12     | LVDD     | M3      | GPIOJ1    | U5      | CM2DATA4 |

| A19     | NC        | E13     | TDI      | M4      | SDD15     | U6      | AVSS     |

| B1      | SDA13     | E14     | GPIOB3   | M5      | Vss       | U7      | CM2DATA5 |

| B2      | SDA14     | E15     | GPIOB1   | M15     | CFCE2#    | U8      | CM2DATA7 |

| В3      | CM1HREF   | E16     | GPIOB0   | M16     | MD3       | U9      | GPIOD3   |

| Pin No. | Pin Name   | Pin No. | Pin Name | Pin No. | Pin Name | Pin No. | Pin Name  |

|---------|------------|---------|----------|---------|----------|---------|-----------|

| B4      | Vss        | E17     | GPIOA3   | M17     | CFCE1#   | U10     | GPIOD0    |

| B5      | CM1DATA3   | E18     | HVDD     | M18     | CFIORD#  | U11     | MA16      |

| В6      | CM1DATA6   | E19     | GPIOA5   | M19     | CFIOWR#  | U12     | MA12      |

| B7      | Vss        | F1      | SDA1     | N1      | SDD11    | U13     | MA8       |

| B8      | BUP#       | F2      | SDVDD    | N2      | Vss      | U14     | MA4       |

| В9      | PLLVDD     | F3      | SDA5     | N3      | SDD13    | U15     | MA1       |

| B10     | SYSCKSEL   | F4      | SDA2     | N4      | SDD14    | U16     | Vss       |

| B11     | TRST#      | F5      | GPIOK1   | N5      | SDD12    | U17     | MBEL#     |

| B12     | TESTCK     | F15     | LVDD     | N15     | MD5      | U18     | MD14      |

| B13     | XVSS       | F16     | GPIOB2   | N16     | MD1      | U19     | MD15      |

| B14     | UVDD3      | F17     | GPIOA6   | N17     | Vss      | V1      | GPIOD6    |

| B15     | UVSS       | F18     | LVDD     | N18     | MD2      | V2      | Vss       |

| B16     | Vss        | F19     | GPIOA7   | N19     | MD0      | V3      | CM2VREF   |

| B17     | UVSS       | G1      | GPIOK7   | P1      | SDVDD    | V4      | CM2DATA0  |

| B18     | PVSS       | G2      | GPIOK6   | P2      | SDD10    | V5      | AVDD      |

| B19     | USBCK_OSCO | G3      | GPIOK3   | P3      | SDD9     | V6      | ADIN7     |

| C1      | SDA11      | G4      | GPIOK0   | P4      | SDD8     | V7      | ADIN5     |

| C2      | Vss        | G5      | Vss      | P5      | Vss      | V8      | ADIN3     |

| C3      | SDVDD      | G15     | GPIOC1   | P15     | MD9      | V9      | ADIN1     |

| C4      | SDA12      | G16     | HVDD     | P16     | MD8      | V10     | AVSS      |

| C5      | CM1VREF    | G17     | GPIOB5   | P17     | MD6      | V11     | MA19      |

| C6      | CM1DATA5   | G18     | Vss      | P18     | MD4      | V12     | MA14      |

| C7      | CM1DATA7   | G19     | GPIOB4   | P19     | LVDD     | V13     | Vss       |

| C8      | Vss        | H1      | LVDD     | R1      | SDD6     | V14     | MA3       |

| C9      | HVDD       | H2      | Vss      | R2      | SDD5     | V15     | GPIOD5    |

| C10     | Vss        | Н3      | GPIOK2   | R3      | SDD4     | V16     | MCS0#     |

| C11     | TESTEN0    | H4      | SDWE#    | R4      | SDD7     | V17     | MWE#      |

| C12     | TDO        | H5      | SDCAS#   | R5      | SDD3     | V18     | LVDD      |

| C13     | Vss        | H15     | GPIOC6   | R6      | SDD2     | V19     | Vss       |

| C14     | VBUS       | H16     | GPIOC0   | R7      | CM2DATA1 | W1      | NC        |

| C15     | Vss        | H17     | GPIOB6   | R8      | CM2DATA6 | W2      | CM2CLKIN  |

| C16     | HVDD       | H18     | HVDD     | R9      | Vss      | W3      | CM2CLKOUT |

| C17     | Vss        | H19     | GPIOB7   | R10     | HVDD     | W4      | C2VDD     |

| C18     | Vss        | J1      | SDCS1#   | R11     | MA13     | W5      | AVDD      |

| C19     | USBCK_OSCI | J2      | SDCS0#   | R12     | MA9      | W6      | ADIN6     |

| D1      | SDA8       | J3      | SDRAS#   | R13     | MA6      | W7      | ADIN4     |

| D2      | SDA9       | J4      | GPIOJ7   | R14     | MA5      | W8      | ADIN2     |

| D3      | SDA7       | J5      | GPIOJ4   | R15     | HVDD     | W9      | ADIN0     |

| D4      | SDA10      | J15     | GPIOC7   | R16     | GPIOD4   | W10     | AVDD      |

| D5      | SDA4       | J16     | GPIOC5   | R17     | MD11     | W11     | MA18      |

| D6      | SDA3       | J17     | GPIOC4   | R18     | Vss      | W12     | HVDD      |

| D7      | CM1DATA1   | J18     | GPIOC3   | R19     | MD7      | W13     | MA10      |

| D8      | CM1DATA2   | J19     | GPIOC2   | T1      | Vss      | W14     | LVDD      |

| D9      | CM1DATA4   | K1      | SDCLK    | T2      | LVDD     | W15     | HVDD      |

| D10     | LVDD       | K2      | SDCLKEN  | T3      | SDD1     | W16     | MA0       |

| D11     | TCK        | K3      | SDVDD    | T4      | GPIOD7   | W17     | MOE#      |

| D12     | TMS        | K4      | SDVDD    | T5      | SDDQM0#  | W18     | MBEH#     |

| D13     | RESET#     | K5      | Vss      | T6      | CM2DATA3 | W19     | NC        |

**Note:** # at the right end of pin name indicates to be an active low signal.

## 3.2 Pin Description

# : # at the right end of pin name indicates to be an active low signal.

I : Input pin

O : Output pin

IO : Bi-directional pin

P : Power supply

Table 3.1 Cell Type Description

| Call Type | Description                                                                                   | Example of Pin being Used             |                 |  |  |

|-----------|-----------------------------------------------------------------------------------------------|---------------------------------------|-----------------|--|--|

| Cell Type | Description                                                                                   | Pin Name                              | Power Supply    |  |  |

| ILS       | Low Voltage LVCMOS Schmitt input                                                              | BUP#                                  | RTCVDD          |  |  |

| ICD1      | LVCMOS input with pull-down resistor                                                          | TESTEN[1:0],TESTCK                    | HVDD            |  |  |

|           | (50kΩ@3.3V)                                                                                   |                                       |                 |  |  |

| ICU1      | LVCMOS input with pull-up resistor (50kΩ@3.3V)                                                | TMS, TDI                              | HVDD            |  |  |

| ICSU1     | LVCMOS Schmitt input with pull-up resistor (50kΩ@3.3V)                                        | TRST#,TCK,RESET#                      | HVDD            |  |  |

| ICSD1     | LVCMOS Schmitt input with pull-down resistor (50kΩ@3.3V)                                      | SYSCKSEL                              | HVDD            |  |  |

| ILTR      | Low Voltage Transparent Input                                                                 | SYS_OSCI                              | RTCVDD          |  |  |

|           |                                                                                               | USBCK_OSCI                            | UPVDD           |  |  |

|           |                                                                                               | R1                                    | UVDD3           |  |  |

| IHTR      | High Voltage Transparent Input                                                                | ADIN[7:0]                             | ADVDD           |  |  |

| OLTR      | Low Voltage Transpatent Output                                                                | SYS_OSCO,SYSVCP                       | PLLVDD          |  |  |

|           |                                                                                               | USBCK_OSCO                            | UPVDD           |  |  |

| BLNC4U1   | Low noise LVCMOS IO buffer with pull-up resistor ( $50k\Omega@3.3V$ ) ( $\pm 4mA$ )           | CF I/F                                | HVDD            |  |  |

| BLNC4D2   | Low noise LVCMOS IO buffer with                                                               | MD [15:0]                             | HVDD            |  |  |

|           | pull-down resistor (100k $\Omega$ @3.3V) ( $\pm$ 4mA)                                         | SDD[15:0],GPIOJ,GPIOK                 | SDVDD           |  |  |

| BLNS4     | Low noise LVCMOS Schmitt IO buffer (±4mA)                                                     | GPIOA, GPIOB, GPIOC,GPIOD,<br>SYSCLKI | HVDD            |  |  |

| BLNS4D1   | Low noise LVCMOS Schmitt IO buffer with pull-down resistor ( $50k\Omega@3.3V$ ) ( $\pm 4mA$ ) | Camera I/F                            | C1VDD,<br>C2VDD |  |  |

| OLN4      | Low noise output buffer (±4mA)                                                                | SRAM Device I/F<br>(excluding MD)     | HVDD            |  |  |

|           |                                                                                               | SDRAM I/F<br>(excluding SDD[15:0])    | SDVDD           |  |  |

| OTLN4     | Low noise Tri-state output buffer (±4mA)                                                      | TDO "                                 | HVDD            |  |  |

| USBDM     | USB DM buffer                                                                                 | DM                                    | UVDD3           |  |  |

| USBDP     | USB DP buffer                                                                                 | DP                                    | UVDD3           |  |  |

| USBVBUS   | USB VBUS output buffer                                                                        | VBUS                                  | UVDD3           |  |  |

Table 3.2 Pin Description

| Pin Name     | Туре  | Cell<br>Type                                                                                                                                                                                                                                                                                                | Pin No.                                                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (MA [23:20]) | (I/O) | (BLNS4)                                                                                                                                                                                                                                                                                                     |                                                                                             | For information on these pins, see the description of <b>GPIOD</b> [3:0].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| MA [19:12]   | 0     | OLN4                                                                                                                                                                                                                                                                                                        | V11,W11,<br>T10,U11,<br>T11,V12,<br>R11,U12                                                 | Address Output Signal for Flash-ROM/SRAM [19:12]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MA 11        | 0     | This pin has the following functions:  • MA11: Address output signal for Flash-ROM/SRAM [11] (Pin function right after reset)  • CFREG# Output Signal When the compact flash (CF) interface is in operation, this signal functions as the REG signal selecting attribute of the CF interface and I/O space. |                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MA [10:0]    | 0     | OLN4                                                                                                                                                                                                                                                                                                        | W13,R12,<br>U13,T13,<br>R13,R14,<br>U14,V14,<br>T15,U15,<br>W16                             | These pins have the following functions:  • MA [10:0]: Address output signal for Flash-ROM/SRAM [10:0] (Pin function right after reset)  • CFADDR [10:0] Output signal  When the CF interface is in operation, this signal becomes the CF interface address signal [10:0].                                                                                                                                                                                                                                                                                                      |

| MBEL#        | I/O   | OLN4                                                                                                                                                                                                                                                                                                        | U17                                                                                         | Data bus low byte enable output for Flash-ROM/SRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| MBEH#        | I/O   | OLN4                                                                                                                                                                                                                                                                                                        | W18                                                                                         | Data bus high byte enable output for Flash-ROM/SRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MD [15:0]    | I/O   | BLNC4D2                                                                                                                                                                                                                                                                                                     | U19,U18,<br>T17,T18,<br>R17,T19,<br>P15,P16,<br>R19,P17,<br>N15,P18,<br>M16,N18,<br>N16,N19 | <ul> <li>These pins have the following functions:</li> <li>16-bit data bus for Flash-ROM/SRAM (Pin function right after reset)</li> <li>When the CF interface is in operation, this pin becomes good for 16-bit data.</li> <li>MODESEL[15:0]</li> <li>Sampled to determine the internal operation mode, at power-on resetting (RESET# transition from Low to High). For details, see section "4.1 System Configuration".</li> <li>Here, to determine the operation mode, a pull-up resistance may be required externally. (Resistance in the range from 4.7 to 10kΩ)</li> </ul> |

| MCS [3:2]#   | 0     | (BLNS4)                                                                                                                                                                                                                                                                                                     | V15,R16                                                                                     | For information on these pins, see the description of <b>GPIOD</b> [5:4].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| MCS [1:0]#   | 0     | OLN4                                                                                                                                                                                                                                                                                                        | T16,V16                                                                                     | Chip select signal for Flash-ROM/SRAM [1:0] (Active low signal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MOE#         | 0     | OLN4                                                                                                                                                                                                                                                                                                        | W17                                                                                         | This pin has the following functions: (Active low signal)  • MOE#: Strobe signal for Flash-ROM/SRAM (Pin function right after reset)  • CFOE# output signal  When the CF interface is in operation, this signal becomes the output enable signal of CF interface memory and attribute spaces.                                                                                                                                                                                                                                                                                   |

| Pin Name     | Туре  | Cell<br>Type | Pin No.                                                                     | Description                                                                                                                                                                                                                                                                                                                                                                |

|--------------|-------|--------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MWE#         | 0     | OLN4         | V17                                                                         | This pin has the following functions: (Active low signal)  • MWE#: Write enable signal for Flash-ROM/SRAM (for static memory) (Pin function right after reset)  • CFWE# output signal  When the CF interface is in operation, this signal becomes the write enable signal of CF interface memory and attribute spaces.                                                     |

| SDA [14:0]   | 0     | OLN4         | B2,B1,<br>C4,C1,<br>D4,D2,<br>D1,D3,<br>E3,F3,<br>D5,D6,<br>F4,F1,          | Address output for SDRAM [14:0]                                                                                                                                                                                                                                                                                                                                            |

| SDD[31:16]   | (I/O) | (BLNC4D2)    |                                                                             | For information on these pins, see the descriptions of GPIOK [7:0] and GPIOJ [7:0].                                                                                                                                                                                                                                                                                        |

| SDD [15:0]   | I/O   | BLNC4D2      | M4,N4,<br>N3,N5,<br>N1,P2,<br>P3,P4,<br>R4,R1,<br>R2,R3,<br>R5,R6,<br>T3,U1 | Data I/O for SDRAM [15:0]                                                                                                                                                                                                                                                                                                                                                  |

| SDWE#        | 0     | OLN4         | H4                                                                          | Write enable signal for SDRAM                                                                                                                                                                                                                                                                                                                                              |

| SDCLK        | 0     | OLN4         | K1                                                                          | Outputting clock for SDRAM  The same frequency as internal operation frequency (CPUCLK) is output.                                                                                                                                                                                                                                                                         |

| SDCLKEN      | 0     | OLN4         | K2                                                                          | Clock enable signal for SDRAM                                                                                                                                                                                                                                                                                                                                              |

| SDRAS#       | 0     | OLN4         | J3                                                                          | RAS signal for SDRAM (Active low signal)                                                                                                                                                                                                                                                                                                                                   |