## **S1D13705** Embedded Memory LCD Controller

# Programming Notes and Examples

Document Number: X27A-G-002-03.1

|   | _ |    | _      |   |

|---|---|----|--------|---|

| N | റ | TΙ | $\sim$ | ᆮ |

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. When exporting the products or technology described in this material, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You are requested not to use, to resell, to export and/or to otherwise dispose of the products (and any technical information furnished, if any) for the development and/or manufacture of weapon of mass destruction or for other military purposes.

All brands or product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

©SEIKO EPSON CORPORATION 2001-2018. All rights reserved.

## **Table of Contents**

| 1 | Introduction                                |

|---|---------------------------------------------|

| 2 | Initialization                              |

|   | 2.1 Display Buffer Location                 |

|   | 2.2 Register Values                         |

|   | 2.3 Frame Rate Calculation                  |

| 3 | Memory Models                               |

|   | 3.1 1 Bit-Per-Pixel (2 Colors/Gray Shades)  |

|   | 3.2 2 Bit-Per-Pixel (4 Colors/Gray Shades)  |

|   | 3.3 4 Bit-Per-Pixel (16 Colors/Gray Shades) |

|   | 3.4 Eight Bit-Per-Pixel (256 Colors)        |

| 4 | Look-Up Table (LUT)                         |

|   | 4.1 Look-Up Table Registers                 |

|   | 4.2 Look-Up Table Organization              |

|   | 4.2.1 Color Modes                           |

|   | 4.2.2 Gray Shade Modes                      |

| 5 | Advanced Techniques                         |

|   | 5.1 Virtual Display                         |

|   | 5.1.1 Registers                             |

|   | 5.1.2 Examples                              |

|   | 5.2 Panning and Scrolling                   |

|   | 5.2.1 Registers                             |

|   | 5.2.2 Examples                              |

|   | 5.3 Split Screen                            |

|   | 5.3.1 Registers                             |

|   | 5.3.2 Examples                              |

| 6 | LCD Power Sequencing and Power Save Modes   |

|   | 6.1 LCD Power Sequencing                    |

|   | 6.2 Registers                               |

|   | 6.3 LCD Enable/Disable                      |

| 7 | Hardware Rotation                           |

|   | 7.1 Introduction To Hardware Rotation       |

|   | 7.2 Default Portrait Mode                   |

|   | 7.3 Alternate Portrait Mode                 |

|   | 7.4 Registers                               |

|   | 7.5 Limitations                             |

|   | 7.6 Examples                                |

|   | <br>  |     | <br>.45  |

|---|-------|-----|----------|

|   | <br>  |     | <br>.46  |

|   |       |     | <br>.46  |

|   |       |     | <br>.46  |

|   |       |     | <br>.47  |

|   |       |     | <br>.47  |

|   | <br>  |     | <br>. 49 |

|   | <br>  |     | <br>. 50 |

|   | <br>  |     | <br>. 53 |

|   | <br>  |     | <br>. 56 |

|   | <br>  |     | <br>. 58 |

|   | <br>  |     | <br>. 59 |

|   | <br>  |     | <br>. 60 |

|   |       |     | <br>.62  |

|   | <br>  |     | <br>. 63 |

|   | <br>  |     | <br>. 63 |

|   | <br>  |     | <br>.64  |

|   |       |     |          |

|   |       |     |          |

|   |       |     |          |

|   |       |     |          |

| • | <br>• | • • | <br>.02  |

|   |       |     |          |

#### 1 Introduction

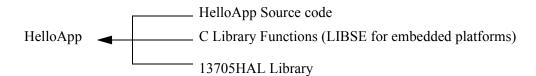

This guide demonstrates how to program the S1D13705 Embedded Memory Color LCD Controller. The guide presents the basic concepts of the LCD controller and provides methods to directly program the registers. It explains some of the advanced techniques used and the special features of the S1D13705.

The guide also introduces the Hardware Abstraction Layer (HAL), which is designed to make programming the S1D13705 as easy as possible. Future S1D1370x products will support the HAL allowing OEMs the ability to upgrade to future chips with relative ease.

This document is updated as appropriate. Please check for the latest revision of this document before beginning any development. The latest revision can be downloaded at vdc.epson.com.

We appreciate your comments on our documentation. Please contact us via email at vdc-documentation@ea.epson.com.

#### 2 Initialization

Prior to doing anything else with the S1D13705 the controller must be initialized. Initialization is the process of setting up the control registers to a known state in order to generate proper display signals.

#### 2.1 Display Buffer Location

Before we can perform the initialization we have to know where to find the S1D13705 display memory and control registers.

The S1D13705 contains 80 kilobytes of internal display memory. External support logic must be employed to decode the starting address for this display memory in CPU address space. On the S5U13705B00x PC platform evaluation boards the address is usually fixed at F00000h. Alternatively the address can be set to D0000h.

The control registers are located by adding 1FFE0h (128 Kb less 32 bytes) to the base memory address. Thus, on the typical PC platform, we access control register 0 at address F1FFE0h. Control register 5 would be located at address F1FFE5, etc.

#### 2.2 Register Values

This section describes the register settings and sequence of setting the registers. In addition to these setting the Look-Up Table must be programmed with appropriate colors. Look-Up Table setup is not covered here. See Section 4 on page 13 of this manual for Look-Up Table programming details.

The following initialization, presented in table form, shows the sequences and values to set the registers. The notes column comments the reason for the particular value being written.

This example writes to all the necessary registers. Initially, when the S1D13705 is powered up, all registers, unless noted otherwise in the specification, are set to zero. This example programs these registers to zero to establish a known state. In practice, it may be possible to write to only a subset of the registers.

The example initializes a S1D13705 to control a panel with the following specifications:

- 320x240 color single passive LCD panel at 70Hz.

- Color Format 2, 8-bit data interface.

- 8 bit-per-pixel (256 colors).

- 6 MHz input clock (CLKI).

Table 2-1: S1D13705 Initialization Sequence

| Register | Value (hex)    | Notes                                                                    | See Also                   |  |

|----------|----------------|--------------------------------------------------------------------------|----------------------------|--|

| [01]     | 0010 0011 (23) | Select a passive, Single, Color panel with an 8-bit data width           |                            |  |

| [02]     | 1100 0000 (C0) | Select 8-bit per pixel color depth                                       |                            |  |

| [03]     | 0000 0011 (03) | Select normal power operation                                            |                            |  |

| [04]     | 0010 0111 (27) | Horizontal display size = (Reg[04]+1)*8 = (39+1) * 8 = 320 pixels        |                            |  |

| [05]     | 1110 1111 (EF) | Vertical display size = Reg[06][05] + 1                                  |                            |  |

| [06]     | 0000 0000 (00) | = 0000 0000 1110 1111 + 1 = 239 +1 = 240 lines                           |                            |  |

| [07]     | 0000 0000 (00) | FPLINE start position (only required for TFT configuration)              |                            |  |

| [80]     | 0000 0000 (00) | Horizontal non-display period = (Reg[08] + 4) * 8<br>= 4 * 8 = 32 pixels | Frame Rate Calculation     |  |

| [09]     | 0000 0000 (00) | FPFRAME start position (only required for TFT configuration)             |                            |  |

| [0A]     | 0000 0011 (03) | Vertical non-display period = REG[0A] = 3 lines                          | Frame Rate Calculation     |  |

| [0B]     | 0000 0000 (00) | MOD rate is only required by some monochrome panels                      |                            |  |

| [0C]     | 0000 0000 (00) | Screen 1 Start Address - set to 0 for initialization                     | Split Screen on page 29    |  |

| [0D]     | 0000 0000 (00) | - Screen 1 Start Address - Set to 0 101 Initialization                   | Split Screen on page 29    |  |

| [0E]     | 0000 0000 (00) | Screen 2 Start Address - set to 0 for initialization                     | Split Screen on page 29    |  |

| [0F]     | 0000 0000 (00) | - Screen 2 Start Address - Set to 0 for initialization                   | Split Screen on page 29    |  |

| [10]     | 0000 0000 (00) | Screen 1 / Screen 2 Start Address MSB - set to 0                         |                            |  |

| [11]     | 0000 0000 (00) | Memory Address offset - not virtual setup - so set to 0                  | Virtual Display on page 23 |  |

| [12]     | 1111 1111 (FF) | Set the vertical size to the maximum value.                              | Split Screen on page 29    |  |

| [13]     | 0000 0011 (03) | Get the vertical size to the maximum value.                              | Split Screen on page 29    |  |

| [15]     |                | Leave the LUT alone for now                                              | Look-Up Table (LUT) on     |  |

| [17]     |                | Leave the LOT alone for now                                              | page 13                    |  |

| [18]     | 0000 0000 (00) | GPIO control and status registers - set to "0".                          |                            |  |

| [19]     | 0000 0000 (00) | Of 10 control and status registers - set to 0.                           |                            |  |

| [1A]     | 0000 0000 (00) | Set the scratch pad bits to "0".                                         |                            |  |

| [1B]     | 0000 0000 (00) | This is not portrait mode so set this register to "0".                   | Introduction To Hardware   |  |

| [1C]     | 0000 0000 (00) | Line Byte Count is only required for portrait mode.                      | Rotation on page 35        |  |

#### 2.3 Frame Rate Calculation

Frame rate specifies the number of complete frame which are drawn on the display in one second. Configuring a frame rate that is too high or too low adversely effects the quality of the displayed image.

System configuration imposes certain non-variable limitations. For instance the width and height of the display panel are fixed as is, typically, the input clock to the S1D13705. From the following formula it is evident that the two variables the programmer can use to adjust frame rate are horizontal and vertical non-display periods.

8

The following are the formulae for determining the frame rate of a panel. The formula for a single passive or TFT panel is calculated as follows:

$$FrameRate = \frac{PCLK}{(HDP + HNDP) \times (VDP + VNDP)}$$

for a dual passive panel the formula is:

$$FrameRate = \frac{PCLK}{2 \times (HDP + HNDP) \times \left(\frac{VDP}{2} + VNDP\right)}$$

```

where: PCLK

= Pixel clock (in Hz)

HDP

= Horizontal Display Period (in pixels)

HNDP = Horizontal Non-Display Period (in pixels)

= Vertical Display Period (in lines)

VDP

= Vertical Non-Display Period (in lines)

VNDP

```

In addition to varying the HNDP and VNDP times we can also select divider values which will reduce CLKi to one half, one quarter up to one eight of the CLKi value. The example below is a portion of a 'C' routine to calculate HNDP and VNDP from a desired frame rate.

```

for (int loop = 0; loop < 2; loop++)

for (VNDP = 2; VNDP < 0x3F; VNDP += 3)

// Solve for HNDP

HNDP = (PCLK / (FrameRate * (VDP + VNDP))) - HDP;

if ((HNDP >= 32) \&\& (HNDP <= 280))

// Solve for VNDP.

VNDP = (PCLK / (FrameRate * (HDP + HNDP))) - VDP;

// If we have satisfied VNDP then we're done.

if ((VNDP >= 0) \&\& (VNDP <= 0x3F))

goto DoneCalc;

}

// Divide ClkI and try again.

// (Reg[02] allows us to dived CLKI by 2)

PCLK /= 2;

// If we still can't hit the frame rate - throw an error.

if ((VNDP < 0) || (VNDP > 0x3F) || (HNDP < 32) || (HNDP > 280))

sprintf("ERROR: Unable to set the desired frame rate.\n");

exit(1);

}

```

This routine first performs a formula rearrangement so that HNDP or VNDP can be solved. Start with VNDP set to a small value. Loop increasing VNDP and solving the equation for HNDP until satisfactory HNDP and VNDP values are found. If no satisfactory values are found then divide CLKI and repeat the process. If a satisfactory frame rate still can't be reached - return an error.

#### Note

Most passive (STN) panels are tolerant of nearly any combination of HNDP and VNDP values, however panel specifications generally specify only a few lines of vertical non-display period. The S1D13705 is capable of generating a vertical non-display period of up to sixty-three lines. This amount of VNDP is far too great a non-display period and will likely degrade display quality. Similarly, setting a large HNDP value may cause a degrade in image quality.

If possible the system should be designed such that VNDP values of 7 or less lines and HNDP values of 20 or less characters can be selected.

## 3 Memory Models

The S1D13705 is capable of operating at four different color depths. For each color depth the data format is packed pixel. S1D13705 packed pixel modes can range from one byte containing eight adjacent pixels (1-bpp) to one byte containing just one pixel (8-bpp).

Packed pixel data may be envisioned as a stream of pixels. In this stream, pixels are packed in adjacent to each other. If a pixel requires four bits then it will be located in the four most significant bits of a byte. The pixel to the immediate right on the display will occupy the lower four bits of the same byte. The next two pixels to the immediate right are located in the following byte, etc.

#### 3.1 1 Bit-Per-Pixel (2 Colors/Gray Shades)

1-bit pixels support two color/gray shades. In this memory format each byte of display buffer contains eight adjacent pixels. Setting or resetting any pixel requires reading the entire byte, masking out appropriate bits and, if necessary, setting bits to "1".

When using a color panel the two colors are derived by indexing into positions 0 and 1 of the Look-Up Table. If the first two LUT elements are set to black (RGB = 0 0 0) and white (RGB = F F) then each "0" bit of display memory will display as a black pixel and each "1" bit will display as a white pixel. The two LUT entries can be set to any desired colors, for instance red and green or cyan and yellow.

For monochrome panels the two displayed gray shades are generated by indexing into the first two elements of the green component of the Look-Up Table (LUT). Thus, by manipulating the green LUT components we can set either of the two gray shades to any of sixteen possible levels.

| Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| Pixel 0 | Pixel 1 | Pixel 2 | Pixel 3 | Pixel 4 | Pixel 5 | Pixel 6 | Pixel 7 |

Figure 3-1: Pixel Storage for 1 Bpp (2 Colors/Gray Shades) in One Byte of Display Buffer

#### 3.2 2 Bit-Per-Pixel (4 Colors/Gray Shades)

2-bit pixels support four color/gray shades. In this memory format each byte of display buffer contains four adjacent pixels. Setting or resetting any pixel requires reading the entire byte, masking out the appropriate bits and, if necessary, setting bits to "1".

Color panels derive their four colors by indexing into positions 0 through 3 of the Look-Up Table. These four LUT entries can be set to any of the 4096 possible color combinations.

Monochrome panels derive four gray shades by indexing into the first four elements of the green component of the Look-Up Table. Any of the four LUT entries can be set to any of the sixteen possible gray shades.

| Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| Pixel 0 | Pixel 0 | Pixel 1 | Pixel 1 | Pixel 2 | Pixel 2 | Pixel 3 | Pixel 3 |

| Bit 1   | Bit 0   |

Figure 3-2: Pixel Storage for 2 Bpp (4 Colors/Gray Shades) in One Byte of Display Buffer

#### 3.3 4 Bit-Per-Pixel (16 Colors/Gray Shades)

Four bit pixels support 16 color/gray shades. In this memory format each byte of display buffer contains two adjacent pixels. Setting or resetting any pixel requires reading the entire byte, masking out the upper or lower nibble (4 bits) and setting the appropriate bits to "1".

Color panels can display up to sixteen colors simultaneously. These sixteen colors are derived by indexing into the first sixteen elements of the Look-Up Table. Each of these colors may be selected from the 4096 possible available colors.

On a monochrome panel the gray shades are generated by indexing into the first sixteen green components of the LUT. Each of these sixteen possible gray shades can be adjusted to any of the sixteen possible gray shades. For instance, one could program the first eight green LUT entries to be 0 and the second green LUT entries to be FFh. This would result in nibble values of 0 through 7 displaying as black and nibble values 8 through 0Fh displaying as white.

| Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| Pixel 0 | Pixel 0 | Pixel 0 | Pixel 0 | Pixel 1 | Pixel 1 | Pixel 1 | Pixel 1 |

| Bit 3   | Bit 2   | Bit 1   | Bit 0   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

Figure 3-3: Pixel Storage for 4 Bpp (16 Colors/Gray Shades) in One Byte of Display Buffer

#### 3.4 Eight Bit-Per-Pixel (256 Colors)

In eight bit-per-pixel mode one byte of display buffer represents one pixel on the display. At this color depth the read-modify-write cycles, required by the lessor pixel depths, are eliminated.

When using a color panel, each byte of display memory acts as and index to one element of the LUT. The displayed color is arrived at by taking the display memory value as an index into the LUT.

Eight bit per pixel is not supported for monochrome display modes. The reason is that each element of the LUT supports a 4-bit (sixteen value) level for red, green and blue. In monochrome display modes on the green value is used to set the gray intensity. Thus we have sixteen possible grey values but, because of the color

| Bit 7     | Bit 6     | Bit 5     | Bit 4       | Bit 3       | Bit 2       | Bit 1      | Bit 0      |

|-----------|-----------|-----------|-------------|-------------|-------------|------------|------------|

| Red bit 2 | Red bit 1 | Red bit 0 | Green bit 2 | Green bit 1 | Green bit 0 | Blue bit 1 | Blue bit 0 |

Figure 3-4: Pixel Storage for 8 Bpp (256 Colors) in One Byte of Display Buffer

## 4 Look-Up Table (LUT)

This section is supplemental to the description of the Look-Up Table architecture found in the S1D13705 Hardware Functional Specification. Covered here is a review of the LUT registers, recommendations for the color and gray shade LUT values, and additional programming considerations for the LUT. Refer to the S1D13705 Hardware Functional Specification, document number X27A-A-001-xx for more detail.

The S1D13705 Look-Up Table consists of 256 indexed red/green/blue entries. Each entry is 4 bits wide. Two registers, REG[15h] and REG[17h], control access to the LUT.

Each Look-Up Table entry consists of a red, green, and blue component. Each component consisting of four bits, or sixteen intensity levels. Any Look-Up Table element can be selected from a palette of 4096 (16x16x16) colors.

In color display modes, pixel values are used as an index to an RGB value stored in the Look-Up Table. In monochrome modes, pixel values still index into the LUT, but only the green component is used to determine display intensity.

The selected color depth determines how many index positions are used for image display. For example at one bit-per-pixel (bpp) only index positions 0 and 1 of the Look-Up Table are used. At 4-bpp the first 16 index positions of the Look-Up Table are used and at 8-bpp all 256 Look-Up Table index positions are used.

The Look-Up Table mechanism itself consists of an index register and a data register. The index, or address, register determines which element of the Look-Up Table will be accessed. After setting the index the LUT may be read or written through the data register. The first data element read or written is the red component of the entry. Subsequent read/write operations access the green and then the blue elements of the Look-Up Table.

The S1D13705 LUT architecture is designed to provide a high degree of similarity in operation to a standard VGA RAMDAC. However, there are two considerations which must be kept in mind.

• The S1D13705 Look-Up Table has four bits (16 levels) of intensity per primary color. The standard VGA RAMDAC has six bits (64 levels). This four to one difference must be taken into consideration when converting from a VGA palette to a LUT palette. One suggestion is to divide the VGA intensity level by four to arrive at the LUT intensity.

However, most applications specify the red, green and blue components as eight bit intensities. To determine the appropriate S1D13705 Look-Up Table value we recommend using the four most significant bits.

#### 4.1 Look-Up Table Registers

| REG[15h] Look-Up Table Address Register |             |             |             |             |             |             | Read/Write  |

|-----------------------------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| LUT Address                             | LUT Address | LUT Address | LUT Address | LUT Address | LUT Address | LUT Address | LUT Address |

| Bit 7                                   | Bit 6       | Bit 5       | Bit 4       | Bit 3       | Bit 2       | Bit 1       | Bit 0       |

#### **LUT Address**

The LUT address register selects which of the 256 LUT entries will be accessed. After three successive reads/writes to the data register this register is automatically incremented to point to the next address.

| REG[17h] Lo       | ok-Up Table D     | Data Register     |                   |     |     |     | Read/Write |

|-------------------|-------------------|-------------------|-------------------|-----|-----|-----|------------|

| LUT Data<br>Bit 3 | LUT Data<br>Bit 2 | LUT Data<br>Bit 1 | LUT Data<br>Bit 0 | n/a | n/a | n/a | n/a        |

#### **LUT Data**

This register is where the 4-bit red/green/blue data value is written/read. Immediately after setting the LUT index with register [15h] this register accesses the red element of the Look-Up Table. With each successive write/read the internal bank select is incremented. Thus the second access is from the green element and the third is from the blue element.

After the third access the LUT Address is incremented by one, then next access to this register will be the red element of the next Look-Up Table index.

#### 4.2 Look-Up Table Organization

#### 4.2.1 Color Modes

#### 1 bpp color

When the S1D13705 is configured for 1 bpp color mode, the LUT is limited to selecting colors from the first two entries. The two LUT entries can be any two RGB values but are typically set to black-and-white.

Each byte in the display buffer contains eight adjacent pixels. If a bit has a value of "0" then the color in LUT 0 index is displayed. A bit value of "1" results in the color in LUT 1 index being displayed.

The following table shows the recommended values for obtaining a black-and-white mode while in 1 bpp on a color panel.

Table 4-1: Recommended LUT Values for 1 Bpp Color Mode

| Index | Red | Green | Blue |

|-------|-----|-------|------|

| 00    | 00  | 00    | 00   |

| 01    | F0  | F0    | F0   |

| 02    | 00  | 00    | 00   |

| •••   | 00  | 00    | 00   |

| FF    | 00  | 00    | 00   |

| unused entries |

|----------------|

#### 2 bpp color

When the S1D13705 is configured for 2 bpp color mode, the displayed colors are selected from the first four entries of the Look-Up Table. The LUT entries may be set to any of the 4096 possible colors.

Each byte in the display buffer contains four adjacent pixels. If a bit combination has a value of "00" then the color in LUT index 0 is displayed. A bit value of "01" results in the color in LUT index 1 being displayed. Likewise the bit combination of "10" displays from the third LUT entry and "11" displays a color from the fourth LUT entry.

The following table shows the example values for 2 bit-per-pixel display mode.

Table 4-2: Example LUT Values for 2 Bpp Color Mode

| Index | Red | Green | Blue |

|-------|-----|-------|------|

| 00    | 00  | 00    | 00   |

| 01    | 70  | 70    | 70   |

| 02    | A0  | A0    | A0   |

| 03    | F0  | F0    | F0   |

| 04    | 00  | 00    | 00   |

|       | 00  | 00    | 00   |

| FF    | 00  | 00    | 00   |

indicates unused entries

#### 4 bpp color

When the S1D13705 is configured for 4 bpp color mode, the displayed colors are selected from the first sixteen entries of the Look-Up Table. The LUT entries may be set to any of the 4096 possible colors.

Each byte in the display buffer contains two adjacent pixels. If a nibble has a value of "0000" then the color in LUT index 0 is displayed. A nibble value of "0001" results in the color in LUT index 1 being displayed. The pattern continues to the nibble pattern of "1111" which results in the sixteenth color of the Look-Up Table being displayed.

The following table shows the example values for 4 bit-per-pixel display mode. These colors simulate the colors used by the sixteen color modes of a VGA.

Table 4-3: Suggested LUT Values to Simulate VGA Default 16 Color Palette

| Index | Red | Green | Blue |  |  |

|-------|-----|-------|------|--|--|

| 00    | 00  | 00    | 00   |  |  |

| 01    | 00  | 00    | A0   |  |  |

| 02    | 00  | A0    | 00   |  |  |

| 03    | 00  | A0    | A0   |  |  |

| 04    | A0  | 00    | 00   |  |  |

| 05    | A0  | 00    | A0   |  |  |

| 06    | A0  | A0    | 00   |  |  |

| 07    | A0  | A0    | A0   |  |  |

| 08    | 00  | 00    | 00   |  |  |

| 09    | 00  | 00    | F0   |  |  |

| 0A    | 00  | F0    | 00   |  |  |

| 0B    | 00  | F0    | F0   |  |  |

| 0C    | F0  | 00    | 00   |  |  |

| 0D    | F0  | 00    | F0   |  |  |

| 0E    | F0  | F0    | 00   |  |  |

| 0F    | F0  | F0    | F0   |  |  |

| 10    | 00  | 00    | 00   |  |  |

|       | 00  | 00    | 00   |  |  |

| FF    | 00  | 00    | 00   |  |  |

indicates unused entries

#### 8 bpp color

When the S1D13705 is configured for 8 bpp color mode the entire Look-Up Table is used to display images. Each of the LUT entries may be set to any of the 4096 possible colors.

Each byte in the display buffer represents one pixels. The byte value is used directly as an index into one of the 256 LUT entries. A display memory byte with a value of 00h will display the color contained in the first Look-Up Table entry while a display memory byte of FFh will display a color formed byte the two hundred and fifty sixth Look-Up Table entry.

The following table depicts LUT values which approximate the VGA default 256 color palette.

Table 4-4: Suggested LUT Values to Simulate VGA Default 256 Color Palette

| Index | R  | G  | В  |

|-------|----|----|----|-------|----|----|----|-------|----|----|----|-------|----|----|----|

| 00    | 00 | 00 | 00 | 40    | F0 | 70 | 70 | 80    | 30 | 30 | 70 | C0    | 00 | 40 | 00 |

| 01    | 00 | 00 | A0 | 41    | F0 | 90 | 70 | 81    | 40 | 30 | 70 | C1    | 00 | 40 | 10 |

| 02    | 00 | A0 | 00 | 42    | F0 | В0 | 70 | 82    | 50 | 30 | 70 | C2    | 00 | 40 | 20 |

| 03    | 00 | A0 | A0 | 43    | F0 | D0 | 70 | 83    | 60 | 30 | 70 | C3    | 00 | 40 | 30 |

| 04    | A0 | 00 | 00 | 44    | F0 | F0 | 70 | 84    | 70 | 30 | 70 | C4    | 00 | 40 | 40 |

| 05    | A0 | 00 | A0 | 45    | D0 | F0 | 70 | 85    | 70 | 30 | 60 | C5    | 00 | 30 | 40 |

| 06    | A0 | 50 | 00 | 46    | B0 | F0 | 70 | 86    | 70 | 30 | 50 | C6    | 00 | 20 | 40 |

| 07    | A0 | A0 | A0 | 47    | 90 | F0 | 70 | 87    | 70 | 30 | 40 | C7    | 00 | 10 | 40 |

| 08    | 50 | 50 | 50 | 48    | 70 | F0 | 70 | 88    | 70 | 30 | 30 | C8    | 20 | 20 | 40 |

| 09    | 50 | 50 | F0 | 49    | 70 | F0 | 90 | 89    | 70 | 40 | 30 | C9    | 20 | 20 | 40 |

| 0A    | 50 | F0 | 50 | 4A    | 70 | F0 | В0 | 8A    | 70 | 50 | 30 | CA    | 30 | 20 | 40 |

| 0B    | 50 | F0 | F0 | 4B    | 70 | F0 | D0 | 8B    | 70 | 60 | 30 | СВ    | 30 | 20 | 40 |

| 0C    | F0 | 50 | 50 | 4C    | 70 | F0 | F0 | 8C    | 70 | 70 | 30 | CC    | 40 | 20 | 40 |

| 0D    | F0 | 50 | F0 | 4D    | 70 | D0 | F0 | 8D    | 60 | 70 | 30 | CD    | 40 | 20 | 30 |

| 0E    | F0 | F0 | 50 | 4E    | 70 | В0 | F0 | 8E    | 50 | 70 | 30 | CE    | 40 | 20 | 30 |

| 0F    | F0 | F0 | F0 | 4F    | 70 | 90 | F0 | 8F    | 40 | 70 | 30 | CF    | 40 | 20 | 20 |

| 10    | 00 | 00 | 00 | 50    | B0 | В0 | F0 | 90    | 30 | 70 | 30 | D0    | 40 | 20 | 20 |

| 11    | 10 | 10 | 10 | 51    | СО | B0 | F0 | 91    | 30 | 70 | 40 | D1    | 40 | 20 | 20 |

| 12    | 20 | 20 | 20 | 52    | D0 | B0 | F0 | 92    | 30 | 70 | 50 | D2    | 40 | 30 | 20 |

| 13    | 20 | 20 | 20 | 53    | ΕO | B0 | F0 | 93    | 30 | 70 | 60 | D3    | 40 | 30 | 20 |

| 14    | 30 | 30 | 30 | 54    | F0 | B0 | F0 | 94    | 30 | 70 | 70 | D4    | 40 | 40 | 20 |

| 15    | 40 | 40 | 40 | 55    | F0 | B0 | E0 | 95    | 30 | 60 | 70 | D5    | 30 | 40 | 20 |

| 16    | 50 | 50 | 50 | 56    | F0 | B0 | D0 | 96    | 30 | 50 | 70 | D6    | 30 | 40 | 20 |

| 17    | 60 | 60 | 60 | 57    | F0 | B0 | C0 | 97    | 30 | 40 | 70 | D7    | 20 | 40 | 20 |

| 18    | 70 | 70 | 70 | 58    | F0 | B0 | В0 | 98    | 50 | 50 | 70 | D8    | 20 | 40 | 20 |

| 19    | 80 | 80 | 80 | 59    | F0 | C0 | В0 | 99    | 50 | 50 | 70 | D9    | 20 | 40 | 20 |

| 1A    | 90 | 90 | 90 | 5A    | F0 | D0 | В0 | 9A    | 60 | 50 | 70 | DA    | 20 | 40 | 30 |

| 1B    | A0 | A0 | A0 | 5B    | F0 | E0 | В0 | 9B    | 60 | 50 | 70 | DB    | 20 | 40 | 30 |

Table 4-4: Suggested LUT Values to Simulate VGA Default 256 Color Palette (Continued)

| Index | R  | G  | В  |

|-------|----|----|----|-------|----|----|----|-------|----|----|----|-------|----|----|----|

| 1C    | В0 | В0 | В0 | 5C    | F0 | F0 | В0 | 9C    | 70 | 50 | 70 | DC    | 20 | 40 | 40 |

| 1D    | C0 | C0 | C0 | 5D    | E0 | F0 | В0 | 9D    | 70 | 50 | 60 | DD    | 20 | 30 | 40 |

| 1E    | E0 | E0 | E0 | 5E    | D0 | F0 | В0 | 9E    | 70 | 50 | 60 | DE    | 20 | 30 | 40 |

| 1F    | F0 | F0 | F0 | 5F    | C0 | F0 | В0 | 9F    | 70 | 50 | 50 | DF    | 20 | 20 | 40 |

| 20    | 00 | 00 | F0 | 60    | В0 | F0 | В0 | A0    | 70 | 50 | 50 | E0    | 20 | 20 | 40 |

| 21    | 40 | 00 | F0 | 61    | В0 | F0 | C0 | A1    | 70 | 50 | 50 | E1    | 30 | 20 | 40 |

| 22    | 70 | 00 | F0 | 62    | В0 | F0 | D0 | A2    | 70 | 60 | 50 | E2    | 30 | 20 | 40 |

| 23    | В0 | 00 | F0 | 63    | В0 | F0 | E0 | A3    | 70 | 60 | 50 | E3    | 30 | 20 | 40 |

| 24    | F0 | 00 | F0 | 64    | В0 | F0 | F0 | A4    | 70 | 70 | 50 | E4    | 40 | 20 | 40 |

| 25    | F0 | 00 | B0 | 65    | В0 | E0 | F0 | A5    | 60 | 70 | 50 | E5    | 40 | 20 | 30 |

| 26    | F0 | 00 | 70 | 66    | В0 | D0 | F0 | A6    | 60 | 70 | 50 | E6    | 40 | 20 | 30 |

| 27    | F0 | 00 | 40 | 67    | В0 | C0 | F0 | A7    | 50 | 70 | 50 | E7    | 40 | 20 | 30 |

| 28    | F0 | 00 | 00 | 68    | 00 | 00 | 70 | A8    | 50 | 70 | 50 | E8    | 40 | 20 | 20 |

| 29    | F0 | 40 | 00 | 69    | 10 | 00 | 70 | A9    | 50 | 70 | 50 | E9    | 40 | 30 | 20 |

| 2A    | F0 | 70 | 00 | 6A    | 30 | 00 | 70 | AA    | 50 | 70 | 60 | EA    | 40 | 30 | 20 |

| 2B    | F0 | В0 | 00 | 6B    | 50 | 00 | 70 | AB    | 50 | 70 | 60 | EB    | 40 | 30 | 20 |

| 2C    | F0 | F0 | 00 | 6C    | 70 | 00 | 70 | AC    | 50 | 70 | 70 | EC    | 40 | 40 | 20 |

| 2D    | В0 | F0 | 00 | 6D    | 70 | 00 | 50 | AD    | 50 | 60 | 70 | ED    | 30 | 40 | 20 |

| 2E    | 70 | F0 | 00 | 6E    | 70 | 00 | 30 | AE    | 50 | 60 | 70 | EE    | 30 | 40 | 20 |

| 2F    | 40 | F0 | 00 | 6F    | 70 | 00 | 10 | AF    | 50 | 50 | 70 | EF    | 30 | 40 | 20 |

| 30    | 00 | F0 | 00 | 70    | 70 | 00 | 00 | В0    | 00 | 00 | 40 | F0    | 20 | 40 | 20 |

| 31    | 00 | F0 | 40 | 71    | 70 | 10 | 00 | B1    | 10 | 00 | 40 | F1    | 20 | 40 | 30 |

| 32    | 00 | F0 | 70 | 72    | 70 | 30 | 00 | B2    | 20 | 00 | 40 | F2    | 20 | 40 | 30 |

| 33    | 00 | F0 | В0 | 73    | 70 | 50 | 00 | В3    | 30 | 00 | 40 | F3    | 20 | 40 | 30 |

| 34    | 00 | F0 | F0 | 74    | 70 | 70 | 00 | B4    | 40 | 00 | 40 | F4    | 20 | 40 | 40 |

| 35    | 00 | B0 | F0 | 75    | 50 | 70 | 00 | B5    | 40 | 00 | 30 | F5    | 20 | 30 | 40 |

| 36    | 00 | 70 | F0 | 76    | 30 | 70 | 00 | В6    | 40 | 00 | 20 | F6    | 20 | 30 | 40 |

| 37    | 00 | 40 | F0 | 77    | 10 | 70 | 00 | В7    | 40 | 00 | 10 | F7    | 20 | 30 | 40 |

| 38    | 70 | 70 | F0 | 78    | 00 | 70 | 00 | B8    | 40 | 00 | 00 | F8    | 00 | 00 | 00 |

| 39    | 90 | 70 | F0 | 79    | 00 | 70 | 10 | В9    | 40 | 10 | 00 | F9    | 00 | 00 | 00 |

| 3A    | B0 | 70 | F0 | 7A    | 00 | 70 | 30 | BA    | 40 | 20 | 00 | FA    | 00 | 00 | 00 |

| 3B    | D0 | 70 | F0 | 7B    | 00 | 70 | 50 | BB    | 40 | 30 | 00 | FB    | 00 | 00 | 00 |

| 3C    | F0 | 70 | F0 | 7C    | 00 | 70 | 70 | ВС    | 40 | 40 | 00 | FC    | 00 | 00 | 00 |

| 3D    | F0 | 70 | D0 | 7D    | 00 | 50 | 70 | BD    | 30 | 40 | 00 | FD    | 00 | 00 | 00 |

| 3E    | F0 | 70 | B0 | 7E    | 00 | 30 | 70 | BE    | 20 | 40 | 00 | FE    | 00 | 00 | 00 |

| 3F    | F0 | 70 | 90 | 7F    | 00 | 10 | 70 | BF    | 10 | 40 | 00 | FF    | 00 | 00 | 00 |

#### 4.2.2 Gray Shade Modes

Gray shade modes are monochrome display modes. Monochrome display modes use the Look-Up Table in a very similar fashion to the color modes. This most significant difference is that the monochrome display modes use only the intensity of the green element of the Look-Up Table to form the gray level.

One side effect of using only green for intensity selection is that in gray shade modes there are only sixteen possible intensities. 8 bit-per-pixel is not supported for gray shade modes.

#### 1 bpp gray shade

When the S1D13705 is configured for 1 bpp gray shade mode, the LUT is limited to selecting colors from the first two green entries. The two LUT entries can be set to any of sixteen possible intensities. Typically they would be set to 0h (black) and Fh (white).

Each byte in the display buffer contains eight adjacent pixels. If a bit has a value of "0" then the color in the green LUT 0 index is displayed. A bit value of "1" results in the color in green LUT 1 index being displayed.

The following table shows the recommended values 1 bpp gray shade display mode.

| Address | Red | Green | Blue |

|---------|-----|-------|------|

| 00      | 00  | 00    | 00   |

| 01      | 00  | F0    | 00   |

| 02      | 00  | 00    | 00   |

|         | 00  | 00    | 00   |

| FF      | 00  | 00    | 00   |

Table 4-5: Recommended LUT Values for 1 Bpp Gray Shade

|  | unused entries |

|--|----------------|

#### 2 bpp gray shade

When the S1D13705 is configured for 2 bpp gray shade, the displayed colors are selected from the first four green entries in the Look-Up Table. The remaining entries of the LUT are unused. Each of the four entries can be set to any of the sixteen possible colors.

Each byte in the display buffer contains four adjacent pixels. If a bit combination has a value of "00" then the intensity in the green LUT index 0 is displayed. A bit value of "01" results in the intensity represented by the green in LUT index 1 being displayed. Likewise the bit combination of "10" displays from the third LUT entry and "11" displays a from the fourth LUT entry.

The following table shows the example values for 2 bit-per-pixel display mode.

Table 4-6: Suggested Values for 2 Bpp Gray Shade

| Index | Red | Green | Blue |

|-------|-----|-------|------|

| 0     | 00  | 00    | 00   |

| 1     | 00  | 50    | 00   |

| 2     | 00  | A0    | 00   |

| 3     | 00  | F0    | 00   |

| 4     | 00  | 00    | 00   |

|       | 00  | 00    | 00   |

| FF    | 00  | 00    | 00   |

| indicates unused entries |

|--------------------------|

#### 4 bpp gray shade

When the S1D13705 is configured for 4 bpp gray shade mode the displayed colors are selected from the green values of the first sixteen entries of the Look-Up Table. Each of the sixteen entries can be set to any of the sixteen possible intensity levels.

Each byte in the display buffer contains two adjacent pixels. If a nibble pattern is "0000" then the green intensity of LUT index 0 is displayed. A nibble value of "0001" results in the green intensity in LUT index 1 being displayed. The pattern continues to the nibble pattern of "1111" which results in the sixteenth intensity of Look-Up Table being displayed.

The following table shows the example values for 4 bit-per-pixel display mode.

Table 4-7: Suggested LUT Values for 4 Bpp Gray Shade

| Index | Red | Green | Blue |

|-------|-----|-------|------|

| 00    | 00  | 00    | 00   |

| 01    | 00  | 10    | 00   |

| 02    | 00  | 20    | 00   |

| 03    | 00  | 30    | 00   |

| 04    | 00  | 40    | 00   |

| 05    | 00  | 50    | 00   |

| 06    | 00  | 60    | 00   |

| 07    | 00  | 70    | 00   |

| 08    | 00  | 80    | 00   |

| 09    | 00  | 90    | 00   |

| 0A    | 00  | A0    | 00   |

| 0B    | 00  | В0    | 00   |

| 0C    | 00  | C0    | 00   |

| 0D    | 00  | D0    | 00   |

| 0E    | 00  | E0    | 00   |

| 0F    | 00  | F0    | 00   |

| 10    | 00  | 00    | 00   |

|       | 00  | 00    | 00   |

| FF    | 00  | 00    | 00   |

indicates unused entries

## 5 Advanced Techniques

This section contains programming suggestions for the following:

- · virtual display

- panning and scrolling

- · split screen display

#### 5.1 Virtual Display

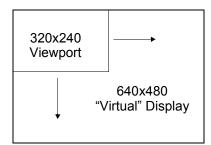

Virtual display refers to the situation where the image to be viewed is larger than the physical display. The difference can be in the horizontal, vertical or both dimensions. To view the image, the display is used as a window into the display buffer. At any given time only a portion of the image is visible. Panning and scrolling are used to view the full image.

The Memory Address Offset register determines the number of horizontal pixels in the virtual image. The offset register can be used to specify from 0 to 255 additional words for each scan line. At 1 bpp, 255 words span an additional 4,080 pixels. At 8 bpp, 255 words span an additional 510 pixels.

The maximum vertical size of the virtual image is the result of dividing 81920 bytes of display memory by the number of bytes on each line (i.e. at 1 bpp with a 320x240 panel set for a virtual width of 640x480 there is enough memory for 1024 lines).

Figure 5-1: "Viewport Inside a Virtual Display," depicts a typical use of a virtual display. The display panel is 320x240 pixels, an image of 640x480 pixels can be viewed by navigating a 320x240 pixel viewport around the image using panning and scrolling.

Figure 5-1: Viewport Inside a Virtual Display

#### 5.1.1 Registers

| REG[11h] Men | REG[11h] Memory Address Offset Register |         |         |         |         |         |         |  |  |  |  |

|--------------|-----------------------------------------|---------|---------|---------|---------|---------|---------|--|--|--|--|

| Memory       | Memory                                  | Memory  | Memory  | Memory  | Memory  | Memory  | Memory  |  |  |  |  |

| Address      | Address                                 | Address | Address | Address | Address | Address | Address |  |  |  |  |

| Offset       | Offset                                  | Offset  | Offset  | Offset  | Offset  | Offset  | Offset  |  |  |  |  |

| Bit 7        | Bit 6                                   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |  |  |  |  |

#### **Memory Address Offset Register**

REG[11h] forms an 8-bit value called the Memory Address Offset. This offset is the number of additional words on each line of the display. If the offset is set to zero there is no virtual width.

#### Note

This value does not represent the number of words to be shown on the display. The display width is set in the Horizontal Display Width register.

#### 5.1.2 Examples

#### Example 1: In this example we go through the calculations to display a 640x480 image on a 320x240 panel at 2 bpp.

Step 1: Calculate the number of pixels per word for this color depth.

At 2 bpp each byte is comprised of 4 pixels, therefore each word contains 8 pixels.

pixels per word =

$$16 / bpp = 16 / 2 = 8$$

Step 2: Calculate the Memory Address Offset register value

We require a total of 640 pixels. The horizontal display register will account for 320 pixels, this leaves 320 pixels for the Memory Address Offset register to account for.

offset = pixels / pixels per word =

$$320 / 8 = 40 = 28h$$

The Memory Address Offset register, REG[11h], will have to be set to 28h to satisfy the above condition.

## Example 2: From the above, what is the maximum number of lines our image can contain?

Step 1: Calculate the number of bytes on each line.

bytes per line = pixels per line / pixels per byte = 640 / 4 = 160

Each line of the display requires 160 bytes.

Step 2: Calculate the number of lines the S1D13705 is capable of.

total\_lines = memory / bytes\_per\_line = 81920 / 160 = 512

We can display a maximum of 512 lines. Our example image requires 480 lines so this example can be done.

### 5.2 Panning and Scrolling

Panning and scrolling describe the operation of moving a physical display viewport about a virtual image in order to view the entire image a portion at time. For example, after setting up the previous example (virtual display) and drawing an image into it we would only be able to view one quarter of the image. Panning and scrolling are used to reveal the rest of the image.

Panning describes the horizontal (side to side) motion of the viewport. When panning to the right the image in the viewport appears to slide to the left. When panning to the left the image to appears to slide to the right. Scrolling describes the vertical (up and down) motion of the viewport. Scrolling down causes the image to appear to slide up and scrolling up causes the image to appear to slide down.

Both panning and scrolling are performed by modifying the start address register. The start address registers in the S1D13705 are a word offset to the data to be displayed in the top left corner of a frame. Changing the start address by one means a change on the display of the number of pixels in one word. The number of pixels in word varies according to the color depth. At 1 bit-per-pixel a word contains sixteen pixels. At 2 bit-per-pixel there are eight pixels, at 4 bit-per-pixel there are four pixels and at 8 bit-per-pixel there is two pixels in each word. The number of pixels in each word represent the finest step we can pan to the left or right.

When portrait mode (see Hardware Rotation on page 35) is enabled the start address registers become offsets to bytes. In this mode the step rate for the start address registers if halved making for smoother panning.

#### 5.2.1 Registers

| REG[0Ch] So                                     | reen 1 Displa        | y Start Addres       | ss 0 (LSB)           |                      |                      |                     |                      |  |  |

|-------------------------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------|----------------------|--|--|

| Start Addr<br>Bit 7                             | Start Addr<br>Bit 6  | Start Addr<br>Bit 5  | Start Addr<br>Bit 4  | Start Addr<br>Bit 3  | Start Addr<br>Bit 2  | Start Addr<br>Bit 1 | Start Addr<br>Bit 0  |  |  |

| REG[0Dh] Screen 1 Display Start Address 1 (MSB) |                      |                      |                      |                      |                      |                     |                      |  |  |

| Start Addr<br>Bit 15                            | Start Addr<br>Bit 14 | Start Addr<br>Bit 13 | Start Addr<br>Bit 12 | Start Addr<br>Bit 11 | Start Addr<br>Bit 10 | Start Addr<br>Bit 9 | Start Addr<br>Bit 8  |  |  |

| REG[10h] Sc                                     | reen 1 Display       | y Start Addres       | ss 2 (MSB)           |                      |                      |                     |                      |  |  |

| n/a                                             | n/a                  | n/a                  | n/a                  | n/a                  | n/a                  | n/a                 | Start Addr<br>Bit 16 |  |  |

#### **Screen 1 Start Address Registers**

These three registers form the seventeen bit screen 1 start address. Screen 1 is displayed starting at the top left corner of the display.

In landscape mode these registers form the word offset to the first byte in display memory to be displayed in the upper left corner of the screen. Changing these registers by one will shift the display image 2 to 16 pixels, depending on the current color depth.

In portrait mode these registers form the offset to the display memory byte where screen 1 will start displaying. Changing these registers in portrait mode will result in a shift of 1 to 8 pixels depending on the color depth.

Refer to Table 5-1: "Number of Pixels Panned Using Start Address" to see the minimum number of pixels affected by a change of one to these registers

Landscape Mode Portrait Mode Color Depth (bpp) Pixels per Word **Pixels Per Byte Number of Pixels Panned Number of Pixels Panned** 16 16 2 8 4 4 8 2 4 4 4 2 8 2 2

Table 5-1: Number of Pixels Panned Using Start Address

#### 5.2.2 Examples

For the following examples we base our calculations on a 4 bit-per-pixel image displayed on a 256w x 64h panel. We have set up a virtual size of 320w x 240h. Width is greater than height so we are in landscape display mode. Refer to Section 2, "Initialization" on page 6 and Section 5.1, "Virtual Display" on page 23 for assistance with these settings.

These examples are shown using a C-like syntax.

#### Example 3: Panning (Right and Left)

To pan to the right increase the start address value by one. To pan to the left decrease the start address value. Keep in mind that, with the exception of 8 bit-per-pixel portrait display mode, the display will jump by more than one pixel as a result of changing the start address registers.

Panning to the right.

SetStartAddress(StartWord);

The routine GetStartAddress() is one which will read the start address registers and return the start address as a long value. It would be written similar to:

```

long GetStartAddress()

{

return ((REG[10] & 1) * 65536) + (REG[0D] * 256) + (REG[0C]);

}

```

The routine SetStartAddress() break up its long integer argument into three register values and store the values.

In this example code the notation REG[] refers to whatever mechanism is employed to read/write the registers.

}

#### Example 4: Scrolling (Up and Down)

To scroll down, increase the value in the Screen 1 Display Start Address Register by the number of words in one *virtual* scan line. To scroll up, decrease the value in the Screen 1 Display Start Address Register by the number of words in one *virtual* scan line. A virtual scan line includes both the number of bytes required by the physical display and any extra bytes that may be being used for creating a virtual width on the display.

The previous dimensions are still in effect for this example (i.e. 320w x 240h virtual size, 256h x 64w physical size at 4 bpp)

```

Step 1: Determine the number of words in one virtual scanline.

```

```

bytes_per_line = pixels_per_line / pixels_per_byte = 320 / 2 = 160

words_per_line = bytes_per_line / 2 = 160 / 2 = 80

Step 2: Scroll up or down

To scroll up.

StartWord = GetStartAddress();

StartWord -= words_per_line;

if (StartWord < 0)

StartWord = 0;

SetStartAddress(StartWord);

To scroll down.

StartWord = GetStartAddress();

StartWord += words_per_line;

SetStartAddress(StartWord);</pre>

```

#### 5.3 Split Screen

Occasionally the need arises to display two different but related images. Take, for example, a game where the main play area requires rapid updates and game status, displayed at the bottom of the screen, requires infrequent updates.

The Split Screen feature of the S1D13705 allows a programmer to setup a display in such a manor. When correctly configured the programmer has only to update the main area on a regular basis. Occasionally, as the need arises, the secondary area is updated.

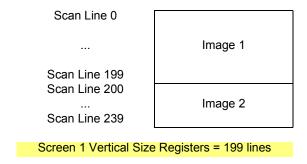

The figure below illustrates how a 320x240 panel may be configured to have one image displaying from scan line 0 to scan line 199 and image 2 displaying from scan line 200 to scan line 239. Although this example picks specific values, the split between image 1 and image 2 may occur at any line of the display.

Figure 5-2: 320x240 Single Panel For Split Screen

In split screen operation "Image 1" is taken from the display memory location pointed to by the Screen 1 Start Address registers and is always located at the top of the screen. "Image 2" is taken from the display memory location pointed to by the Screen 2 Start Address registers. The line where "Image 1" end and "Image 2" begins is determined by the Screen 1 Vertical Size register.

#### 5.3.1 Registers

Split screen operation is performed primarily by manipulating three register sets. Screen 1 Start Address and Screen 2 Start Address determine from where in display memory the first and second images will be taken from. The Vertical Size registers determine how many lines Screen 1 will use. The following is a description of the registers used to do split screen.

| REG[12] Scree               | REG[12] Screen 1 Vertical Size (LSB) |       |       |       |       |       |       |  |  |  |  |

|-----------------------------|--------------------------------------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| Bit 7                       | Bit 6                                | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |  |

| REG[13] Scree               | REG[13] Screen 1 Vertical Size (MSB) |       |       |       |       |       |       |  |  |  |  |

| n/a n/a n/a n/a Bit 9 Bit 8 |                                      |       |       |       |       |       |       |  |  |  |  |

#### **Screen 1 Vertical Size**

These two registers form a ten bit value which determines the size of screen 1. When the vertical size is equal to or greater than the physical number of lines being displayed there is no visible effect on the display. When the vertical size value is less than the number of physical display lines, operation is like this:

- 1. From the beginning of a frame to the number of lines indicated by vertical size the display data will come from the memory area pointed to by the Screen 1 Display Start Address.

- 2. After *vertical size* lines have been displayed the system will begin displaying data from the memory area pointed to by Screen 2 Display Start Address.

On thing that must be pointed out here is that Screen 1 memory is **always** displayed at the top of the screen followed by screen 2 memory. This relationship holds true regardless of where in display memory Screen 1 Start Address and Screen 2 Start Address are pointing. For instance, Screen 2 Start Address may point to offset zero of display memory while Screen 1 Start Address points to a location several thousand bytes higher. Screen 1 will still be shown first on the display. While not particularly useful, it is even possible to set screen 1 and screen 2 to the same address.

| REG[0Eh] Screen 2 Display Start Address 0 (LSB) |                     |                     |                     |                     |                     |                     |                     |  |  |  |  |

|-------------------------------------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|--|--|--|--|

| Start Addr Bit<br>7                             | Start Addr Bit<br>6 | Start Addr Bit<br>5 | Start Addr Bit<br>4 | Start Addr Bit<br>3 | Start Addr Bit<br>2 | Start Addr Bit<br>1 | Start Addr Bit<br>0 |  |  |  |  |

| REG[0Fh] Screen 2 Display Start Address 1 (MSB) |                     |                     |                     |                     |                     |                     |                     |  |  |  |  |

| Start Addr Bit                                  | Start Addr Bit      | Start Addr Bit      | Start Addr Bit      | Start Addr Bit      | Start Addr Bit      | Start Addr Bit      | Start Addr Bit      |  |  |  |  |

#### Screen 2 Start Address Registers

These three registers form the seventeen bit Screen 2 Start Address. Screen 2 is always displayed immediately following the screen 1 data and will begin at the left-most pixel on a line. Keep in mind that if the Screen 1 Vertical Size is equal to or greater than the physical display then Screen 2 will not be shown.

In landscape mode these registers form the word offset to the first byte in display memory to be displayed. Changing these registers by one will shift the display image 2 to 16 pixels, depending on the current color depth.

The S1D13705 does not support split screen operation in portrait mode. Screen 2 will never be used if portrait mode is selected.

Refer to Table 5-1: "Number of Pixels Panned Using Start Address" to see the minimum number of pixels affected by a change of one to these registers

Screen 1 Start Address registers, REG[0C], REG[0D] and REG[10] are discussed in Section 5.2.1 on page 26

#### 5.3.2 Examples

## Example 5: Display 200 scanlines of image 1 and 40 scanlines of image 2. Image 2 is located first (offset 0) in the display buffer followed immediately by image 1. Assume a 320x240 display and a color depth of 4 bpp.

1. Calculate the Screen 1Vertical Size register values.

```

vertical size = 200 = C8h

```

Write the Vertical Size LSB, REG[12h], with C8h and Vertical Size MSB, REG[13h], with a 00h.

2. Calculate the Screen 1 Start Word Address register values.

Screen 2 is located first in display memory, therefore we must calculate the number of bytes taken up by the screen 2 data.

bytes per line = pixels per line / pixels per byte = 320 / 2 = 160

total bytes = bytes per line x lines =  $160 \times 40 = 6400$ .

Screen 2 requires 6400 bytes (0 to 6399) therefore the start address offset for screen 1 must be 6400 bytes. (6400 bytes = 3200 words = C80h words)

Set the Screen 1 Start Word Address MSB, REG[0Dh], to 0Ch and the Screen 1 Start Word Address LSB, REG[0Ch], to 80h.

3. Calculate the Screen 2 Start Word Address register values.

Screen 2 display data is coming from the very beginning of the display buffer. All there is to do here is ensure that both the LSB and MSB of the Screen 2 Start Word Address registers are set to zero.

## 6 LCD Power Sequencing and Power Save Modes

#### 6.1 LCD Power Sequencing

Correct power sequencing is required to prevent long term damage to LCD panels and to avoid unsightly "lines" during power-up and power-down. Power Sequencing allows the LCD power supply to discharge prior to shutting down the LCD logic signals.

Proper LCD power sequencing dictates there must be a time delay between the LCD power being disabled and the LCD signals being shut down. During power-up the LCD signals must be active prior to or when power is applied to the LCD. The time intervals vary depending on the power supply design.

The S1D13705 performs automatic power sequencing in response to both software power save (REG[03h]) or in response to a hardware power save. One frame after a power save mode is set, the S1D13705 disables LCD power, and the LCD logic signals continue for one hundred and twenty seven frames allowing the LCD power supply to completely discharge. For most applications the internal power sequencing is the appropriate choice.

There may be situations where the internal time delay is insufficient to discharge the LCD power supply before the LCD signals are shut down, or the delay is too long and the designer wishes to shorten it. This section details the sequences to manually power-up and power-down the LCD interface.

#### 6.2 Registers

| REG[03h] Mode Register 2 |  |  |  |                    |                                  |                                 |                                 |  |  |  |  |

|--------------------------|--|--|--|--------------------|----------------------------------|---------------------------------|---------------------------------|--|--|--|--|

|                          |  |  |  | LCDPWR<br>Override | Hardware<br>Power Save<br>Enable | Software<br>Power Save<br>bit 1 | Software<br>Power Save<br>bit 0 |  |  |  |  |

The LCD Power (LCDPWR) Override bit forces LCD power inactive one frame after being toggled. As long as this bit is "1" LCD power will be disabled.

The Hardware Power Save Enable bit must be set in order to activate hardware power save through GPIO0.

The Software Power Save bits set and reset the software power save mode. These bits are set to "11" for normal operation and set to "00" for power save mode.

LCD logic signals to the display panel are active for 128 frames after setting either hardware or software power save modes. Power sequencing override is performed by setting the LCDPWR Override bit some time before setting a power save mode for power off sequences. During power on sequences the power save mode is reset some time before the LCDPWR Override is reset resulting in the LCD logic signals being active before power is applied to the panel.

#### 6.3 LCD Enable/Disable

The descriptions below cover manually powering the LCD panel up and down. Use the sequences described in this section if the power supply connected to the panel requires more than 127 frames to discharge on power-down, or if the panel requires starting the LCD logic well in advance of enabling LCD power. Currently there are no known circumstances where the LCD logic must be active well in advance of LCD power.

#### **Note**

If 127 frame period is to long, blank the display, then reprogram the Horizontal and Vertical sizes to produce a shorter frame period before using these methods.

#### Power On/Enable Sequence

The following is a sequence for manually powering-up an LCD panel if LCD power had to be applied later than LCD logic.

- 1. Set REG[03h] bit 3 (LCDPWR Override) to "1". This ensures that LCD power will be held disabled.

- 2. Enable LCD logic. This is done by either setting the GPIO0 pin low to disable hardware power save mode and/or by setting REG[03h] bits 1-0 to "11" to disable software power save.

- 3. Count "x" Vertical Non-Display Periods (OPTIONAL).

"x" corresponds the length of time LCD logic must be enabled before LCD power-up, converted to the equivalent vertical non-display periods. For example, at 72 HZ counting 36 non-display periods results in a one half second delay.

- 4. Set REG[03h] bit 3 to "0" to enable LCD Power.

#### Power Off/Disable Sequence

The following is a sequence for manually powering-down an LCD panel. These steps would be used if the power supply discharge requirements are larger than the default 127 frames.

- 1. Set REG[03h] bit 3 (LCDPWR Override) to "1" which will disable LCD Power.

- 2. Count "x" Vertical Non-Display Periods.

"x" corresponds to the power supply discharge time converted to the equivalent vertical non-display periods. (see the previous example)

- 3. Disable the LCD logic by setting the software power save in REG[03h] or setting hardware power save via GPIO0. Keep in mind that after setting the power save mode there will be 127 frames before the LCD logic signals are disabled.

#### 7 Hardware Rotation

#### 7.1 Introduction To Hardware Rotation

Many of todays applications use the LCD panel in a portrait orientation (typically LCD panels are landscape oriented). In this case it becomes necessary to "rotate" the displayed image. This rotation can be done by software at the expense of performance or, as with the S1D13705, it can be done by hardware with no performance penalty.

This discussion of display rotation is intended to augment the excellent description of the hardware functionality found in the Hardware Functional Specification.

The S1D13705 supports two portrait modes: Default Portrait Mode and Alternate Portrait Mode.

#### 7.2 Default Portrait Mode

Default portrait mode was designed to reduce power consumption for portrait mode use. The reduced power consumption comes with certain trade offs.

The most obvious difference between the two modes is that Default Portrait Mode requires the portrait width be a power of two, e.g. a 240-line panel, used in portrait mode, requires setting a virtual width of 256 pixels. Also default portrait mode is only capable of scrolling the display in two line increments.

The benefits to using default portrait mode lies in the ability to use a slower input clock and in reduced power consumption.

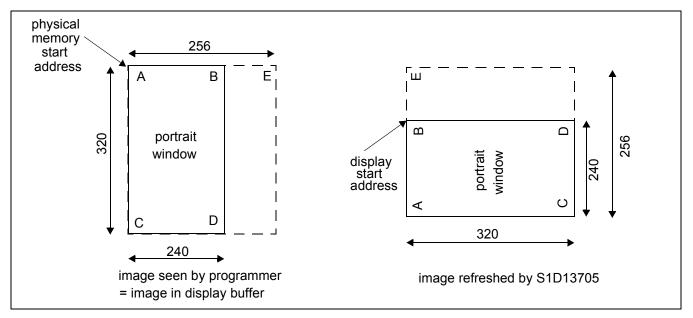

The following figure depicts the ways to envision memory layouts for the S1D13705 in default portrait mode. This example uses a 320x240 panel.

Figure 7-1: Relationship Between the Default Mode Screen Image and the Image Refreshed by S1D13705

From the programmers perspective the memory is laid out as shown on the left. The programmer accesses memory exactly as for a panel of with the dimensions of 240x320 setup to have a 256 pixel horizontal stride. The programmer sees memory addresses increasing from A->B and from B->C.

From a hardware perspective the S1D13705 always refreshes the LCD panel in the order B->D and down to do A->C.

#### 7.3 Alternate Portrait Mode

Alternate portrait mode does not impose the power of two line width. To rotated the image on 240 line panel requires a portrait stride of 240 pixels. Alternate portrait mode is capable of scrolling by one line at a time in response to changes to the Start Address Registers. However, to achieve the same frame rate requires a 2 x faster input clock, therefore using more power.

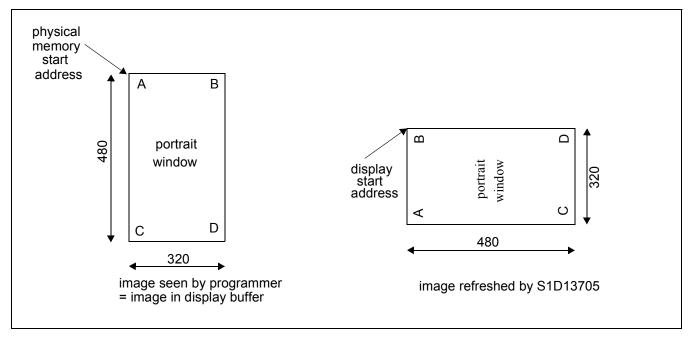

The following figure depicts the ways to envision memory layouts for the S1D13705 in alternate portrait mode. This example also uses a 320x240 panel. Notice that in alternate portrait mode the stride may be as little as 240 pixels.

Figure 7-2: Relationship Between the Alternate Mode Screen Image and the Image Refreshed by S1D13705

From the programmers perspective the memory is laid out as shown on the left. The programmer accesses memory exactly as for a panel of with the dimensions of 240x320. The programmer sees memory addresses increasing from A->B and from B->C.

From a hardware perspective the S1D13705 always refreshes the LCD panel in the order B->D and down to do A->C

The greatest factor in selecting alternate portrait mode over default portrait mode would be for the ability to obtain an area of contiguous off screen memory. For example: A 640x480 panel in default portrait mode at two bit-per-pixel requires 81920 bytes (80 Kb). There is unused memory but it is not contiguous. The same situation using alternate portrait mode requires 76800 bytes leaving 5120 bytes of contiguous memory available to the application. In fact the change in memory usage may make the difference between being able to run certain panels in portrait mode or not being able to do so.

# 7.4 Registers

This section describes the registers used to set portrait mode operation.

| REG[0Ch] Screen 1 Start Word Address LSB |                                          |        |        |        |        |       |        |

|------------------------------------------|------------------------------------------|--------|--------|--------|--------|-------|--------|

| bit 7                                    | bit 6                                    | bit 5  | bit 4  | bit 3  | bit 2  | bit 1 | bit 0  |

| REG[0Dh] Scr                             | REG[0Dh] Screen 1 Start Word Address MSB |        |        |        |        |       |        |

| bit 15                                   | bit 14                                   | bit 13 | bit 12 | bit 11 | bit 10 | bit 9 | bit 8  |

| REG[0Eh] Scr                             | REG[0Eh] Screen 1 Start Word Address MSB |        |        |        |        |       |        |

| n/a                                      | n/a                                      | n/a    | n/a    | n/a    | n/a    | n/a   | bit 16 |

The Screen 1 Start Address registers must be set correctly for portrait mode. In portrait mode the Start Address registers form a byte offset, as opposed to a word offset, into display memory.

The initial required offset is the portrait mode stride (in bytes) less one.

| REG[1Ch] Line Byte Count Register |       |       |       |       |       |       |       |

|-----------------------------------|-------|-------|-------|-------|-------|-------|-------|

| bit 7                             | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

The line byte count register informs the S1D13705 of the stride, in bytes, between two consecutive lines of display in portrait mode. The Line Byte Count register only affects portrait mode operation and are ignored when the S1D13705 is in landscape display mode.

| REG[1Bh] Portrait Mode Register |                         |     |     |     |                                         |                                              |                                              |

|---------------------------------|-------------------------|-----|-----|-----|-----------------------------------------|----------------------------------------------|----------------------------------------------|

| Portrait Mode<br>Enable         | Portrait Mode<br>Select | n/a | n/a | n/a | Portrait Mode<br>Memory<br>Clock Select | Portrait Mode<br>Pixel Clock<br>Select Bit 1 | Portrait Mode<br>Pixel Clock<br>Select Bit 0 |

The portrait mode register contains several items for portrait mode support.

The first is the Portrait Mode Enable bit. When this bit is "0" the S1D13705 is in landscape mode and the remainder of the settings in this register as well as the Line Byte Count in REG[1Ch] are ignored. Set this bit to "1" to enable portrait mode.

The portrait mode select bit selects between the "Default Mode" and the "Alternate Mode". Setting this bit to "0" selects the default portrait mode while setting this bit to "1" enables the alternate portrait mode.

Portrait Mode Memory Clock Select is another power saving measure which can be enabled if the final MCLK value is less than or equal to 25 MHz. Memory Clock Select results in the S1D13705 temporarily increasing the memory clock circuitry on CPU access and resuming the slower speed when the access is complete. This results in better performance while using the least power.

In portrait display mode the CLKI (input clock) is routed to the portrait section of the S1D13705 as CLK. From the CLK signal the MCLK value can be determined from table 8-8 of the Hardware Functional Specification, document number X27A-A-001-xx. If MCLK is determined to be less than or equal to 25 MHz then Portrait Mode Memory Clock Select may be enabled.

# 7.5 Limitations

The only limitation to using portrait mode on the S1D13705 is that split screen operation is not supported.

A comparison of the two portrait modes is as follows:

Table 7-1: Default and Alternate Portrait Mode Comparison

| Item                | Default Portrait Mode                                                                                                                                                                                                                                                                                                                                                                   | Alternate Portrait Mode                                                                                                                                                                                 |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Memory Requirements | The width of the rotated image must be a power of 2. In most cases, a virtual image is required where the right-hand side of the virtual image is unused and memory is wasted. For example, a 320x480x4bpp image would normally require only 76,800 bytes - possible within the 80K byte address space, but the virtual image is 512x480x4bpp which needs 122,880 bytes - not possible. | Does not require a virtual image.                                                                                                                                                                       |  |  |

| Clock Requirements  | CLK need only be as fast as the required PCLK.                                                                                                                                                                                                                                                                                                                                          | MCLK, and hence CLK, need to be 2x PCLK. For example, if the panel requires a 3MHz PCLK, then CLK must be 6MHz. Note that 25MHz is the maximum CLK, so PCLK cannot be higher than 12.5MHz in this mode. |  |  |

| Power Consumption   | Lowest power consumption.                                                                                                                                                                                                                                                                                                                                                               | Higher than Default Mode.                                                                                                                                                                               |  |  |

| Panning             | Vertical panning in 2 line increments.                                                                                                                                                                                                                                                                                                                                                  | Vertical panning in 1 line increments.                                                                                                                                                                  |  |  |

| Performance         | Nominal performance. Note that performance can be increased by increasing CLK and setting MCLK = CLK (REG[1Bh] bit 2 = 1).                                                                                                                                                                                                                                                              | Higher performance than Default Mode.<br>Note that performance can be increased by<br>increasing CLK and setting MCLK = CLK<br>(REG[1Bh] bit 2 = 1).                                                    |  |  |

# 7.6 Examples

#### Example 6: Enable default portrait mode for a 320x240 panel at 4 bpp.

Before switching to portrait mode from landscape mode, display memory should be cleared to make the user perceived transition smoother. Images in display memory are not rotated automatically by hardware and a garbled image would be visible for a short period of time if video memory is not cleared.

If alternate portrait is used then the CLK signal is divided in half to get the PCLK signal. If the Input Clock Divide bit, in register[02] is set we can simply reset the divider. The result of this is a PCLK of exactly the same frequency as we used for landscape mode and we can use the current horizontal and vertical non-display periods. If the Input Clock Divide bit is not set then we must recalculate the frame rate based on the a PCLK value. In this example we will bypass recalculation of the horizontal and vertical non-display times (frame rate) by selecting the default portrait mode scheme.

1. Calculate and set the Screen 1 Start Word Address register.

OffsetBytes = (Width x BitsPerPixel / 8) - 1 =  $(256 \times 4 / 8) - 1 = 127 = 007$ Fh

("Width" is the width of the portrait mode display - in this case the next power of two greater than 240 pixels or 256.)

Set Screen1 Display Start Word Address LSB (REG [0Ch]) to 7Fh and Screen1 Display Start Word Address MSB (REG[0Dh]) to 00h.

2. Calculate the Line Byte Count

The Line Byte Count also must be based on the power of two width.

LineByteCount = Width x BitsPerPixel  $/ 8 = 256 \times 4 / 8 = 128 = 80h$ .

Set the Line Byte Count (REG[1C]) to 80h.

3. Enable portrait mode.

This example uses the default portrait mode scheme. If we do not change the Portrait Mode Pixel Clock Select bits then we will not have to recalculate the non-display timings to correct the frame rate.

Write 80h to the Portrait Mode Register (REG[1Bh]).

The display is now configured for portrait mode use. Offset zero into display memory will corresponds to the upper left corner of the display. The only item to keep in mind is that the count from the first pixel of one line to the first pixel of the next line (referred to as the "stride") is 128 bytes.

#### Example 7: Enable alternate portrait mode for a 320x240 panel at 4 bpp.

#### Note

As we have to perform a frame rate calculation for this mode we need to know the following panel characteristics: 320x240 8-bit color to be run at 80 Hz with a 16 MHz input clock.

As in the previous example, before switching to portrait mode, display memory should be cleared. Images in display memory are not rotated automatically by hardware and the garbled image would be visible for a short period of time if video memory is not cleared.

1. Calculate and set the Screen 1 Start Word Address register.

OffsetBytes = (Width x BitsPerPixel / 8) - 1 = (240 x 4 / 8) - 1 = 119 = 0077h

Set Screen1 Display Start Word Address LSB (REG [0Ch]) to 77h and Screen1 Display Start Word Address MSB (REG[0Dh]) to 00h.

2. Calculate the Line Byte Count.

LineByteCount = Width x BitsPerPixel  $/ 8 = 240 \times 4 / 8 = 120 = 78 h$ .

Set the Line Byte Count (REG[1C]) to 78h.

3. Enable portrait mode.

This example uses the alternate portrait mode scheme. We will not change the MCLK Autoswitch or Pixel Clock Select settings.

Write C0h to the Portrait Mode register (REG[1Bh])