### **S1D13742 Mobile Graphics Engine**

# Interfacing the Sharp LQ043xxx 480x272 TFT Panel

Document Number: X63A-G-003-01.1

|   |   |   |   | _ |

|---|---|---|---|---|

| N | n | T | റ | ᆮ |

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. When exporting the products or technology described in this material, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You are requested not to use, to resell, to export and/or to otherwise dispose of the products (and any technical information furnished, if any) for the development and/or manufacture of weapon of mass destruction or for other military purposes.

All brands or product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

©SEIKO EPSON CORPORATION 2008-2018. All rights reserved.

# **Table Of Contents**

| Chapter 1 Interfacing the Sharp LQ043xxx 480x272 TFT Panel |                                                                  |  |  |  |  |

|------------------------------------------------------------|------------------------------------------------------------------|--|--|--|--|

| 1.1 Ove                                                    | rview                                                            |  |  |  |  |

| 1.1.1                                                      | Electrical Interface                                             |  |  |  |  |

| 1.1.2                                                      | S1D13742 Register Settings for Sharp LQ043xxx, 480x272 TFT Panel |  |  |  |  |

| Chapter 2 C                                                | hange Record                                                     |  |  |  |  |

| Chapter 3 Sa                                               | ales and Technical Support                                       |  |  |  |  |

# Chapter 1 Interfacing the Sharp LQ043xxx 480x272 TFT Panel

This document describes the hardware and software environment required to interface the S1D13742 Mobile Graphics Engine and Sharp LQ043xxxx 480x272 TFT Panel.

The designs described in this document are presented only as examples of how such interfaces might be implemented.

#### 1.1 Overview

The S1D13742 directly supports the Sharp LQ043xxx and requires no additional hardware and minimal programming. The S1D13742 register settings and electrical interface is described below.

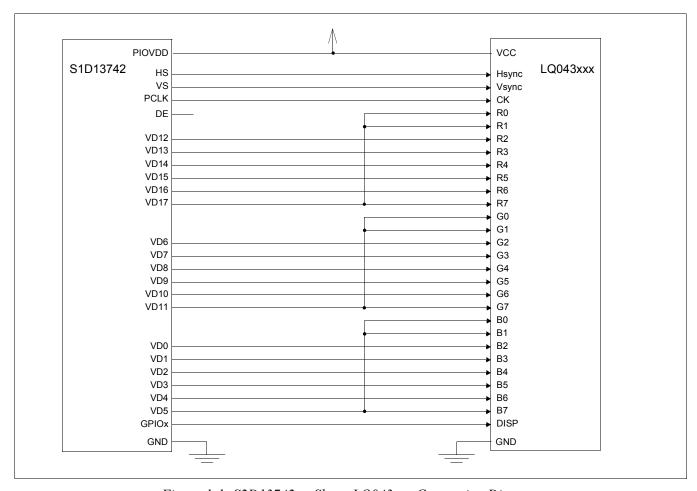

Figure 1-1: S2D13742 to Sharp LQ043xxx Connection Diagram

#### 1.1.1 Electrical Interface

6

Table 1-1: Pin Mapping

| S1D13742                      | LQ043xxxx |  |

|-------------------------------|-----------|--|

| Pin Name                      | Pin Name  |  |

| HS                            | Hsync     |  |

| VS                            | Vsync     |  |

| PCLK                          | CK        |  |

| DE                            | -         |  |

| VD17                          | R0        |  |

| VD17                          | R1        |  |

| VD12                          | R2        |  |

| VD13                          | R3        |  |

| VD14                          | R4        |  |

| VD15                          | R5        |  |

| VD16                          | R6        |  |

| VD17                          | R7        |  |

| VD11                          | G0        |  |

| VD11                          | G1        |  |

| VD6                           | G2        |  |

| VD7                           | G3        |  |

| VD8                           | G4        |  |

| VD9                           | G5        |  |

| VD10                          | G6        |  |

| VD11                          | G7        |  |

| VD5                           | B0        |  |

| VD5                           | B1        |  |

| VD0                           | B2        |  |

| VD1                           | B3        |  |

| VD2                           | B4        |  |

| VD3                           | B5        |  |

| VD4                           | B6        |  |

| VD5                           | B7        |  |

| GPIOx (any of GPIO[7:0] pins) | DISP      |  |

The same power must be connected to PIOVDD pins of S1D13742 and to VCC pins of Sharp LQ043xxx panel.

Display ON/OFF signal is provided by one of S1D13742 GPIO pins and it is under application software control. The Vertical Non-Display Period status bit or TE pin, can be used to comply with the Sharp LQ043xxx requirement that DISP signal does not change while Vsync is low.

#### 1.1.2 S1D13742 Register Settings for Sharp LQ043xxx, 480x272 TFT Panel

The registers listed below are only those associated with panel specific timing issues. All other registers are not shown here.

When a window is setup for YUV data, the data must always alternate between odd and even lines, starting with an odd line.

Table 1-2: Example Register Settings for Sharp LQ043xxx 480x272 TFT Panel

| Register       | Value                                                                          | Comment                                                  |  |  |

|----------------|--------------------------------------------------------------------------------|----------------------------------------------------------|--|--|

| All            | default                                                                        | Come out of reset - all registers set to default values  |  |  |

| REG[56h]       | 02h                                                                            | enter sleep mode (or use PWRSVE pin)                     |  |  |

|                |                                                                                | set PLL M-Divider.                                       |  |  |

| REG[04h]       | 03h                                                                            | CLKI = 4MHz,                                             |  |  |

| DE010011       | F01                                                                            | PLL input clock = CLKI/4 = 1MHz.                         |  |  |

| REG[06h]       | F8h                                                                            |                                                          |  |  |

| REG[08h]       | 80h                                                                            |                                                          |  |  |

| REG[0Ah]       | 28h                                                                            |                                                          |  |  |

| REG[0Ch]       | 00h                                                                            |                                                          |  |  |

| REG[0Eh]       | 3Eh                                                                            | LL = 63, resulting SYSCLK = LL x PLL input clock = 63MHz |  |  |

| REG[12h]       | 31h                                                                            | set PCLK divide, PCLK = 9MHz                             |  |  |

|                |                                                                                | set SYSCLK source = PLL                                  |  |  |

| REG[14h]       | 00h                                                                            | no panel data swap, 18-bit panel                         |  |  |

| REG[16h]       | 3Ch                                                                            | HDP = 480 pixels                                         |  |  |

| REG[18h]       | 2Dh                                                                            | HNDP = 45 pixels                                         |  |  |

| REG[1Ah]       | 10h                                                                            |                                                          |  |  |

| REG[1Ch]       | 01h                                                                            |                                                          |  |  |

| REG[1Eh]       | 0Eh                                                                            | VNDP = 14 lines                                          |  |  |

| REG[20h]       | 29h                                                                            | HS Pulse Width = 41 pixels                               |  |  |

| REG[22h]       | 02h                                                                            | HS Start Position = 2 pixels                             |  |  |

| REG[24h]       | 0Ah                                                                            | VS Width = 10 lines                                      |  |  |

| REG[26h]       | 02h                                                                            | VS Start Position (VFP) = 2 line                         |  |  |

| REG[28h]       | 00h                                                                            | PCLK Polarity: data output on rising edge                |  |  |

| REG[2Ah]       | 82h                                                                            | set memory to 18bpp, data mode to RGB 6:6:6 mode 1       |  |  |

| REG[56h]       | 00h                                                                            | disable sleep mode                                       |  |  |

| REG[04h] bit 7 | _                                                                              | wait for PLL to lock - poll REG[04h] bit 7               |  |  |

| REG[38h]       | 00h                                                                            | Window X Start Position = 0                              |  |  |

| REG[3Ah]       | 00h                                                                            | Willidow A Start Fosition - 0                            |  |  |

| REG[3Ch]       | 00h                                                                            | Window V Start Position = 0                              |  |  |

| REG[3Eh]       | 00h                                                                            | Window Y Start Position = 0                              |  |  |

| REG[40h]       | DFh                                                                            | Window X End Position = 479                              |  |  |

| REG[42h]       | 01h                                                                            | VVIIIGOW A EIIG FUSILIUII - 479                          |  |  |

| REG[44h]       | 0Fh                                                                            | Window V End Position - 271                              |  |  |

| REG[46h]       | 01h                                                                            | Window Y End Position = 271                              |  |  |

| REG[48h]       | Write the image data to the Memory Data Port, REG[48h] and REG[49h]. The image |                                                          |  |  |

| REG[49h]       | REG[49h] will immediately begin to appear on the LCD.                          |                                                          |  |  |

The above values are intended as examples. This example assumes that CLKI = 4MHz and that the PLL is used to generate SYSCLK. Actual settings can vary and still remain within the LCD panel timing requirements.

# **Chapter 2 Change Record**

X63A-A-001-00 Revision 1.1 - Issued: March 28, 2018

- updated Sales and Technical Support Section

- updated some formatting

X63A-A-001-00 Revision 1.0 - Issued: June 11, 2008

- all changes from the last revision are highlighted in Red

- initial release

# **Chapter 3 Sales and Technical Support**

For more information on Epson Display Controllers, visit the Epson Global website.

https://global.epson.com/products\_and\_drivers/semicon/products/display\_controllers/

For Sales and Technical Support, contact the Epson representative for your region.

https://global.epson.com/products\_and\_drivers/semicon/information/support.html