## S1D13A04 LCD/USB Companion Chip

# Programming Notes and Examples

Document Number: X37A-G-003-07.1

| N  | $\sim$ | т | റ  |  |

|----|--------|---|----|--|

| I٧ | U      | ' | IC |  |

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. When exporting the products or technology described in this material, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You are requested not to use, to resell, to export and/or to otherwise dispose of the products (and any technical information furnished, if any) for the development and/or manufacture of weapon of mass destruction or for other military purposes.

All brands or product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

©SEIKO EPSON CORPORATION 2001-2018. All rights reserved.

## **Table of Contents**

| 1 | Introduction                                                           |

|---|------------------------------------------------------------------------|

| 2 | Identifying the S1D13A04                                               |

| 3 | Initialization                                                         |

| 4 | Memory Models                                                          |

|   | 4.1 Display Buffer Location                                            |

|   | 4.2 Memory Organization for One Bit-per-pixel (2 Colors/Gray Shades)   |

|   | 4.3 Memory Organization for Two Bit-per-pixel (4 Colors/Gray Shades)   |

|   | 4.4 Memory Organization for Four Bit-per-pixel (16 Colors/Gray Shades) |

|   | 4.5 Memory Organization for 8 Bpp (256 Colors/64 Gray Shades)          |

|   | 4.6 Memory Organization for 16 Bpp (65536 Colors/64 Gray Shades)       |

| 5 | Look-Up Table (LUT)                                                    |

|   | 5.1 Registers                                                          |

|   | 5.1.1 Look-Up Table Write Register                                     |

|   | 5.1.2 Look-Up Table Read Registers                                     |

|   | 5.2 Look-Up Table Organization                                         |

|   | 5.2.1 Gray Shade Modes                                                 |

|   | 5.2.2 Color Modes                                                      |

| 6 | Power Save Mode                                                        |

|   | 6.1 Overview                                                           |

|   | 6.2 Registers                                                          |

|   | 6.2.1 Power Save Mode Enable                                           |

|   | 6.2.2 Memory Controller Power Save Status                              |

|   | 6.3 LCD Power Sequencing                                               |

|   | 6.4 Enabling Power Save Mode                                           |

|   | 6.5 Disabling Power Save Mode                                          |

| 7 | SwivelView <sup>4</sup>                                                |

|   | 7.1 SwivelView Registers                                               |

|   | 7.2 Examples                                                           |

|   | 7.3 Limitations                                                        |

|   | 7.3.1 SwivelView 0° and 180°                                           |

|   | 7.3.2 SwivelView 90° and 270°                                          |

| 8 | Picture-In-Picture Plus                                                |

|   | 8.1 Registers                                                          |

|   | 8.2 Picture-In-Picture-Plus Examples                                   |

|   | 8.2.1 SwivelView 0° (Landscape Mode)                                   |

|   | 8.2.2 SwivelView 90°                                                   |

|    | 8.2.3       | SwivelView 180°                                                  | 49  |

|----|-------------|------------------------------------------------------------------|-----|

|    | 8.2.4       | SwivelView 270°                                                  | 52  |

|    | 8.3 Limi    | itations                                                         | 55  |

|    | 8.3.1       | SwivelView 0° and 180°                                           | 55  |

|    | 8.3.2       | SwivelView 90° and 270°                                          | 55  |

| 9  | 2D BitBL    | T Engine                                                         | 56  |

|    | 9.1 Regi    | sters                                                            | 56  |

|    | 9.2 BitB    | LT Descriptions                                                  | 64  |

|    | 9.2.1       | Write BitBLT with ROP                                            | 65  |

|    | 9.2.2       | Color Expansion BitBLT                                           | 68  |

|    | 9.2.3       | Color Expansion BitBLT With Transparency                         | 72  |

|    | 9.2.4       | Solid Fill BitBLT                                                | 72  |

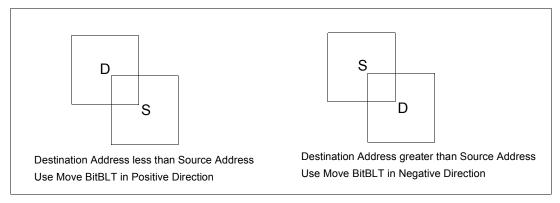

|    | 9.2.5       | Move BitBLT in a Positive Direction with ROP                     | 74  |

|    | 9.2.6       | Move BitBLT in Negative Direction with ROP                       | 76  |

|    | 9.2.7       | Transparent Write BitBLT                                         | 77  |

|    | 9.2.8       | Transparent Move BitBLT in Positive Direction                    | 80  |

|    | 9.2.9       | Pattern Fill BitBLT with ROP                                     | 82  |

|    | 9.2.10      | Pattern Fill BitBLT with Transparency                            | 84  |

|    | 9.2.11      | Move BitBLT with Color Expansion                                 |     |

|    | 9.2.12      | Transparent Move BitBLT with Color Expansion                     | 87  |

|    | 9.2.13      | Read BitBLT                                                      | 87  |

|    | 9.3 S1D     | 13A04 BitBLT Synchronization                                     | 90  |

|    | 9.4 S1E     | D13A04 BitBLT Known Limitations                                  | 91  |

|    | 9.5 Sam     | ple Code                                                         | 91  |

| 10 | Programi    | ming the USB Controller                                          | 92  |

|    | 10.1 Regi   | sters and Interrupts                                             | 92  |

|    | 10.1.1      | Registers                                                        | 92  |

|    | 10.1.2      | Interrupts                                                       | 93  |

|    | 10.2 Initia | alization                                                        | 93  |

|    | 10.2.1      | GPIO Setup                                                       | 93  |

|    | 10.2.2      | USB Registers                                                    | 94  |

|    | 10.3 Data   | Transfers                                                        | 95  |

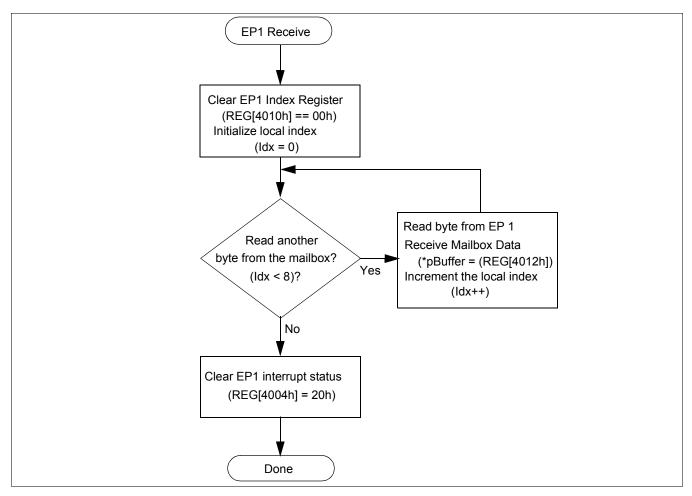

|    | 10.3.1      | Receiving Data from the Host - the OUT command                   | 95  |

|    | 10.3.2      | Sending Data to the Host - the IN command                        | 99  |

|    | 10.4 Kno    | wn Issues                                                        | 104 |

|    | 10.4.1      | EP4 NAK Status not set correctly in USB Status Register          | 104 |

|    | 10.4.2      | Write to EP4 FIFO Valid bit cleared by NAK                       | 105 |

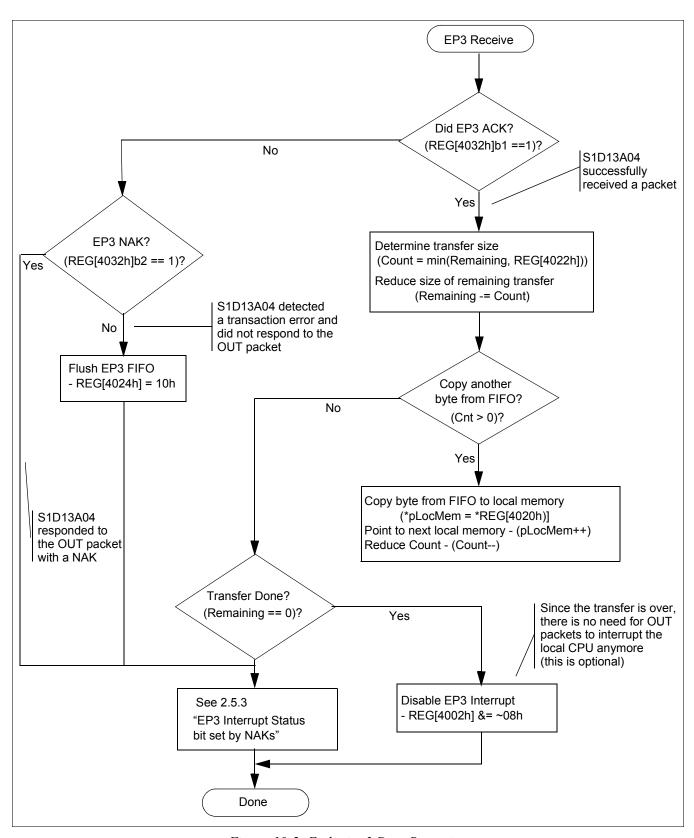

|    | 10.4.3      | EP3 Interrupt Status bit set by NAKs                             | 105 |

|    | 10.4.4      | "EP2 Valid Bit" in USB Status can be erroneously set by firmware | 108 |

|    | 10.4.5     | Setting EP4 FIFO Valid bit while NAKing IN token | 108 |

|----|------------|--------------------------------------------------|-----|

| 11 | Hardware   | Abstraction Layer                                | 110 |

|    | 11.1 Intro | duction                                          | 110 |

|    | 11.2 API   | for the HAL Library                              | 110 |

|    | 11.2.1     | Startup Routines                                 | 111 |

|    | 11.2.2     | Memory Access                                    | 113 |

|    | 11.2.3     | Register Access                                  | 114 |

|    | 11.2.4     | Clock Support                                    | 116 |

|    | 11.2.5     | Miscellaneous                                    | 117 |

| 12 | Sample C   | Code                                             | 119 |

| 13 | Change R   | Record                                           | 120 |

| 14 | Sales and  | d Technical Support                              | 121 |

THIS PAGE LEFT BLANK

## 1 Introduction

This guide discusses programming issues and provides examples for the main features of the S1D13A04, such as SwivelView, Picture-in-Picture Plus, and the BitBLT engine. The example source code referenced in this guide is available on the web at vdc.epson.com.

This guide also introduces the Hardware Abstraction Layer (HAL), which is designed to simplify the programming of the S1D13A04. Most S1D13xxx products have HAL support, thus allowing OEMs to do multiple designs with a common code base.

This document is updated as appropriate. Please check for the latest revision of this document before beginning any development. The latest revision can be downloaded at vdc.epson.com.

We appreciate your comments on our documentation. Please contact us via email at vdc-documentation@ea.epson.com.

## 2 Identifying the S1D13A04

The S1D13A04 can be identified by reading the value contained in the Product Information Register (REG[00h]). To identify the S1D13A04 follow the steps below.

- 1. Read REG[00h].

- 2. The production version of the S1D13A04 returns a value of 2Cxx282Ch (where xx depends on the configuration of the CNF[6:0] pins). This value can be broken down into the following.

- 1. The product code for the S1D13A04 is 0Bh (001011 binary) and can be found in bits 7-2 and also in bits 31-26.

- 2. The revision code is 0h (00 binary) and can be found in bits 1-0 and again in bits 25-24.

- 3. The display buffer size is 28h (00101000 binary) and is contained in bits 15-8.

#### Note

The display buffer size is the distinguishing value between the S1D13A03 and the S1D13A04 as they share the same product code and revision code. For the correct display buffer size for the S1D13A03, see the *S1D13A03 Hardware Functional Specification*, document number X36A-A-001-xx.

## 3 Initialization

This section describes how to initialize the S1D13A04. Sample code for performing initialization of the S1D13A04 is provided in the file **init13A04.c** which is available on the internet at vdc.epson.com.

S1D13A04 initialization can be broken into the following steps.

- 1. Set all registers to initial values. The values are obtained by using the s1d13A04.h file that is exported by the **13A04CFG.EXE** configuration utility. For more information on 13A04CFG, see the *13A04CFG User Manual*, document number X37A-B-001-xx.

- 2. Program the Look-Up Table (LUT) with color values. For details on programming the LUT, see Section 5, "Look-Up Table (LUT)" on page 13.

- 3. Clear the display buffer.

If the system implementation uses a clock chip instead of a fixed oscillator, refer to the HAL (Hardware Abstraction Layer) sample code available on the internet at vdc.epson.com. For example, the Epson S5U13A04B00C evaluation board uses a Cypress clock chip.

## 4 Memory Models

The S1D13A04 contains a display buffer of 160K bytes and supports color depths of 1, 2, 4, 8, and 16 bit-per-pixel. For each color depth, the data format is packed pixel.

Packed pixel data may be envisioned as a stream of pixels. In this stream, pixels are packed adjacent to each other. If a pixel requires four bits, then it is located in the four most significant bits of a byte. The pixel to the immediate right on the display occupies the lower four bits of the same byte. The next two pixels to the immediate right are located in the following byte, etc.

## 4.1 Display Buffer Location

The S1D13A04 display buffer is 160K bytes of embedded SRAM. The display buffer is memory mapped and is accessible directly by software. The memory block location assigned to the S1D13A04 display buffer varies with each individual hardware platform.

For further information on the display buffer, see the S1D13A04 Hardware Functional Specification, document number X37A-A-001-xx.

For further information on the S1D13A04 Evaluation Board, see the S5U13A04B00C Evaluation Board Rev. 1.0 User Manual, document number X37A-G-004-xx.

## 4.2 Memory Organization for One Bit-per-pixel (2 Colors/Gray Shades)

| Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| Pixel 0 | Pixel 1 | Pixel 2 | Pixel 3 | Pixel 4 | Pixel 5 | Pixel 6 | Pixel 7 |

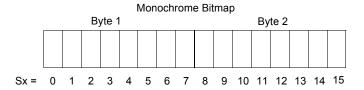

Figure 4-1: Pixel Storage for 1 Bpp in One Byte of Display Buffer

At a color depth of 1 bpp, each byte of display buffer contains eight adjacent pixels. Setting or resetting any pixel requires reading the entire byte, masking out the unchanged bits and setting the appropriate bits to 1.

One bit pixels provide 2 gray shades/color possibilities. For monochrome panels the gray shades are generated by indexing into the first two elements of the green component of the Look-Up Table (LUT). For color panels the 2 colors are derived by indexing into the first 2 positions of the LUT.

## 4.3 Memory Organization for Two Bit-per-pixel (4 Colors/Gray Shades)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0 |  |

|-------|-------|-------|-------|-------|-------|----------|-------|--|

| Pixe  | el 0  | Pixe  | el 1  | Pixe  | el 2  | Pixel 3  |       |  |

| bits  | 1-0   | bits  | 1-0   | bits  | 1-0   | bits 1-0 |       |  |

Figure 4-2: Pixel Storage for 2 Bpp in One Byte of Display Buffer

At a color depth of 2 bpp, each byte of display buffer contains four adjacent pixels. Setting or resetting any pixel requires reading the entire byte, masking out the unchanged bits and setting the appropriate bits to 1.

Two bit pixels provide 4 gray shades/color possibilities. For monochrome panels the gray shades are generated by indexing into the first 4 elements of the green component of the Look-Up Table (LUT). For color panels the 4 colors are derived by indexing into the first 4 positions of the LUT.

## 4.4 Memory Organization for Four Bit-per-pixel (16 Colors/Gray Shades)

| Bit 7 | Bit 7 Bit 6 |               | Bit 5 Bit 4 |  | Bit 3 Bit 2 |               | Bit 0 |

|-------|-------------|---------------|-------------|--|-------------|---------------|-------|

|       |             | el 0<br>: 3-0 |             |  | Pix<br>bits | el 1<br>s 3-0 |       |

Figure 4-3: Pixel Storage for 4 Bpp in One Byte of Display Buffer

At a color depth of 4 bpp, each byte of display buffer contains two adjacent pixels. Setting or resetting any pixel requires reading the entire byte, masking out the upper or lower nibble (4 bits) and setting the appropriate bits to 1.

Four bit pixels provide 16 gray shades/color possibilities. For monochrome panels the gray shades are generated by indexing into the first 16 elements of the green component of the Look-Up Table (LUT). For color panels the 16 colors are derived by indexing into the first 16 positions of the LUT.

## 4.5 Memory Organization for 8 Bpp (256 Colors/64 Gray Shades)

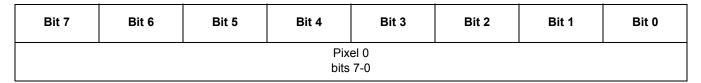

Figure 4-4: Pixel Storage for 8 Bpp in One Byte of Display Buffer

At a color depth of 8 bpp, each byte of display buffer represents one pixel on the display. At this color depth the read-modify-write cycles are eliminated making the update of each pixel faster.

Each byte indexes into one of the 256 positions of the LUT. The S1D13A04 LUT supports six bits per primary color. This translates into 256K possible colors when color mode is selected. Therefore the display has 256 colors available out of a possible 256K colors.

When a monochrome panel is selected, the green component of the LUT is used to determine the intensity. The green indices, with six bits, can resolve 64 gray shades. Display memory values > 64 are truncated. Thus a display memory value of 65 (1000 0001) displays the same intensity as a display memory value of 1.

## 4.6 Memory Organization for 16 Bpp (65536 Colors/64 Gray Shades)

| Bit 15 | Bit 14                     | Bit 13                    | Bit 12                        | Bit 11 | Bit 10 | Bit 9 | Bit 8 |  |  |

|--------|----------------------------|---------------------------|-------------------------------|--------|--------|-------|-------|--|--|

|        | ı                          | Red Component<br>bits 4-0 | Green Component<br>bits 5-3   |        |        |       |       |  |  |

| Bit 7  | Bit 6                      | Bit 5                     | Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 |        |        |       |       |  |  |

| (      | Green Componer<br>bits 2-0 | nt                        | Blue Component<br>bits 4-0    |        |        |       |       |  |  |

Figure 4-5: Pixel Storage for 16 Bpp in Two Bytes of Display Buffer

At a color depth of 16 bpp the S1D13A04 is capable of displaying 64K (65536) colors. The 64K color pixel is divided into three parts: five bits for red, six bits for green, and five bits for blue. In this mode the LUT is bypassed and output goes directly into the Frame Rate Modulator.

Should monochrome mode be chosen at this color depth, the output sends the six bits of the green LUT component to the modulator for a total of 64 possible gray shades.

#### Note

This operation is similar to 8 bpp, but it requires twice as much memory for the display.

## 5 Look-Up Table (LUT)

This section discusses programming the S1D13A04 Look-Up Table (LUT). Included is a summary of the LUT registers, recommendations for color/gray shade LUT values, and additional programming considerations. For a discussion of the LUT architecture, refer to the S1D13A04 Hardware Functional Specification, document number X37A-A-001-xx.

The S1D13A04 is designed with a LUT consisting of 256 indexed red/green/blue entries. Each LUT entry is six bits wide. The color depth (bpp) determines how many indices are used. For example, 1 bpp uses the first 2 indices, 2 bpp uses the first 4 indices, 4 bpp uses the first 16 indices and 8 bpp uses all 256 indices. 16 bpp bypasses the LUT.

In color modes, the pixel values stored in the display buffer index directly to an RGB value stored in the LUT. In monochrome modes, the pixel value indexes into the green component of the LUT and the amount of green at that index controls the intensity.

## 5.1 Registers

## 5.1.1 Look-Up Table Write Register

| Look-                        | Look-Up Table Write Register |    |    |    |    |    |                     |                    |    |       |      |     |    |    |    |

|------------------------------|------------------------------|----|----|----|----|----|---------------------|--------------------|----|-------|------|-----|----|----|----|

| REG[18h] Default = 00000000h |                              |    |    |    |    |    |                     |                    |    | Write | Only |     |    |    |    |

|                              | LUT Write Address            |    |    |    |    |    |                     | LUT Red Write Data |    |       |      | n/  | /a |    |    |

| 31                           | 30                           | 29 | 28 | 27 | 26 | 25 | 24                  | 23                 | 22 | 21    | 20   | 19  | 18 | 17 | 16 |

|                              | LUT Green Write Data n/a     |    |    |    |    | /a | LUT Blue Write Data |                    |    |       |      | n/a |    |    |    |

| 15                           | 14                           | 13 | 12 | 11 | 10 | 9  | 8                   | 7                  | 6  | 5     | 4    | 3   | 2  | 1  | 0  |

This register receives the data to be written to the red (bits 23-18), green (bits 15-10), and blue (bits 7-2) components of the Look-Up Table (LUT). Also contained in this register is the LUT Write Address (bits 31-24) which forms a pointer to the location in the LUT where the RGB components will be written.

This register should be accessed using a 32-bit write cycle to ensure proper operation. If the Look-Up Table Write Register is accessed with 8 or 16-bit write, it is important to understand that the LUT data is latched into the LUT only after the completion of the write to the LUT Write Address bits. On little endian systems, this means a write to bits 31-24. On big endian systems, this means a write to bits 7-2.

This is a write-only register and returns 00h if read.

#### Note

For further information on the S1D13A04 LUT architecture, see the *S1D13A04 Hard-ware Functional Specification*, document number X37A-A-001-xx.

## 5.1.2 Look-Up Table Read Registers

| Look-                                                          | Look-Up Table Read Register |    |    |    |                    |    |    |                   |      |     |    |    |    |    |    |

|----------------------------------------------------------------|-----------------------------|----|----|----|--------------------|----|----|-------------------|------|-----|----|----|----|----|----|

| REG[1Ch] Default = 00000000h Write Only (bits 31-24)/Read Only |                             |    |    |    |                    |    |    |                   | Only |     |    |    |    |    |    |

| LUT Read Address (write only)                                  |                             |    |    |    |                    |    |    | LUT Red Read Data |      |     |    | n  | ′a |    |    |

| 31                                                             | 30                          | 29 | 28 | 27 | 26                 | 25 | 24 | 23                | 22   | 21  | 20 | 19 | 18 | 17 | 16 |

| LUT Green Read Data n/a                                        |                             |    |    |    | LUT Blue Read Data |    |    |                   | n    | n/a |    |    |    |    |    |

| 15                                                             | 14                          | 13 | 12 | 11 | 10                 | 9  | 8  | 7                 | 6    | 5   | 4  | 3  | 2  | 1  | 0  |

This register contains the data returned from the red (bits 23-18), green (bits 15-10), and blue (bits 7-2) components of the Look-Up Table (LUT). Also contained in this register is the LUT Read Address (bits 31-24) which forms a pointer to the location in the LUT where the RGB components are read from.

Reading the LUT is a two step process. First the desired index must be set by writing the LUT Read Address bits with the desired index. Second, the LUT values are retrieved by reading from the Look-Up Table Read Register.

Bits 31-24 are write only and will return 00h if read.

#### **Note**

For further information on the S1D13A04 LUT architecture, see the *S1D13A04 Hardware Functional Specification*, document number X37A-A-001-xx.

## 5.2 Look-Up Table Organization

- The Look-Up Table treats the value of a pixel as an index into an array. For example, a pixel value of zero would point to the first LUT entry, whereas a pixel value of seven would point to the eighth LUT entry.

- The value contained in each LUT entry represents the intensity of the given color or gray shade. This intensity can range in value from 0 to 3Fh.

- The S1D13A04 Look-Up Table is linear. This means increasing the LUT entry number results in a brighter color or gray shade. For example, a LUT entry of FCh in the red bank results in bright red output while a LUT entry of 1Ch results in dull red.

Look-Up Table Indices Used **Effective Gray Color Depth GREEN** Shades/Colors RED **BLUE** 2 gray shades 1 bpp gray 2 4 2 bpp gray 4 gray shades 4 bpp gray 16 16 gray shades 8 bpp gray 64 64 gray shades 64 gray shades 16 bpp gray 1 bpp color 2 2 2 2 colors 2 bpp color 4 4 4 4 colors 4 bpp color 16 16 16 16 colors

*Table 5-1: Look-Up Table Configurations*

Table 5-1: Look-Up Table Configurations

| Color Depth  | Lool | k-Up Table Indices | Effective Gray |               |

|--------------|------|--------------------|----------------|---------------|

| Color Deptil | RED  | GREEN              | BLUE           | Shades/Colors |

| 8 bpp color  | 256  | 256                | 256            | 256 colors    |

| 16 bpp color |      |                    |                | 65536 colors  |

= Indicates the Look-Up Table is not used for that display mode

## 5.2.1 Gray Shade Modes

Gray shade (monochrome) modes are defined by the Color/Mono Panel Select bit (REG[0Ch] bit 6). When this bit is set to 0, the value output to the panel is derived solely from the green component of the LUT.

For each gray shade a table of sample LUT values is provided. These LUT values are a standardized set of intensities used by the Epson S1D13A04 utility programs.

#### **Note**

These LUT values carry eight bits of significance. The S1D13A04 LUT uses only the six MSB. The 2 LSB are ignored.

## 1 bpp gray shade

The 1 bpp gray shade mode uses the green component of the first 2 LUT entries. The remaining indices of the LUT are unused.

Table 5-2: Suggested LUT Values for 1 Bpp Gray Shade

| Red | Green                | Blue                             |

|-----|----------------------|----------------------------------|

| 00  | 00                   | 00                               |

| 00  | FF                   | 00                               |

| 00  | 00                   | 00                               |

| 00  | 00                   | 00                               |

| 00  | 00                   | 00                               |

|     | 00<br>00<br>00<br>00 | 00 00<br>00 FF<br>00 00<br>00 00 |

Unused entries

#### 2 bpp gray shade

The 2 bpp gray shade mode uses the green component of the first 4 LUT entries. The remaining indices of the LUT are unused.

Table 5-3: Suggested LUT Values for 4 Bpp Gray Shade

| Index | Red | Green | Blue |  |  |

|-------|-----|-------|------|--|--|

| 00    | 00  | 00    | 00   |  |  |

| 01    | 00  | 55    | 00   |  |  |

| 02    | 00  | AA    | 00   |  |  |

| 03    | 00  | FF    | 00   |  |  |

| 04    | 00  | 00    | 00   |  |  |

|       | 00  | 00    | 00   |  |  |

| FF    | 00  | 00    | 00   |  |  |

Unused entries

## 4 bpp gray shade

The 4 bpp gray shade mode uses the green component of the first 16 LUT entries. The remaining indices of the LUT are unused.

Table 5-4: Suggested LUT Values for 4 Bpp Gray Shade

| Index | Red            | Green | Blue |  |  |  |  |  |

|-------|----------------|-------|------|--|--|--|--|--|

| 00    | 00             | 00    | 00   |  |  |  |  |  |

| 01    | 00             | 10    | 00   |  |  |  |  |  |

| 02    | 00             | 20    | 00   |  |  |  |  |  |

| 03    | 00             | 34    | 00   |  |  |  |  |  |

| 04    | 00             | 44    | 00   |  |  |  |  |  |

| 05    | 00             | 54    | 00   |  |  |  |  |  |

| 06    | 00             | 68    | 00   |  |  |  |  |  |

| 07    | 00             | 78    | 00   |  |  |  |  |  |

| 08    | 00             | 88    | 00   |  |  |  |  |  |

| 09    | 00             | 9C    | 00   |  |  |  |  |  |

| 0A    | 00             | AC    | 00   |  |  |  |  |  |

| 0B    | 00             | BC    | 00   |  |  |  |  |  |

| 0C    | 00             | CC    | 00   |  |  |  |  |  |

| 0D    | 00             | DC    | 00   |  |  |  |  |  |

| 0E    | 00             | EC    | 00   |  |  |  |  |  |

| 0F    | 00             | FC    | 00   |  |  |  |  |  |

| 10    | 00             | 00    | 00   |  |  |  |  |  |

|       | 00             | 00    | 00   |  |  |  |  |  |

| FF    | 00             | 00    | 00   |  |  |  |  |  |

|       | Unused entries |       |      |  |  |  |  |  |

Seiko Epson Corporation

## 8 bpp gray shade

When configured for 8 bpp gray shade mode, the green component of all 256 LUT entries may be used. However, this results in redundant values where each of the 256 pixel values can only be mapped into 1 of 64 gray shades.

Table 5-5: Suggested LUT Values for 8 Bpp Gray Shade

| Index | Red | Green | Blue | Index | Red | Green | Blue |

|-------|-----|-------|------|-------|-----|-------|------|

| 00    | 00  | 00    | 00   | 20    | 00  | 80    | 00   |

| 01    | 00  | 04    | 00   | 21    | 00  | 84    | 00   |

| 02    | 00  | 08    | 00   | 22    | 00  | 88    | 00   |

| 03    | 00  | 0C    | 00   | 23    | 00  | 8C    | 00   |

| 04    | 00  | 10    | 00   | 24    | 00  | 90    | 00   |

| 05    | 00  | 14    | 00   | 25    | 00  | 94    | 00   |

| 06    | 00  | 18    | 00   | 26    | 00  | 98    | 00   |

| 07    | 00  | 1C    | 00   | 27    | 00  | 9C    | 00   |

| 08    | 00  | 20    | 00   | 28    | 00  | A0    | 00   |

| 09    | 00  | 24    | 00   | 29    | 00  | A4    | 00   |

| 0A    | 00  | 28    | 00   | 2A    | 00  | A8    | 00   |

| 0B    | 00  | 2C    | 00   | 2B    | 00  | AC    | 00   |

| 0C    | 00  | 30    | 00   | 2C    | 00  | B0    | 00   |

| 0D    | 00  | 34    | 00   | 2D    | 00  | B4    | 00   |

| 0E    | 00  | 38    | 00   | 2E    | 00  | B8    | 00   |

| 0F    | 00  | 3C    | 00   | 2F    | 00  | BC    | 00   |

| 10    | 00  | 40    | 00   | 30    | 00  | C0    | 00   |

| 11    | 00  | 44    | 00   | 31    | 00  | C4    | 00   |

| 12    | 00  | 48    | 00   | 32    | 00  | C8    | 00   |

| 13    | 00  | 4C    | 00   | 33    | 00  | CC    | 00   |

| 14    | 00  | 50    | 00   | 34    | 00  | D0    | 00   |

| 15    | 00  | 54    | 00   | 35    | 00  | D4    | 00   |

| 16    | 00  | 58    | 00   | 36    | 00  | D8    | 00   |

| 17    | 00  | 5C    | 00   | 37    | 00  | DC    | 00   |

| 18    | 00  | 60    | 00   | 38    | 00  | E0    | 00   |

| 19    | 00  | 64    | 00   | 39    | 00  | E4    | 00   |

| 1A    | 00  | 68    | 00   | 3A    | 00  | E8    | 00   |

| 1B    | 00  | 6C    | 00   | 3B    | 00  | EC    | 00   |

| 1C    | 00  | 70    | 00   | 3C    | 00  | F0    | 00   |

| 1D    | 00  | 74    | 00   | 3D    | 00  | F4    | 00   |

| 1E    | 00  | 78    | 00   | 3E    | 00  | F8    | 00   |

| 1F    | 00  | 7C    | 00   | 3F    | 00  | FC    | 00   |

|       |     |       |      | 40    | 00  | 00    | 00   |

|       |     |       |      |       | 00  | 00    | 00   |

|       |     |       |      | FF    | 00  | 00    | 00   |

Unused entries

#### 16 bpp gray shade

The Look-Up Table is bypassed at this color depth, therefore programming the LUT is not required.

As with 8 bpp there are limitations to the colors which can be displayed. In this mode the six bits of green are used to set the absolute intensity of the image. This results in 64 gray shades.

#### 5.2.2 Color Modes

In color display modes, the number of LUT entries used is determined by the color depth. For each color depth a table of sample LUT values is provided. These LUT values are a standardized set of colors used by the Epson S1D13A04 utility programs.

#### Note

These LUT values carry eight bits of significance. The S1D13A04 LUT uses only the six MSB. The 2 LSB are ignored.

#### 1 bpp color

When the S1D13A04 is configured for 1 bpp color mode the first 2 entries in the LUT are used. The remaining indices of the LUT are unused.

Table 5-6: Suggested LUT Values for 1 bpp Color

| Index | Red | Green | Blue |

|-------|-----|-------|------|

| 00    | 00  | 00    | 00   |

| 01    | FF  | FF    | FF   |

| 02    | 00  | 00    | 00   |

|       | 00  | 00    | 00   |

| FF    | 00  | 00    | 00   |

= Indicates unused entries in the LUT

#### 2 bpp color

When the S1D13A04 is configured for 2 bpp color mode the first 4 entries in the LUT are used. The remaining indices of the LUT are unused.

Table 5-7: Suggested LUT Values for 2 bpp Color

| Index | Red | Green | Blue |  |  |  |

|-------|-----|-------|------|--|--|--|

| 00    | 00  | 00    | 00   |  |  |  |

| 01    | 00  | 00    | FF   |  |  |  |

| 02    | FF  | 00    | 00   |  |  |  |

| 03    | FF  | FF    | FF   |  |  |  |

| 04    | 00  | 00    | 00   |  |  |  |

Table 5-7: Suggested LUT Values for 2 bpp Color

| Index | Red | Green | Blue |

|-------|-----|-------|------|

|       | 00  | 00    | 00   |

| FF    | 00  | 00    | 00   |

= Indicates unused entries in the LUT

## 4 bpp color

When the S1D13A04 is configured for 4 bpp color mode the first 16 entries in the LUT are used. The remaining indices of the LUT are unused.

The following table shows LUT values that simulate those of a VGA operating in 16 color mode.

Table 5-8: Suggested LUT Values for 4 bpp Color

| Index | Red | Green | Blue |  |  |

|-------|-----|-------|------|--|--|

| 00    | 00  | 00    | 00   |  |  |

| 01    | 00  | 00    | AA   |  |  |

| 02    | 00  | AA    | 00   |  |  |

| 03    | 00  | AA    | AA   |  |  |

| 04    | AA  | 00    | 00   |  |  |

| 05    | AA  | 00    | AA   |  |  |

| 06    | AA  | AA    | 00   |  |  |

| 07    | AA  | AA    | AA   |  |  |

| 08    | 00  | 00    | 00   |  |  |

| 09    | 00  | 00    | FF   |  |  |

| 0A    | 00  | FF    | 00   |  |  |

| 0B    | 00  | FF    | FF   |  |  |

| 0C    | FF  | 00    | 00   |  |  |

| 0D    | FF  | 00    | FF   |  |  |

| 0E    | FF  | FF    | 00   |  |  |

| 0F    | FF  | FF    | FF   |  |  |

| 10    | 00  | 00    | 00   |  |  |

|       | 00  | 00    | 00   |  |  |

| FF    | 00  | 00    | 00   |  |  |

= Indicates unused entries in the LUT

## 8 bpp color

When the S1D13A04 is configured for 8 bpp color mode all 256 entries in the LUT are used.

The S1D13A04 LUT has six bits (64 intensities) of intensity control per primary color which is the same as a standard VGA RAMDAC.

The following table shows LUT values that simulate the VGA default color palette.

Table 5-9: Suggested LUT Values 8 bpp Color

| Index | R  | G  | В  |

|-------|----|----|----|-------|----|----|----|-------|----|----|----|-------|----|----|----|

| 00    | 00 | 00 | 00 | 40    | 00 | 00 | 00 | 80    | FF | FF | 00 | C0    | 00 | 00 | 00 |

| 01    | 00 | 00 | AA | 41    | 00 | 00 | 11 | 81    | FF | EF | 00 | C1    | 00 | 11 | 11 |

| 02    | 00 | AA | 00 | 42    | 00 | 00 | 22 | 82    | FF | DE | 00 | C2    | 00 | 22 | 22 |

| 03    | 00 | AA | AA | 43    | 00 | 00 | 33 | 83    | FF | CD | 00 | C3    | 00 | 33 | 33 |

| 04    | AA | 00 | 00 | 44    | 00 | 00 | 44 | 84    | FF | ВС | 00 | C4    | 00 | 44 | 44 |

| 05    | AA | 00 | AA | 45    | 00 | 00 | 55 | 85    | FF | AB | 00 | C5    | 00 | 55 | 55 |

| 06    | AA | AA | 00 | 46    | 00 | 00 | 66 | 86    | FF | 9A | 00 | C6    | 00 | 66 | 66 |

| 07    | AA | AA | AA | 47    | 00 | 00 | 77 | 87    | FF | 89 | 00 | C7    | 00 | 77 | 77 |

| 08    | 55 | 55 | 55 | 48    | 00 | 00 | 89 | 88    | FF | 77 | 00 | C8    | 00 | 89 | 89 |

| 09    | 00 | 00 | FF | 49    | 00 | 00 | 9A | 89    | FF | 66 | 00 | C9    | 00 | 9A | 9A |

| 0A    | 00 | FF | 00 | 4A    | 00 | 00 | AB | 8A    | FF | 55 | 00 | CA    | 00 | AB | AB |

| 0B    | 00 | FF | FF | 4B    | 00 | 00 | BC | 8B    | FF | 44 | 00 | СВ    | 00 | BC | ВС |

| 0C    | FF | 00 | 00 | 4C    | 00 | 00 | CD | 8C    | FF | 33 | 00 | CC    | 00 | CD | CD |

| 0D    | FF | 00 | FF | 4D    | 00 | 00 | DE | 8D    | FF | 22 | 00 | CD    | 00 | DE | DE |

| 0E    | FF | FF | 00 | 4E    | 00 | 00 | EF | 8E    | FF | 11 | 00 | CE    | 00 | EF | EF |

| 0F    | FF | FF | FF | 4F    | 00 | 00 | FF | 8F    | FF | 00 | 00 | CF    | 00 | FF | FF |

| 10    | 00 | 00 | 00 | 50    | 00 | 00 | FF | 90    | FF | 00 | 00 | D0    | FF | 00 | 00 |

| 11    | 11 | 11 | 11 | 51    | 00 | 11 | FF | 91    | FF | 00 | 11 | D1    | FF | 11 | 11 |

| 12    | 22 | 22 | 22 | 52    | 00 | 22 | FF | 92    | FF | 00 | 22 | D2    | FF | 22 | 22 |

| 13    | 33 | 33 | 33 | 53    | 00 | 33 | FF | 93    | FF | 00 | 33 | D3    | FF | 33 | 33 |

| 14    | 44 | 44 | 44 | 54    | 00 | 44 | FF | 94    | FF | 00 | 44 | D4    | FF | 44 | 44 |

| 15    | 55 | 55 | 55 | 55    | 00 | 55 | FF | 95    | FF | 00 | 55 | D5    | FF | 55 | 55 |

| 16    | 66 | 66 | 66 | 56    | 00 | 66 | FF | 96    | FF | 00 | 66 | D6    | FF | 66 | 66 |

| 17    | 77 | 77 | 77 | 57    | 00 | 77 | FF | 97    | FF | 00 | 77 | D7    | FF | 77 | 77 |

| 18    | 89 | 89 | 89 | 58    | 00 | 89 | FF | 98    | FF | 00 | 89 | D8    | FF | 89 | 89 |

| 19    | 9A | 9A | 9A | 59    | 00 | 9A | FF | 99    | FF | 00 | 9A | D9    | FF | 9A | 9A |

| 1A    | AB | AB | AB | 5A    | 00 | AB | FF | 9A    | FF | 00 | AB | DA    | FF | AB | AB |

| 1B    | ВС | ВС | ВС | 5B    | 00 | ВС | FF | 9B    | FF | 00 | ВС | DB    | FF | ВС | ВС |

| 1C    | CD | CD | CD | 5C    | 00 | CD | FF | 9C    | FF | 00 | CD | DC    | FF | CD | CD |

| 1D    | DE | DE | DE | 5D    | 00 | DE | FF | 9D    | FF | 00 | DE | DD    | FF | DE | DE |

| 1E    | EF | EF | EF | 5E    | 00 | EF | FF | 9E    | FF | 00 | EF | DE    | FF | EF | EF |

| 1F    | FF | FF | FF | 5F    | 00 | FF | FF | 9F    | FF | 00 | FF | DF    | FF | FF | FF |

| 20    | 00 | 00 | 00 | 60    | 00 | FF | FF | A0    | FF | 00 | FF | E0    | 00 | FF | 00 |

| 21    | 11 | 00 | 00 | 61    | 00 | FF | EF | A1    | EF | 00 | FF | E1    | 11 | FF | 11 |

| 22    | 22 | 00 | 00 | 62    | 00 | FF | DE | A2    | DE | 00 | FF | E2    | 22 | FF | 22 |

| 23    | 33 | 00 | 00 | 63    | 00 | FF | CD | A3    | CD | 00 | FF | E3    | 33 | FF | 33 |

Index Index Index R G В R G В R G В Index R G В 24 44 00 00 64 00 FF ВС A4 ВС 00 FF E4 44 FF 44 55 00 00 FF AB 00 FF 55 FF 55 25 65 00 AB A5 E5 26 66 00 00 66 00 FF 9A A6 9A 00 FF E6 66 FF 66 00 00 89 27 77 67 00 FF 89 Α7 00 FF E7 77 FF 77 28 89 00 00 68 00 FF 77 A8 77 00 FF E8 89 FF 89 29 9A 00 00 69 00 FF 66 Α9 66 00 FF E9 9A FF 9A 2A ΑB 00 00 6A 00 FF AA 55 00 FF EΑ AΒ FF AB 55 2B BC 00 00 6B 00 FF 44 AB 44 00 FF ΕB BC FF BC CD 00 00 00 FF 33 33 00 EC CD FF CD 2C 6C AC FF 2D DE 00 00 6D 00 FF 22 AD 22 00 FF ED DE FF DE EF 00 00 FF 00 FF FF 2E 6E 00 11 ΑE 11 EE EF EF 2F FF 00 00 6F 00 FF 00 AF 00 00 FF EF FF FF FF 00 30 00 00 00 70 00 FF 00 B0 00 F0 00 00 FF 00 31 00 11 00 71 11 FF 00 B1 11 00 11 F1 11 11 FF 32 00 22 00 72 22 FF 00 B2 22 00 22 F2 22 22 FF FF 33 00 33 00 73 33 FF 00 B3 33 00 33 F3 33 33 34 00 44 00 74 44 FF 00 B4 44 00 44 F4 44 44 FF 00 55 00 00 00 FF 35 75 55 FF B5 55 55 F5 55 55 36 00 66 00 76 00 00 F6 66 FF 66 FF B6 66 66 66 00 00 77 FF 00 00 F7 77 FF 37 77 77 B7 77 77 77 38 89 00 78 FF 89 F8 FF 00 89 00 B8 00 89 89 89 9A 00 B9 F9 FF 39 00 79 9A FF 00 9A 00 9A 9A 9A 00 00 FF 3A AB 7A AB FF 00 BA AB 00 AB FΑ AB AB ВС 00 00 7B 00 BC 00 ВС FF 3B BC FF BB BC FΒ BC 3C 00 CD 00 7C CD FF 00 BC CD 00 CD FC CD CD FF 3D 00 DE 00 00 DE FD DE DE FF 7D DE FF BD 00 DE 3E 00 EF 00 7E EF FF 00 BE EF 00 EF FE EF EF FF 3F 00 FF 00 7F FF FF 00 BF FF 00 FF FF FF FF FF

Table 5-9: Suggested LUT Values 8 bpp Color (Continued)

#### 16 bpp color

The Look-Up Table is bypassed at this color depth, therefore programming the LUT is not required.

## 6 Power Save Mode

The S1D13A04 is designed for very low-power applications. During normal operation, the internal clocks are dynamically disabled when not required. The S1D13A04 design also includes a Power Save Mode to further save power. When Power Save Mode is initiated, LCD power sequencing is required to ensure the LCD bias power supply is disabled properly. For further information on LCD power sequencing, see Section 6.3, "LCD Power Sequencing" on page 26.

For Power Save Mode AC Timing, see the *S1D13A04 Hardware Functional Specification*, document number X37A-A-001-xx.

#### 6.1 Overview

The S1D13A04 includes a software initiated Power Save Mode. Enabling/disabling Power Save Mode is controlled using the Power Save Mode Enable bit (REG[14h] bit 4).

While Power Save Mode is enabled the following conditions apply.

- Registers are accessible (USB registers are not accessible)

- Memory writes are possible<sup>1</sup>

- Memory reads are not possible

- LCD display is inactive.

- LCD interface outputs are forced low.

#### Note

<sup>1</sup> Memory writes are possible during power save mode because the S1D13A04 dynamically enables the memory controller for display buffer writes.

## 6.2 Registers

#### 6.2.1 Power Save Mode Enable

|     | Power Save Configuration Register REG[14h] Default = 00000010h |    |    |   |    |    |    |                        |                                           |     |                                 | Read/ | Write |    |                                      |    |    |

|-----|----------------------------------------------------------------|----|----|---|----|----|----|------------------------|-------------------------------------------|-----|---------------------------------|-------|-------|----|--------------------------------------|----|----|

|     | n/a                                                            |    |    |   |    |    |    |                        |                                           |     |                                 |       |       |    |                                      |    |    |

| 31  |                                                                | 30 | 29 | ) | 28 | 27 | 26 | 25                     | 24                                        | 23  | 22                              | 21    | 20    | 19 | 18                                   | 17 | 16 |

| n/a |                                                                |    |    |   |    |    |    | VNDP<br>Status<br>(RO) | Memory<br>Power<br>Save<br>Status<br>(RO) | n/a | Power<br>Save<br>Mode<br>Enable |       | n/a   |    | 'Direct'<br>HR-TFT<br>GPO<br>Control |    |    |

| 15  |                                                                | 14 | 13 | 3 | 12 | 11 | 10 | 9                      | 8                                         | 7   | 6                               | 5     | 4     | 3  | 2                                    | 1  | 0  |

The Power Save Mode Enable bit initiates Power Save Mode when set to 1. Setting the bit to 0 disables Power Save Mode and returns the S1D13A04 to normal mode. At reset this bit is set to 1.

#### Note

Enabling/disabling Power Save Mode requires proper LCD Power Sequencing. See Section 6.3, "LCD Power Sequencing" on page 26.

## **6.2.2 Memory Controller Power Save Status**

| Power Save Configuration Register REG[14h] Default = 00000010h |  |    |  |    |  |    |     |   |    |  | Read/ | Write |                        |                                           |     |                                 |    |     |    |                                      |

|----------------------------------------------------------------|--|----|--|----|--|----|-----|---|----|--|-------|-------|------------------------|-------------------------------------------|-----|---------------------------------|----|-----|----|--------------------------------------|

|                                                                |  |    |  |    |  |    |     |   |    |  |       | n     | /a                     |                                           |     |                                 |    |     |    |                                      |

| 31                                                             |  | 30 |  | 29 |  | 28 | 2   | 7 | 26 |  | 25    | 24    | 23                     | 22                                        | 21  | 20                              | 19 | 18  | 17 | 16                                   |

|                                                                |  |    |  |    |  | r  | ı/a |   |    |  |       |       | VNDP<br>Status<br>(RO) | Memory<br>Power<br>Save<br>Status<br>(RO) | n/a | Power<br>Save<br>Mode<br>Enable |    | n/a |    | 'Direct'<br>HR-TFT<br>GPO<br>Control |

| 15                                                             |  | 14 |  | 13 |  | 12 | 1   | 1 | 10 |  | 9     | 8     | 7                      | 6                                         | 5   | 4                               | 3  | 2   | 1  | 0                                    |

The Memory Controller Power Save Status bit is a read-only status bit which indicates the power save state of the S1D13A04 SRAM interface. When this bit returns a 1, the SRAM interface is powered down and the memory clock source may be disabled. When this bit returns a 0, the SRAM interface is active. This bit returns a 0 after a chip reset.

#### Note

Memory writes are possible during power save mode because the S1D13A04 dynamically enables the memory controller for display buffer writes.

## 6.3 LCD Power Sequencing

The S1D13A04 requires LCD power sequencing (the process of powering-on and powering-off the LCD panel). LCD power sequencing allows the LCD bias voltage to discharge prior to shutting down the LCD signals, preventing long term damage to the panel and avoiding unsightly "lines" at power-on/power-off.

Proper LCD power sequencing for power-off requires a delay from the time the LCD power is disabled to the time the LCD signals are shut down. Power-on requires the LCD signals to be active prior to applying power to the LCD. This time interval depends on the LCD bias power supply design. For example, the LCD bias power supply on the S5U13A04B00C Evaluation Board requires 0.5 seconds to fully discharge. Other power supply designs may vary.

This section assumes the LCD bias power is controlled through GPIO0. The S1D13A04 GPIO pins are multi-use pins and may not be available in all system designs. For further information on the availability of GPIO pins, see the *S1D13A04 Hardware Functional Specification*, document number X37A-A-001-xx.

#### Note

This section discusses LCD power sequencing for passive and TFT (non-HR-TFT) panels only. For further information on LCD power sequencing the HR-TFT, see *Connecting to the Sharp HR-TFT Panels*, document number X37A-G-011-xx.

## 6.4 Enabling Power Save Mode

Power Save Mode must be enabled using the following steps.

1. Turn off the LCD bias power.

#### Note

The S5U13A04B00C uses GPIO0 to control the LCD bias power supplies. Your system design may vary.

- 2. Wait for the LCD bias power supply to discharge. The discharge time is based on the discharge rate of the power supply.

- 3. Enable Power Save Mode set REG[14h] bit 4 to 1.

The S1D13A04 is now in Power Save Mode. To further increase power savings PCLK and MCLK can be switched off (see steps 4 and 5).

- 4. At this time, the LCD pixel clock source may be disabled.

- 5. After the Memory Controller Power Save Status bit (REG[14h] bit 6) returns a 1, the Memory Clock source may be shut down.

## 6.5 Disabling Power Save Mode

Bring the S1D13A04 out of Power Save Mode using the following steps.

- 1. If the Memory Clock source is shut down, it must be started.

- 2. If the pixel clock is disabled, it must be started.

- 3. Disable Power Save Mode set REG[14h] bit 4 to 0.

- 4. Wait for the LCD bias power supply to charge. The charge is based on the time required for the LCD power supply to reach operating voltage.

- 5. Enable the LCD bias power.

#### Note

The S5U13A04B00C uses GPIO0 to control the LCD bias power supplies. Your system design may vary.

## 7 SwivelView<sup>TM</sup>

Most computer displays operate in landscape mode. In landscape mode the display is typically wider than it is high. For example, a display size of 320x240 is 320 pixels wide and 240 lines high.

SwivelView rotates the display image counter-clockwise in ninety degree increments. Rotating the image on a 320x240 display by 90 or 270 degrees yields a display that is now 240 pixels wide and 320 lines high.

The S1D13A04 provides hardware support for SwivelView in all color depths (1, 2, 4, 8 and 16 bpp).

For further details on the SwivelView feature, see the S1D13A04 Hardware Functional Specification, document number X37A-A-001-xx.

## 7.1 SwivelView Registers

These are the registers which control the SwivelView feature.

|                           | Display Settings Register               |  |    |  |    |  |    |  |    |    |                  |                            |      |                       |                                      |     |                 |    |    |

|---------------------------|-----------------------------------------|--|----|--|----|--|----|--|----|----|------------------|----------------------------|------|-----------------------|--------------------------------------|-----|-----------------|----|----|

| REG[                      | REG[10h] Default = 00000000h Read/Write |  |    |  |    |  |    |  |    |    |                  |                            | rite |                       |                                      |     |                 |    |    |

|                           |                                         |  |    |  |    |  |    |  |    |    | Display<br>Blank | Dithering<br>Disable       | n/a  | SW<br>Video<br>Invert | PIP <sup>+</sup><br>Window<br>Enable | n/a | SwivelVi<br>Sel |    |    |

| 31                        | 30                                      |  | 29 |  | 28 |  | 27 |  | 26 | 25 | 24               | 23                         | 22   | 21                    | 20                                   | 19  | 18              | 17 | 16 |

| n/a Bits-<br>(actual valu |                                         |  |    |  |    |  |    |  |    |    |                  | per-pixel S<br>e: 1, 2, 4, |      | o)                    |                                      |     |                 |    |    |

| 15                        | 14                                      |  | 13 |  | 12 |  | 11 |  | 10 | 9  | 8                | 7                          | 6    | 5                     | 4                                    | 3   | 2               | 1  | 0  |

SwivelView Mode Select

The SwivelView modes are selected using the SwivelView Mode Select Bits[1:0] (bits 17-16). The combinations of these bits provide the following rotations.

Table 7-1: SwivelView Mode Select Bits

| SwivelView Mode<br>Select Bit 1 | SwivelView Mode<br>Select Bit 0 | SwivelView<br>Orientation |

|---------------------------------|---------------------------------|---------------------------|

| 0                               | 0                               | 0° (normal)               |

| 0                               | 1                               | 90°                       |

| 1                               | 0                               | 180°                      |

| 1                               | 1                               | 270°                      |

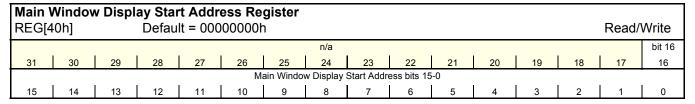

#### Main Window Display Start Address

The Main Window Display Start Address register represents a DWORD address which points to the start of the main window image in the display buffer. An address of 0 is the start of the display buffer. For the following SwivelView mode descriptions, the *desired byte address* is the starting display address for the main window image.

```

In SwivelView 0°, program the start address

= desired byte address ÷ 4

```

In SwivelView 90°, program the start address =  $((\text{desired byte address} + (\text{panel height} \times \text{bpp} \div 8) + ((4 - (\text{panel height} \times \text{bpp} \div 8)) & 03h)) \div 4) - 1$

In SwivelView 180°, program the start address =  $((\text{desired byte address} + (\text{Main Window Stride} \times (\text{panel height } - 1)) + (\text{panel width} \times \text{bpp} \div 8) + ((4 - (\text{panel width} \times \text{bpp} \div 8)) & 03h)) \div 4) - 1$

In SwivelView 270°, program the start address = (desired byte address + ((panel width - 1) × Main Window Stride)) ÷ 4

#### Note

Truncate all fractional values before writing to the address registers.

#### Note

SwivelView  $0^{\circ}$  and  $180^{\circ}$  require the panel width to be a multiple of  $32 \div$  bits-per-pixel. SwivelView  $90^{\circ}$  and  $270^{\circ}$  require the panel height to be a multiple of  $32 \div$  bits-per-pixel. If this is not possible, refer to Section 7.3, "Limitations".

| Main Window Line Address Offset RegisterREG[44h]Default = 00000000hRead/Write |                                              |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|-------------------------------------------------------------------------------|----------------------------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|                                                                               | n/a                                          |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 31                                                                            | 30                                           | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|                                                                               | n/a Main Window Line Address Offset bits 9-0 |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 15                                                                            | 14                                           | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

Main Window Line Address Offset

The Main Window Line Address Offset register indicates the number of dwords per line in the main window image.

For SwivelView 0° and 180°, the image width must be at least the panel width. For SwivelView 90° and 270°, the image width must be at least the panel height. In addition, the image width must be a multiple of 32 ÷ bpp. If the image width is not such a multiple, a slightly larger width must be chosen (see Section 7.3, "Limitations").

*Panel width* and *panel height* refer to the physical panel dimensions in pixels. *Stride* is the number of bytes required for one line of the image; the offset register represents the stride in DWORD steps.

Main Window Stride = image width  $\times$  bpp  $\div$  8

#### Note

Image width can be larger than panel width (or panel height, for SwivelView 90° or 270°).

number of dwords per line = image width  $\div$  (32  $\div$  bpp)

## 7.2 Examples

# Example 1: In SwivelView 0° (normal) mode, program the main window registers for a 320x240 panel at a color depth of 4 bpp.

Determine the main window display start address.

The main window is typically placed at the start of display memory which is at display address 0.

main window display start address register = desired byte address ÷ 4 = 0

Program the Main Window Display Start Address register. REG[40h] is set to 00000000h.

2. Determine the main window line address offset.

```

number of dwords per line

= image width \div (32 \div bpp)

= 320 \div (32 \div 4)

= 40

= 28h

```

Program the Main Window Line Address Offset register. REG[44h] is set to 00000028h.

# Example 2: In SwivelView 90° mode, program the main window registers for a 320x240 panel at a color depth of 4 bpp.

1. Determine the main window display start address.

The main window is typically placed at the start of display memory, which is at display address 0.

```

main window display start address register

= ((\text{desired byte address} + (\text{panel height} \times \text{bpp} \div 8) + ((4 - (\text{panel height} \times \text{bpp} \div 8)) & 03h)) \div 4) - 1

= ((0 + (240 \times 4 \div 8) + ((4 - (240 \times 4 \div 8)) & 03h)) \div 4) - 1

= 29

= 1 \text{Dh}

```

Program the Main Window Display Start Address register. REG[40h] is set to 0000001Dh

2. Determine the main window line address offset.

```

number of dwords per line

= image width \div (32 \div bpp)

= 240 \div (32 \div 4)

= 30

= 1Eh

```

Program the Main Window Line Address Offset register. REG[44h] is set to 0000001Eh.

# Example 3: In SwivelView 180° mode, program the main window registers for a 320x240 panel at a color depth of 4 bpp.

1. Determine the main window display start address.

The main window is typically placed at the start of display memory which is at display address 0.

Main Window Stride

```

= image width × bpp ÷ 8

= 320 × 4 ÷ 8

= 160

= A0h

```

main window display start address register

```

= ((desired byte address + (Main Window Stride × (panel height -1)) + (panel width × bpp \div 8) + ((4 - (panel width × bpp \div 8)) & 03h)) \div 4) - 1 = ((0+(160 × (240 - 1)) + (320 × 4 \div 8) + ((4 - (320 × 4 \div 8))& 03h)) \div 4) - 1 = 9599 = 257Fh

```

Program the Main Window Display Start Address register. REG[40h] is set to 0000257Fh.

2. Determine the main window line address offset.

```

number of dwords per line

= image width \div (32 \div bpp)

= 320 \div (32 \div 4)

= 40

= 28h

```

Program the Main Window Line Address Offset register. REG[44h] is set to 00000028h.

# Example 4: In SwivelView 270° mode, program the main window registers for a 320x240 panel at a color depth of 4 bpp.

1. Determine the main window display start address.

The main window is typically placed at the start of display memory, which is at display address 0.

Main Window Stride

```

= image width \times bpp \div 8

= 240 \times 4 \div 8

= 120

= 78h

```

main window display start address register

```

= (desired byte address + ((panel width - 1) × Main Window Stride)) \div 4

= (0 + ((320 - 1) \times 120)) \div 4

= 9570

= 2562h

```

Program the Main Window Display Start Address register. REG[40h] is set to 00002562h.

2. Determine the main window line address offset.

```

number of dwords per line

= image width \div (32 \div bpp)

= 240 \div (32 \div 4)

= 30

= 1Eh

```

Program the Main Window Line Address Offset register. REG[44h] is set to 0000001Eh.

## 7.3 Limitations

## 7.3.1 SwivelView 0° and 180°

In SwivelView 0° and 180°, the Main Window Line Address Offset register (REG[44h]) requires the *panel width* to be a multiple of 32 ÷ bits-per-pixel. If this is not the case, then the Main Window Line Address Offset register must be programmed to a longer line which meets this requirement. This longer line creates a virtual image where the width is *main window line address offset register* × 32 ÷ bits-per-pixel. In SwivelView 0°, this virtual image should be drawn in display memory as left justified, and in SwivelView 180°, this virtual image should be drawn in display memory as right justified. A left-justified image is one drawn in display memory such that each of the image's lines only use the left most portion of the line width defined by the line address offset register (i.e. starting at horizontal position 0). A right-justified image is one drawn in display memory such that each of the image's lines only use the right most portion of the line width defined by the line address offset register (i.e. starting at a non-zero horizontal position which is the virtual width - image width).

## 7.3.2 SwivelView 90° and 270°

In SwivelView 90° and 270°, the Main Window Line Address Offset register (REG[44h]) requires the *panel height* to be a multiple of 32 ÷ bits-per-pixel. If this is not the case, then the Main Window Line Address Offset register must be programmed to a longer line which meets this requirement. This longer line creates a virtual image whose width is *main window line address offset register* × 32 ÷ bits-per-pixel. In SwivelView 270°, this virtual image should be drawn in display memory as left justified, and in SwivelView 90°, this virtual image should be drawn in display memory as right justified. A left-justified image is one drawn in display memory such that each of the image's lines only use the left most portion of the line width defined by the line address offset register (i.e. starting at horizontal position 0). A right-justified image is one drawn in display memory such that each of the image's lines only use the right most portion of the line width defined by the line address offset register (i.e. starting at a non-zero horizontal position which is the virtual width - image width).

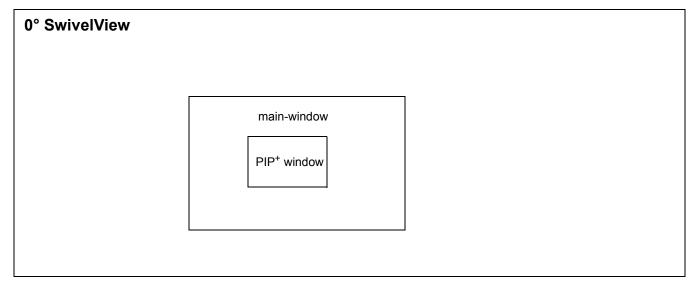

## 8 Picture-In-Picture Plus

Picture-in-Picture Plus (PIP<sup>+</sup>) enables a secondary window (or PIP<sup>+</sup> window) within the main display window. The PIP<sup>+</sup> window may be positioned anywhere within the virtual display and is controlled through the PIP<sup>+</sup> Window control registers (REG[50h] through REG[5Ch]). The PIP<sup>+</sup> window retains the same color depth and SwivelView orientation as the main window.

A PIP<sup>+</sup> window can be used to display temporary items such as a dialog box or to "float" the display item so that the system doesn't have to exclude the area during screen repaints.

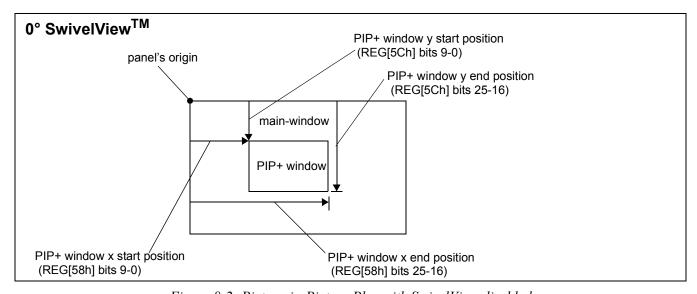

The following diagram shows an example of a PIP<sup>+</sup> window within a main window.

Figure 8-1: Picture-in-Picture Plus with SwivelView disabled

## 8.1 Registers

The following registers control the Picture-In-Picture Plus feature.

| Display Settings Register REG[10h] Default = 00000000h Read/Write |     |    |    |    |    |    |                             |                  |                      |                                                            |                       |                                      |     |                  |                |

|-------------------------------------------------------------------|-----|----|----|----|----|----|-----------------------------|------------------|----------------------|------------------------------------------------------------|-----------------------|--------------------------------------|-----|------------------|----------------|

|                                                                   | n/a |    |    |    |    |    | Pixel<br>Doubling<br>Horiz. | Display<br>Blank | Dithering<br>Disable | n/a                                                        | SW<br>Video<br>Invert | PIP <sup>+</sup><br>Window<br>Enable | n/a | SwivelVio<br>Sel | ew Mode<br>ect |

| 31                                                                | 30  | 29 | 28 | 27 | 26 | 25 | 24                          | 23               | 22                   | 21                                                         | 20                    | 19                                   | 18  | 17               | 16             |

| n/a                                                               |     |    |    |    |    |    |                             |                  |                      | Bits-per-pixel Select (actual value: 1, 2, 4, 8 or 16 bpp) |                       |                                      |     |                  |                |

| 15                                                                | 14  | 13 | 12 | 11 | 10 | 9  | 8                           | 7                | 6                    | 5                                                          | 4                     | 3                                    | 2   | 1                | 0              |

PIP<sup>+</sup> Window Enable

The PIP<sup>+</sup> Window Enable bit enables a PIP<sup>+</sup> window within the main window. The location of the PIP<sup>+</sup> window within the landscape window is determined by the PIP<sup>+</sup> X Position register (REG[58h]) and PIP<sup>+</sup> Y Position register (REG[5Ch]). The PIP<sup>+</sup> window has its own Display Start Address register (REG[50h]) and Line Address Offset register (REG[54h]). The PIP<sup>+</sup> window shares the same color depth and SwivelView<sup>TM</sup> orientation as the main window.

| PIP <sup>+</sup> Display Start Address Register REG[50h] Default = 00000000h Read/Write |                                                  |    |    |    |    |    |     |    |    |    |    |    |    |    |        |

|-----------------------------------------------------------------------------------------|--------------------------------------------------|----|----|----|----|----|-----|----|----|----|----|----|----|----|--------|

|                                                                                         |                                                  |    |    |    |    |    | n/a |    |    |    |    |    |    |    | bit 16 |

| 31                                                                                      | 30                                               | 29 | 28 | 27 | 26 | 25 | 24  | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16     |

|                                                                                         | PIP <sup>+</sup> Display Start Address bits 15-0 |    |    |    |    |    |     |    |    |    |    |    |    |    |        |

| 15                                                                                      | 14                                               | 13 | 12 | 11 | 10 | 9  | 8   | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0      |

PIP<sup>+</sup> Display Start Address

The PIP<sup>+</sup> Display Start Address register is a DWORD which represents an address that points to the start of the PIP<sup>+</sup> window image in the display buffer. An address of 0 is the start of the display buffer. For the following PIP<sup>+</sup> descriptions, the desired byte address is the starting display address for the PIP<sup>+</sup> window image.

```

In SwivelView 0°, program the start address

= desired byte address \div 4

In SwivelView 90°, program the start address

= ((desired byte address + (PIP<sup>+</sup> width \times bpp \div 8)

+((4 - (PIP^+ width \times bpp \div 8)) \& (03h)) \div 4) - 1

In SwivelView 180°, program the start address

= ((\text{desired byte address} + (\text{PIP}^+ \text{Stride} \times (\text{PIP}^+ \text{height} - 1)))

+ (PIP^{+} width \times bpp \div 8) + ((4 - (PIP^{+} width \times bpp \div 8)) \& 03h)) \div 4) - 1

In SwivelView 270°, program the start address

= (desired byte address + ((PIP<sup>+</sup> height - 1) × PIP<sup>+</sup> Stride)) \div 4

```

#### Note

Truncate all fractional values before writing to the address registers.

#### Note

SwivelView  $0^{\circ}$  and  $180^{\circ}$  require the PIP<sup>+</sup> width to be a multiple of  $32 \div$  bits-per-pixel. SwivelView  $90^{\circ}$  and  $270^{\circ}$  require the PIP<sup>+</sup> height to be a multiple of  $32 \div$  bits-per-pixel. If this is not possible, refer to Section 8.3, "Limitations".

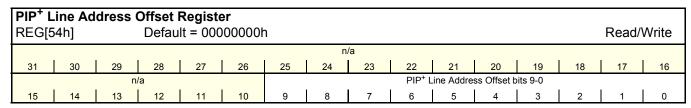

PIP<sup>+</sup> Line Address Offset

The PIP<sup>+</sup> Line Address Offset register indicates the number of dwords per line in the PIP<sup>+</sup> window image.

The image width must be a multiple of 32 ÷ bpp. If the image width is not such a multiple, a slightly larger width must be chosen (see Section 8.3, "Limitations").

*PIP*<sup>+</sup> width and *PIP*<sup>+</sup> height refer to the PIP<sup>+</sup> dimensions as seen in SwivelView 0° (landscape mode). Stride is the number of bytes required for one line of the image; the offset register represents the stride in DWORD steps.

$PIP^{+}$  Stride = image width × bpp ÷ 8

For SwivelView 0° and 180°,

$PIP^{+}$  Width=((REG[58h] bits 25:16) - (REG[58h] bits 9:0) + 1) × (32 ÷ bpp)

PIP<sup>+</sup> Height=(REG[5Ch] bits 25:16) - (REG[5Ch] bits 9:0) + 1

For SwivelView 90° and 270°,

$PIP^{+}$  Width=((REG[5Ch] bits 25:16) - (REG[5Ch] bits 9:0) + 1) × (32 ÷ bpp)

$PIP^{+}$  Height=(REG[58h] bits 25:16) - (REG[58h] bits 9:0) + 1

#### Note

Image width can be larger than PIP<sup>+</sup> width (or PIP<sup>+</sup> height, for SwivelView 90° or 270°).

number of dwords per line = image width  $\div$  (32  $\div$  bpp)

| PIP <sup>+</sup> X P | PIP <sup>+</sup> X Positions Register |    |    |    |    |    |    |    |  |                  |                      |              |     |    |       |       |

|----------------------|---------------------------------------|----|----|----|----|----|----|----|--|------------------|----------------------|--------------|-----|----|-------|-------|

| REG[58h              | REG[58h] Default = 0000000            |    |    |    |    |    |    |    |  |                  |                      |              |     |    | Read/ | Write |

|                      | n/a                                   |    |    |    |    |    |    |    |  | PIP              | <sup>+</sup> X End P | osition bits | 9-0 |    |       |       |

| 31                   | 30                                    | 29 | 28 | 27 | 26 | 25 | 24 | 23 |  | 22               | 21                   | 20           | 19  | 18 | 17    | 16    |

|                      | n/a                                   |    |    |    |    |    |    |    |  | PIP <sup>+</sup> | X Start P            | osition bits | 9-0 |    |       |       |

| 15                   | 14                                    | 13 | 12 | 11 | 10 | 9  | 8  | 7  |  | 6                | 5                    | 4            | 3   | 2  | 1     | 0     |

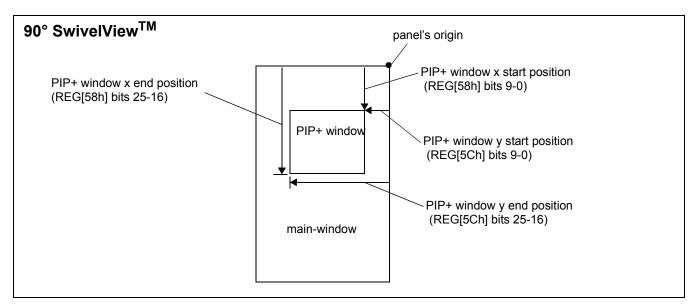

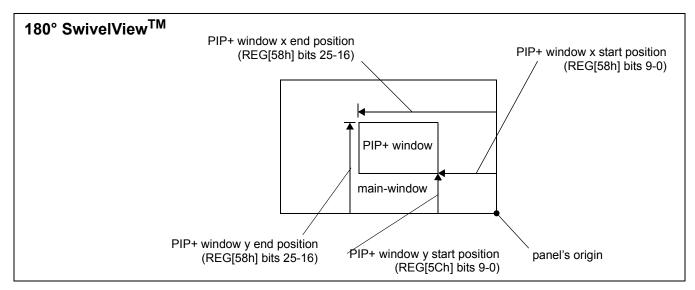

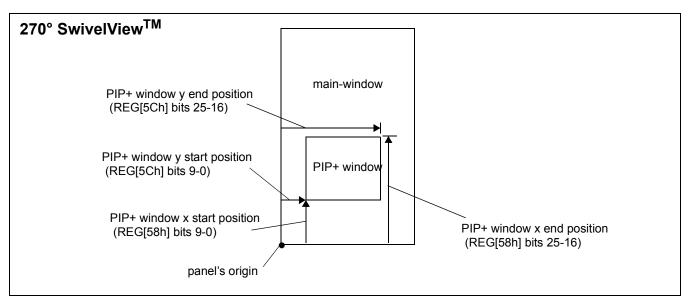

PIP<sup>+</sup> X End Position

The PIP<sup>+</sup> X End Position bits determine the horizontal end of the PIP<sup>+</sup> window in 0° and 180° SwivelView orientations. These bits determine the vertical end position in 90° and 270° SwivelView. For further information on defining the value of the X End Position, see Section 8.2, "Picture-In-Picture-Plus Examples" on page 43.

This register also increments differently based on the SwivelView orientation. For 0° and 180° SwivelView the X End Position is incremented by X pixels where X is relative to the current color depth. For 90° and 270° SwivelView the X End Position is incremented in 1 line increments.

Table 8-1: 32-bit Address Increments for PIP<sup>+</sup> X Position in SwivelView 0° and 180°

| Bits-Per-Pixel (Color Depth) | Pixel Increment (X) |

|------------------------------|---------------------|

| 1 bpp                        | 32                  |

| 2 bpp                        | 16                  |

| 4 bpp                        | 8                   |

| 8 bpp                        | 4                   |

| 16 bpp                       | 2                   |

In SwivelView  $0^{\circ}$ , these bits set the horizontal coordinates (x) of the PIP<sup>+</sup> window's right edge. Increasing x moves the right edge towards the right in steps of  $32 \div$  bits-per-pixel (see Table 8-1: ). The horizontal coordinates start at pixel 0.

Program the PIP<sup>+</sup> Window X End Position so that  $PIP^+$  Window X End Position =  $x \div (32 \div bits-per-pixel)$

#### Note

Truncate the fractional part of the above equation.

**In SwivelView 90°**, these bits set the vertical coordinates (y) of the PIP<sup>+</sup> window's bottom edge. Increasing y moves the bottom edge downward in 1 line steps. The vertical coordinates start at line 0.

Program the PIP<sup>+</sup> Window X End Position so that PIP<sup>+</sup> Window X End Position = y

In SwivelView 180°, these bits set the horizontal coordinates (x) of the PIP<sup>+</sup> window's left edge. Increasing x moves the left edge towards the right in steps of  $32 \div$  bits-per-pixel (see Table 8-1: ). The horizontal coordinates start at pixel 0.

Program the PIP<sup>+</sup> Window X End Position so that  $PIP^+$  Window X End Position = (panel width - x - 1) ÷ (32 ÷ bits-per-pixel)

#### Note

Truncate the fractional part of the above equation.

**In SwivelView 270°**, these bits set the vertical coordinates (y) of the PIP<sup>+</sup> window's top edge. Increasing y moves the top edge downwards in 1 line steps. The vertical coordinates start at line 0.

Program the PIP<sup>+</sup> Window X End Position so that PIP<sup>+</sup> Window X End Position = panel width - y - 1

#### PIP<sup>+</sup> X Start Position

The PIP<sup>+</sup> X Start Position bits determine the horizontal position of the start of the PIP<sup>+</sup> window in 0° and 180° SwivelView orientations. These bits determine the vertical start position in 90° and 270° SwivelView. For further information on defining the value of the X Start Position, see Section 8.2, "Picture-In-Picture-Plus Examples" on page 43.

The register also increments differently based on the SwivelView orientation. For 0° and 180° SwivelView the X Start Position is incremented by X pixels where X is relative to the current color depth. For 90° and 270° SwivelView the X Start Position is incremented in 1 line increments.

| Bits-per-pixel (Color Depth) | Pixel Increment (X) |

|------------------------------|---------------------|

| 1 bpp                        | 32                  |

| 2 bpp                        | 16                  |

| 4 bpp                        | 8                   |

| 8 bpp                        | 4                   |

| 16 bpp                       | 2                   |

Table 8-2: 32-bit Address Increments for Color Depth

In SwivelView  $0^{\circ}$ , these bits set the horizontal coordinates (x) of the PIP<sup>+</sup> windows's left edge. Increasing x moves the left edge towards the right in steps of  $(32 \div \text{bits-per-pixel})$  (see Table 8-2: ). The horizontal coordinates start at pixel 0.

Program the PIP<sup>+</sup> Window X Start Position so that PIP<sup>+</sup> Window X Start Position =  $x \div (32 \div bits-per-pixel)$

#### Note

Truncate the fractional part of the above equation.

**In SwivelView 90°**, these bits set the vertical coordinates (y) of the PIP<sup>+</sup> window's top edge. Increasing y moves the top edge downward in 1 line steps. The vertical coordinates start at line 0.

Program the PIP<sup>+</sup> Window X Start Position so that PIP<sup>+</sup> Window X Start Position = y

In SwivelView 180°, these bits set the horizontal coordinates (x) of the PIP $^+$  window's right edge. Increasing x moves the right edge towards the right in steps of (32  $\div$  bits-perpixel) (see Table 8-2:). The horizontal coordinates start at pixel 0.

Program the PIP<sup>+</sup> Window X Start Position so that PIP<sup>+</sup> Window X Start Position = (panel width - x - 1)  $\div$  (32  $\div$  bits-per-pixel)

#### Note

Truncate the fractional part of the above equation.

**In SwivelView 270°**, these bits set the vertical coordinates (y) of the PIP<sup>+</sup> window's bottom edge. Increasing y moves the bottom edge downwards in 1 line steps. The vertical coordinates start at line 0.

Program the PIP<sup>+</sup> Window X Start Position so that  $PIP^+$  Window X Start Position = panel width - y - 1

| PIP <sup>+</sup> Y | PIP <sup>+</sup> Y Positions Register |    |        |    |    |    |     |                      |              |      |                        |              |       |       |    |    |

|--------------------|---------------------------------------|----|--------|----|----|----|-----|----------------------|--------------|------|------------------------|--------------|-------|-------|----|----|

| REG[5              | 5Ch]                                  |    | 000001 | า  |    |    |     |                      |              |      |                        |              | Read/ | Write |    |    |

|                    |                                       |    |        |    |    |    | PIP | <sup>+</sup> Y End P | osition bits | 9-0  |                        |              |       |       |    |    |

| 31                 | 30                                    | 29 | 28     | 27 | 26 | 25 | 24  | 23                   |              | 22   | 21                     | 20           | 19    | 18    | 17 | 16 |

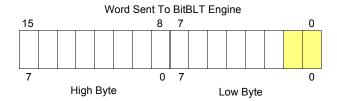

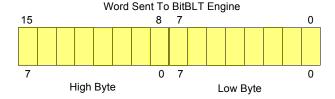

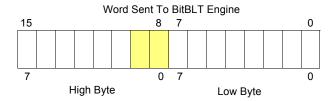

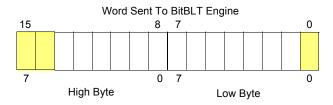

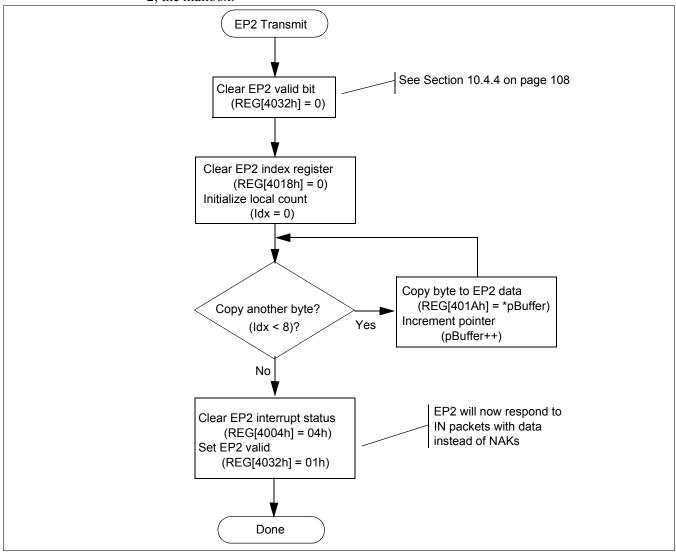

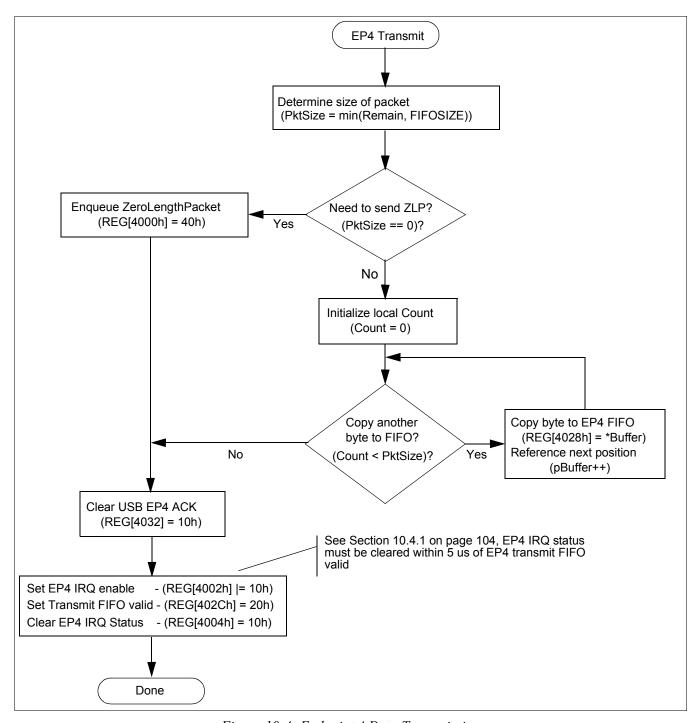

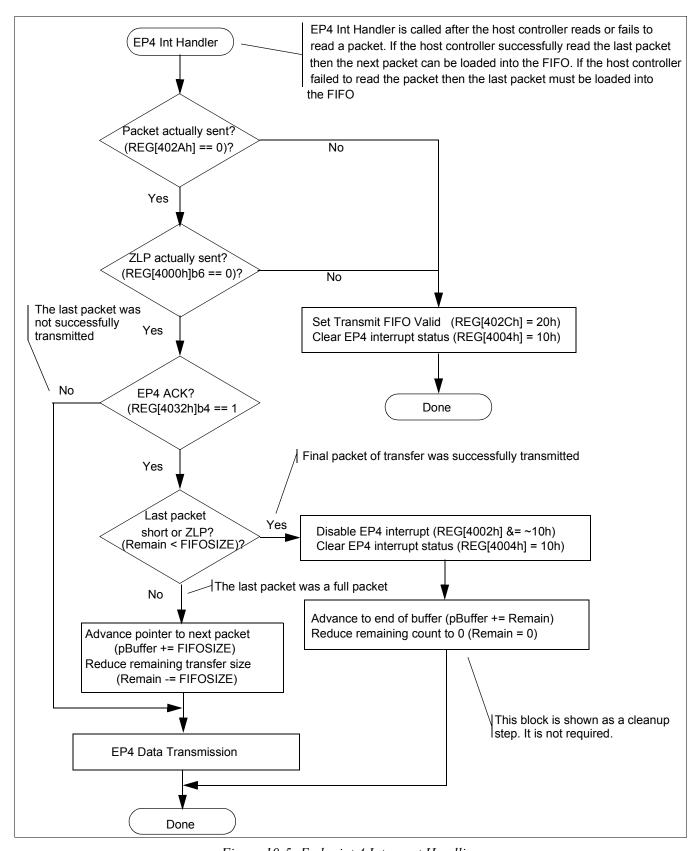

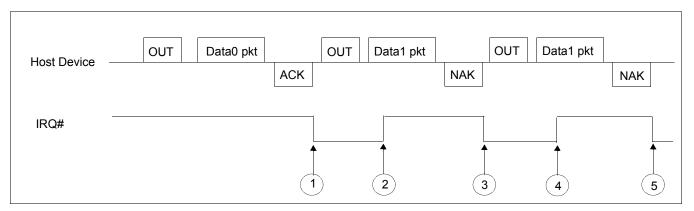

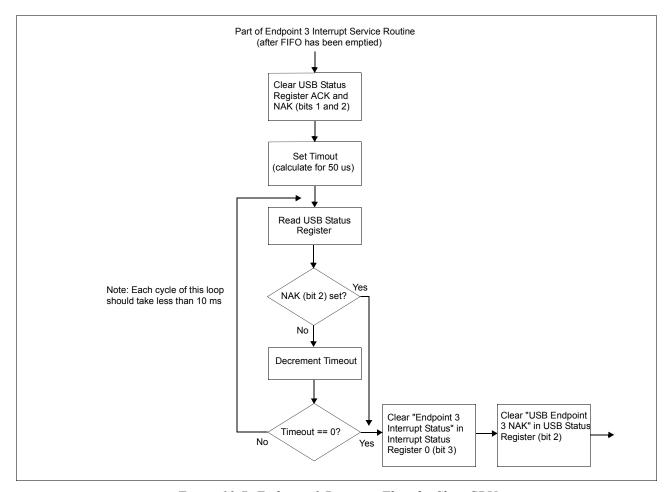

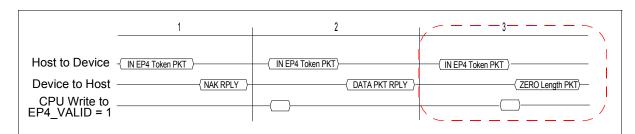

|                    | n/a                                   |    |        |    |    |    |     |                      |              | PIP. | <sup>+</sup> Y Start P | osition bits | s 9-0 |       |    |    |