## S1D13L04 XGA Simple LCD Controller

# Hardware Functional Specification

Document Number: XB3A-A-001-01.1

| NI | $\sim$ | ГΙ | $\sim$ | _ |

|----|--------|----|--------|---|

| Ν  | O      | ı  | C      |   |

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. When exporting the products or technology described in this material, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You are requested not to use, to resell, to export and/or to otherwise dispose of the products (and any technical information furnished, if any) for the development and/or manufacture of weapon of mass destruction or for other military purposes.

All brands or product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

©SEIKO EPSON CORPORATION 2016-2018. All rights reserved.

## **Table Of Contents**

| Chapter | 1 Intro | oduction                        |

|---------|---------|---------------------------------|

| 1.1     | Scope   |                                 |

| 1.2     | Overv   | iew Description                 |

| Chapter | 2 Fea   | tures                           |

| 2.1     | Memo    | ry                              |

| 2.2     | CPU I   | nterfaces                       |

| 2.3     | Panel   | Interface Support               |

| 2.4     | Displa  | y Features                      |

| 2.5     | Clock   | Source                          |

| 2.6     | Misce   | llaneous                        |

| Chapter | 3 Sys   | tem Diagram                     |

| Chapter | 4 Blo   | ck Diagram                      |

| Chapter | 5 Pins  | s                               |

| 5.1     |         | BL04 Pinout Diagrams            |

| 5       |         | QFP22 208-pin Pinout            |

| 5.2     | Pin De  | escription                      |

|         |         | Host Interface                  |

| 5       | .2.2    | LCD Interface                   |

| 5       | .2.3    | SDRAM Interface                 |

| 5       | .2.4    | GPIO / Multi Function Interface |

| 5       | .2.5    | Miscellaneous                   |

| 5       | .2.6    | Power And Ground                |

| 5.3     | Summ    | ary of Configuration Options    |

| 5.4     | Host E  | Bus Interface Pin Mapping       |

| 5.5     | LCD I   | nterface Pin Mapping            |

| 5.6     | GPIO    | Pin Mapping                     |

| 5.7     | PWM     | Interface Pin Mapping           |

| Chapter | 6 D.C   | . Characteristics               |

| Chapter | 7 A.C   | . Characteristics               |

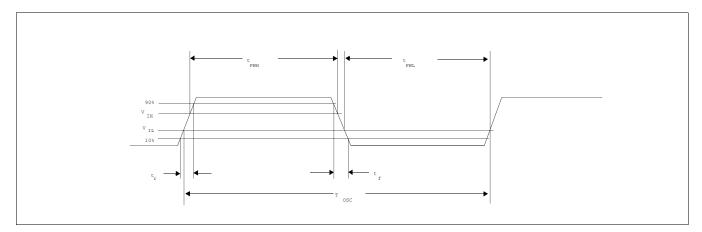

| 7.1     | Clock   | Timing                          |

| 7       | .1.1    | Input Clocks                    |

| 7       | .1.2    | Internal Clocks                 |

| 7       | .1.3    | PLL Clock                       |

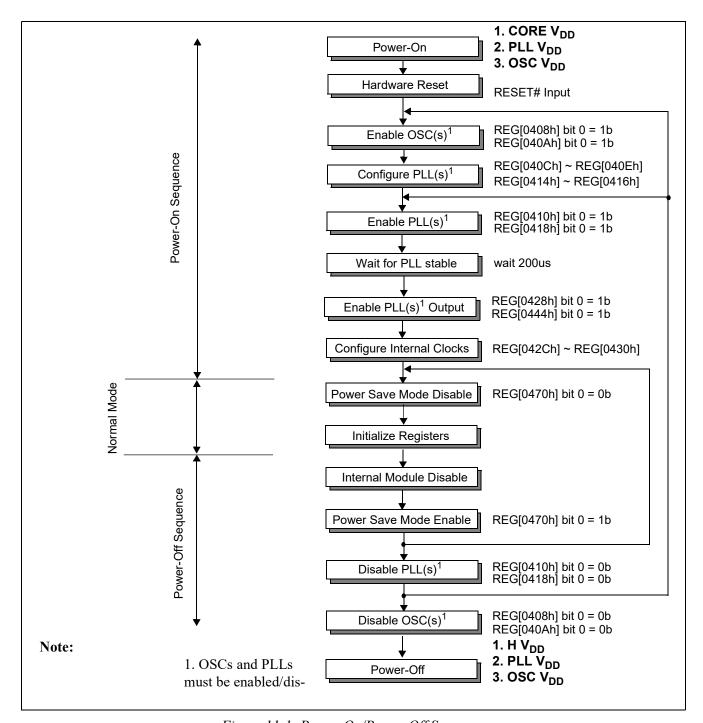

| 7.2     | Power   | Supply Sequence                 |

| 7       | .2.1    | Power Supply Structure          |

| 7       | .2.2    | Power-On Sequence               |

| 7.2.3 Power-Off Sequence                       | 42  |

|------------------------------------------------|-----|

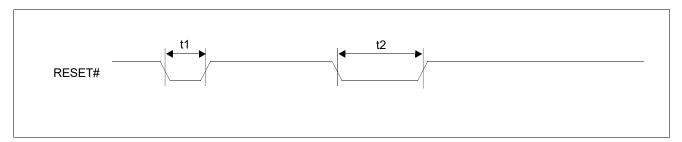

| 7.3 RESET# Timing                              | 43  |

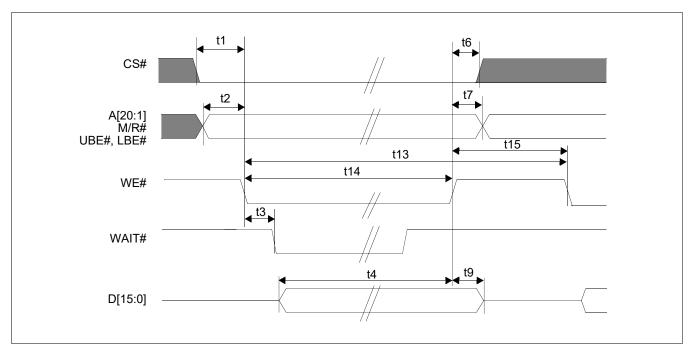

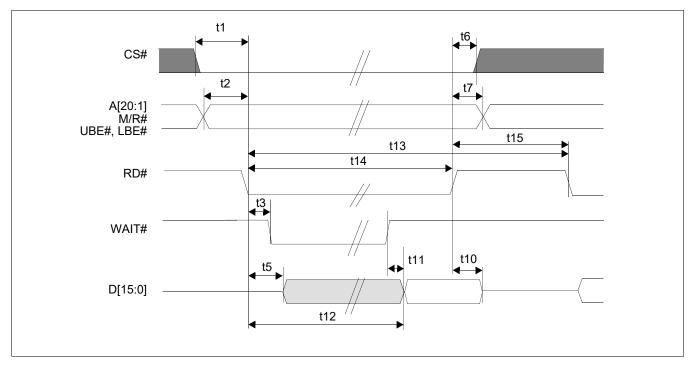

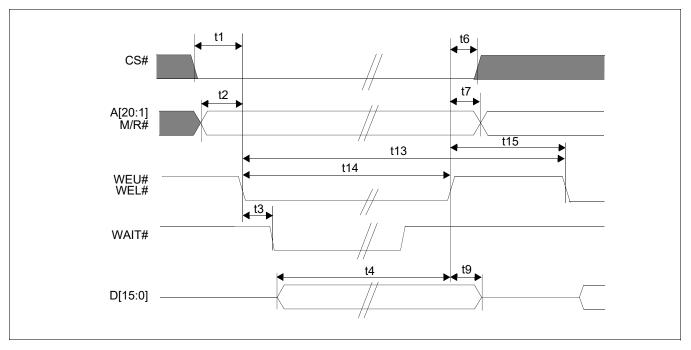

| 7.4 Host Bus Interface Timing                  | 44  |

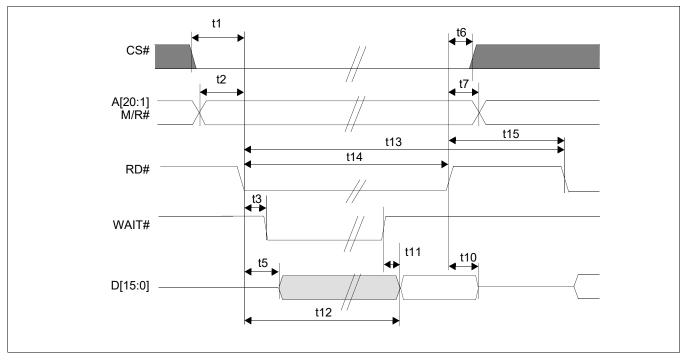

| 7.4.1 Direct/Indirect 80 Type 1                | 44  |

| 7.4.2 Direct/Indirect 80 Type 2                | 46  |

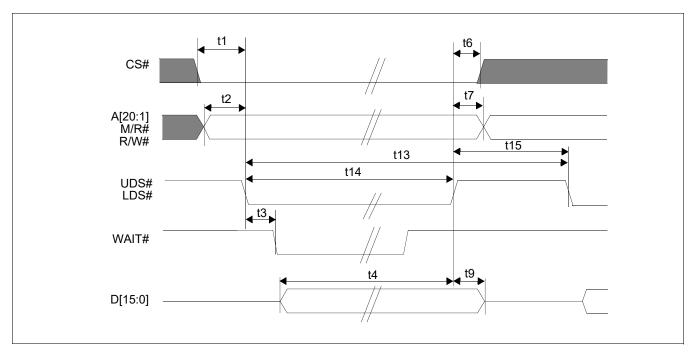

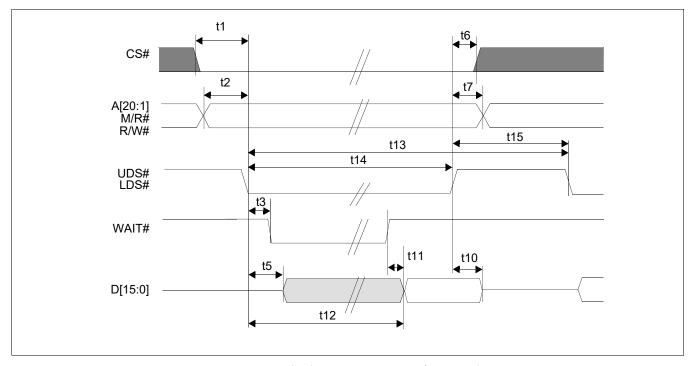

| 7.4.3 Direct/Indirect 68                       | 48  |

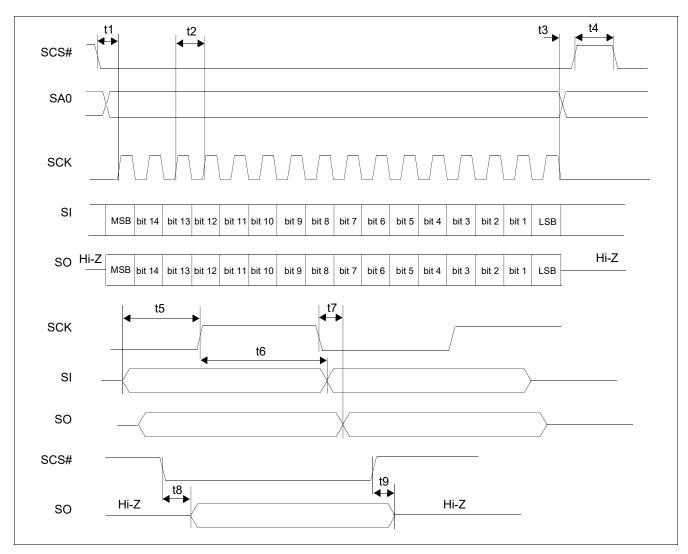

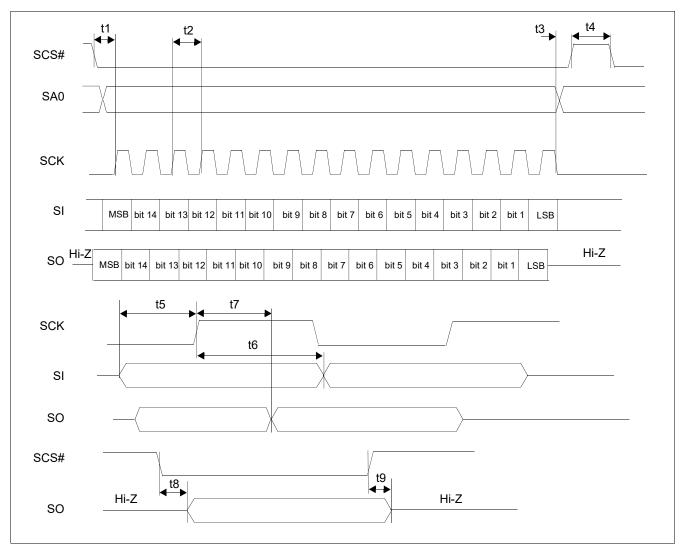

| 7.4.4 Serial Host                              | 50  |

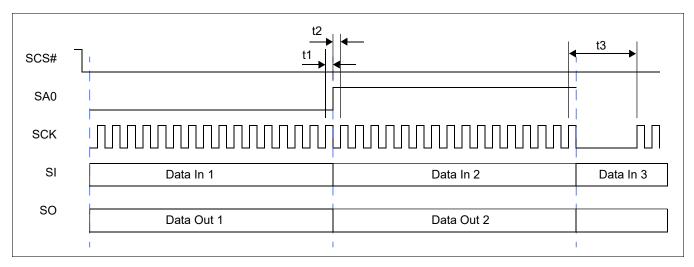

| 7.4.5 Serial Host Interface Burst Mode         | 52  |

| 7.5 Power Sequencing                           | 52  |

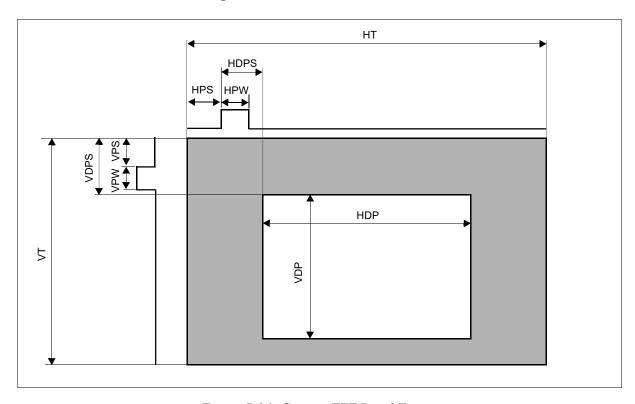

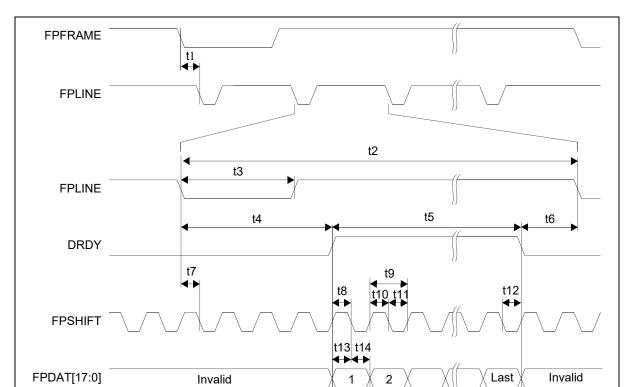

| 7.6 Panel Interface Timing                     | 53  |

| 7.6.1 Generic TFT Panel Timing                 | 53  |

| 7.6.2 ND-TFD 8-Bit Serial Interface Timing     | 57  |

| 7.6.3 ND-TFD 9-Bit Serial Interface Timing     | 58  |

| 7.6.4 a-Si TFT Serial Interface Timing         | 59  |

| 7.6.5 uWIRE Serial Interface Timing            | 60  |

| 7.6.6 24-bit Serial Interface Timing           | 61  |

| 7.7 SDRAM Interface Timing                     | 62  |

| Chapter 8 Memory Map                           | 66  |

| 8.1 Accessing Memory using Direct Addressing   | 66  |

| 8.2 Accessing Memory using Indirect Addressing | 68  |

| 8.3 IO Map                                     | 68  |

| Chapter 9 Clocks                               | 69  |

| 9.1 Clock Overview                             |     |

| 9.2 PLL Programming Examples                   | 70  |

| Chapter 10 Registers                           | 71  |

| 10.1 Register Mapping                          |     |

| 10.2 Register Set                              |     |

| 10.3 Register Restrictions                     |     |

| 10.4 Register Descriptions                     |     |

| 10.4.1 Host Interface Registers                |     |

| 10.4.2 System Control Registers                |     |

| 10.4.3 LCD Panel Configuration Registers       | 100 |

| 10.4.4 LCD Display Mode Registers              | 108 |

| 10.4.5 GPIO Registers                          | 129 |

| 10.4.6 Memory Controller Registers             |     |

| 10.4.7 PWM Registers                           | 149 |

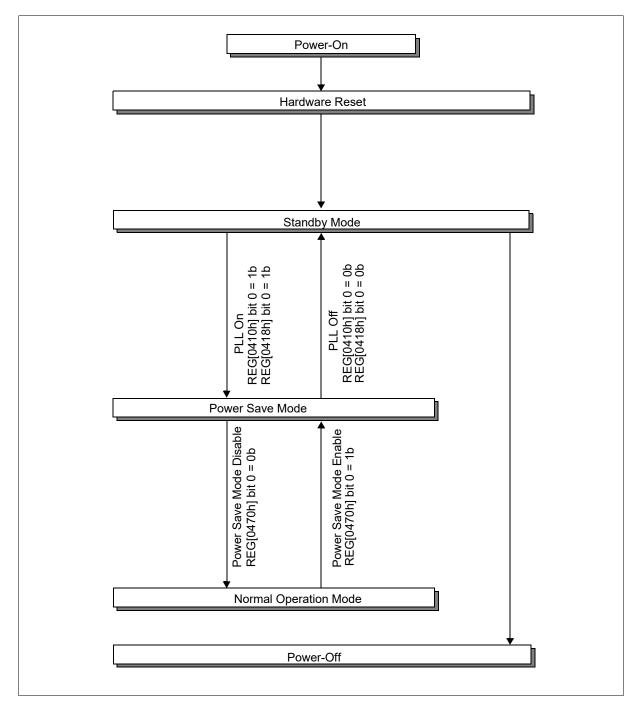

| Chapter 11 Power Save Modes                    | 157 |

| 11.1 Power-On/Power-Off Sequence               |     |

| 11.2 Operational Modes                         |     |

|                                                |     |

| 11.2.1 Power-On                                      |

|------------------------------------------------------|

| 11.2.2 Reset                                         |

| 11.2.3 Standby Mode                                  |

| 11.2.4 Power Save Mode                               |

| 11.2.5 Normal Mode                                   |

| 11.2.6 Power-Off                                     |

| 11.3 Power Save Mode Functions                       |

| Chapter 12 Data Formats                              |

| 12.1 Memory Data Formats                             |

| Chapter 13 Display Functions                         |

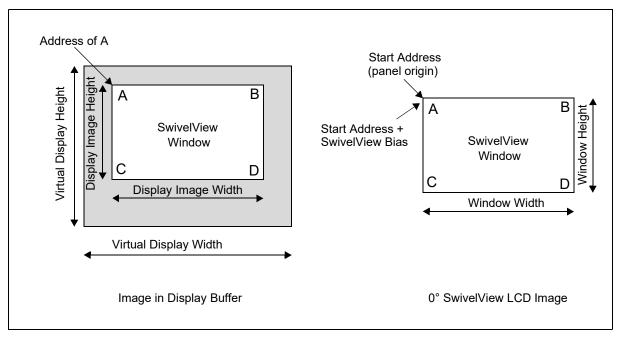

| 13.1 SwivelView <sup>TM</sup>                        |

| 13.1.1 0° SwivelView                                 |

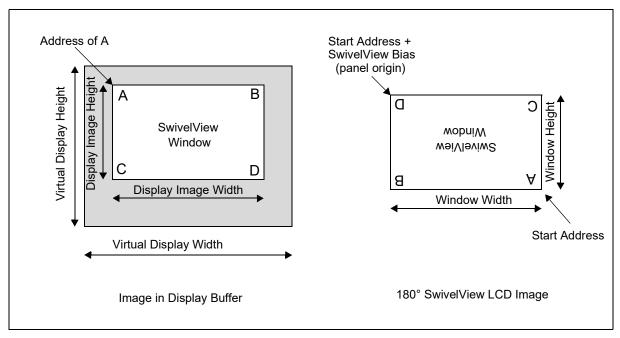

| 13.1.2 180° SwivelView                               |

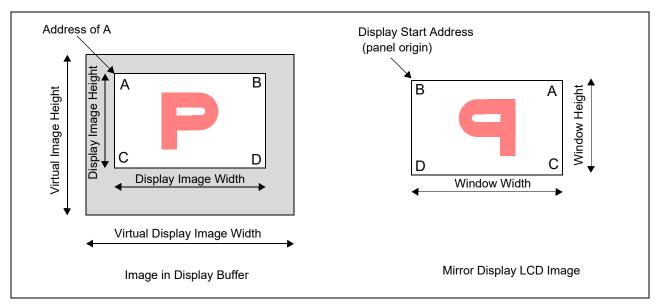

| 13.2 Mirror Display                                  |

| 13.2.1 Mirror Display for 0° SwivelView              |

| 13.2.2 Mirror Display Combined with SwivelView Modes |

| 13.3 Gamma Correction                                |

| 13.3.1 Gamma LUT Bank Selection                      |

| 13.3.2 Programming the Gamma LUTs                    |

| 13.4 Pseudo Color Mode                               |

| Chapter 14 SDRAM Interface                           |

| 14.1 SDRAM Initialization                            |

| 14.1.1 Initializing Normal SDRAM                     |

| 14.1.2 Initializing Mobile SDRAM                     |

| 14.2 Memory Bandwidth                                |

| Chapter 15 Pulse Width Modulation (PWM)              |

| 15.1 PWM Circuit Overview                            |

| 15.2 Other Notes                                     |

| Chapter 16 Host Interface                            |

| 16.1 Hardware Configuration                          |

| 16.1.1 Chip Select (1 CS# vs. 2 CS#)                 |

| 16.1.2 Endian Mode                                   |

| 16.1.3 CNF[4:0]- Host Bus Interface Type             |

| 16.1.4 Serial Host Interface Clock Polarity          |

| 16.2 Host Bus Time-out Function                      |

| 16.2.1 Host Read/Write Cycle Time-out                |

| 16.2.2 Host WAIT# Length Time-out                    |

| 16.3 Indirect Interface                              |

| 16.3.1 Indirect Addressing for Register Access       |

| 16.3.2        | Register Access                                          |

|---------------|----------------------------------------------------------|

| 16.3.3        | Memory Access                                            |

| 16.4 Read     | Ahead Feature                                            |

| 16.5 Seria    | l Interface                                              |

| 16.5.1        | Description                                              |

| 16.5.2        | Burst Mode Operation                                     |

| 16.5.3        | Data Transfer Examples                                   |

| 16.5.4        | Indirect Register Address Auto Increment Serial Examples |

| 16.6 Regis    | ster Accesses for Big Endian Host Interfaces             |

| Chapter 17 Lo | CD Panel Interface .........................199          |

| 17.1 TFT/     | ND-TFD Panels                                            |

| 17.1.1        | TFT/ND-TFD Data Output Formats                           |

| 17.1.2        | RGB Serial Command Interfaces                            |

| 17.1.3        | TFT/ND-TFD Programming Flow                              |

| Chapter 18 C  | rystal Oscillator Circuit                                |

| Chapter 19 D  | esign Considerations ........................204         |

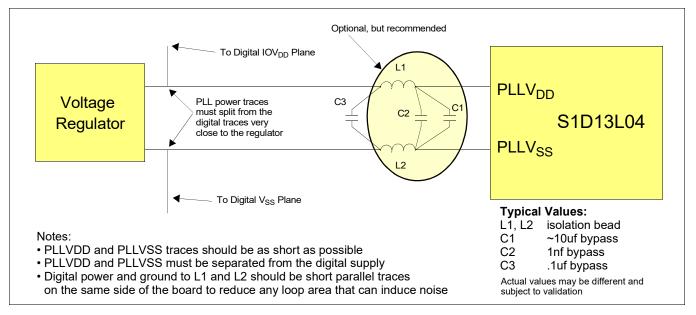

| 19.1 Guid     | elines for PLL Power Layout                              |

| Chapter 20 M  | echanical Data                                           |

| Chapter 21 C  | hange Record ...........................207              |

| Chapter 22 Sa | ales and Technical Support                               |

## **Chapter 1 Introduction**

#### 1.1 Scope

This is the Hardware Functional Specification for the S1D13L04 XGA Simple LCD Controller. Included in this document are timing diagrams, AC and DC characteristics, register descriptions, and power management descriptions. This document is intended for two audiences: Video Subsystem Designers and Software Developers.

This document is updated as appropriate. Please check for the latest revision of this document before beginning any development. The latest revision can be downloaded at vdc.epson.com.

We appreciate your comments on our documentation. Please contact us via email at vdc-documenation@ea.epson.com.

#### 1.2 Overview Description

The S1D13L04 is a simple, multi-purpose Graphics LCD Controller which supports up to XGA resolution TFT panels. With an external SDRAM memory controller, it allows up to 16Mbyte as a display frame buffer. The S1D13L04 supports most popular CPU interfaces in both 16-bit and Direct/Indirect variations.

The S1D13L04's combination of multiple CPU interfaces and display interface types offers a versatile, yet easy to develop display system. Additionally, it offers such features as Multiple Windows (PIP), Alpha Blending, Gamma Correction, and Mirror/Rotation which allow user configurability of various images on the Main/PIP1/PIP2 windows. The S1D13L04 is a flexible, low cost, low power solution that meets the demands of embedded markets such as medical, office automation, factory automation, home automation and measuring instruments, where total system cost concerns can still be met when using TFT panels up to XGA resolution.

## **Chapter 2 Features**

#### 2.1 Memory

- Uses external SDRAM or mobile SDRAM as the display buffer (no embedded memory)

- Memory is addressable using direct or indirect access modes

- Linear access to the first 1M bytes of memory and four configurable 256K byte windows into the remaining area

- SDRAM Interface

- Supports up to 100MHz SDRAM bus clock

- Supports x16 SDRAM interfaces

- Supports 8/16M bytes of 4 bank SDRAM

- Supports 8/16M bytes of 4 bank Mobile SDRAM

- Low power design

- Automatic re-entry into self refresh mode

#### Note

For memory usage guidelines, see Section 14.2, "Memory Bandwidth" on page 176.

#### 2.2 CPU Interfaces

- Direct and indirect interface support of the Intel 80, 68 16-bit CPU interfaces.

- · Serial Host Interface

- Registers are memory-mapped M/R# input selects between memory and register address space

#### 2.3 Panel Interface Support

- RGB interface single-panels

- Color TFT Panels

- 16/18-bit interface

- Generic TFT/TFD interface

- Optional serial command interface supports:

- TFT w/µ-Wire interface (16-bit)

- EPSON ND-TFD 4 pin interface (8-bit)

- EPSON ND-TFD 3 pin interface (9-bit)

- 8/24-bit command interface

- Panel Resolution Examples

- For memory usage guidelines, see Section 14.2, "Memory Bandwidth" on page 176.

#### 2.4 Display Features

- Multiple window (layer) support

- Main window and PIP1 window (if enabled) form the View Port (bottom layer)

- 8/16/32 bit-per-pixel (bpp) color depths

- alpha blending is not supported for the View Port

- mirror and 180° rotation functions

- optional gamma correction

- PIP2 window (if enabled) is the top layer

- 8/16/32 bit-per-pixel (bpp) color depths

- optional alpha blending function (ARGB 1:5:5:5 / ARGB 4:4:4:4 / ARGB 8:8:8:8 formats including alpha map)

- optional transparency function

- mirror and 180° rotation functions

- optional gamma correction

- Mirror and Rotation

- Mirror function performs a horizontal flip of the display image

- independent controls for View Port (Main/PIP window) and PIP2 window

- Rotation function performs a 180° counter-clockwise rotation of the display image

- independent controls for View Port (Main/PIP window) and PIP2 window

- Alpha Blending

- Supports alpha blending between the View Port (Main + PIP1) and the PIP2 window

- 8-bit constant alpha value

- Dynamic alpha with alpha map

- Combined with transparency

#### **Features**

- Gamma Correction

- Selectable gamma correction for Main/PIP1/PIP2 windows

- 2 Gamma Correction Look-up Tables (Bank A and Bank B) using Single Port SRAM

- Independent color correction for each of RGB components

- View Port (Main+PIP1 window) can be dynamically switched between LUT banks

- Async table access

- Pseudo Color Expansion

- Async table access

- 2x2 Dither matrix

- 2x2 FRM

- Error Diffusion

- 2-bit color reduction

- Interrupt support

- Maskable Non-Display (Vsync) interrupt

- Vsync interrupt assertion can be delayed a configurable number of lines

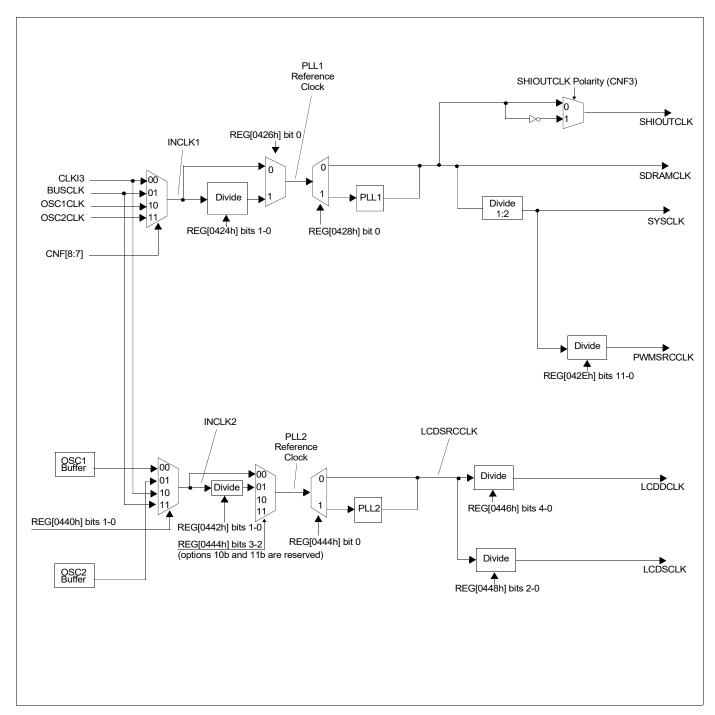

#### 2.5 Clock Source

- 2 embedded PLLs

- PLL1 source: BUSCLK, CLKI3, OSCI1/OSCO1, or OSCI2/OSCO2

- PLL2 source: BUSCLK, CLKI3, OSCI1/OSCO1, or OSCI2/OSCO2

- Two crystal inputs: OSCI1/OSCO1 and OSCI2/OSCO2

- Two digital inputs: BUSCLK, CLKI3

- Clock Outputs: MEMCLK

#### 2.6 Miscellaneous

- Supports maximum 50MHz Internal System Clock

- IRQ output pin

- IRQ Source (VSYNC, Delayed VSYNC, Etc.)

- PWM: 4 channel for backlight control

- Software initiated power save mode

- Clocks are dynamically turned off when modules are not needed

- General Purpose Input/Output pins are available

- Operating system independent

- Extended Temperature Range: -40 to 85°

- Power Supplies:

- IO operates at 3.3 volts  $\pm 0.3$ V

- Core operates at 1.8 volts  $\pm 0.15$ V

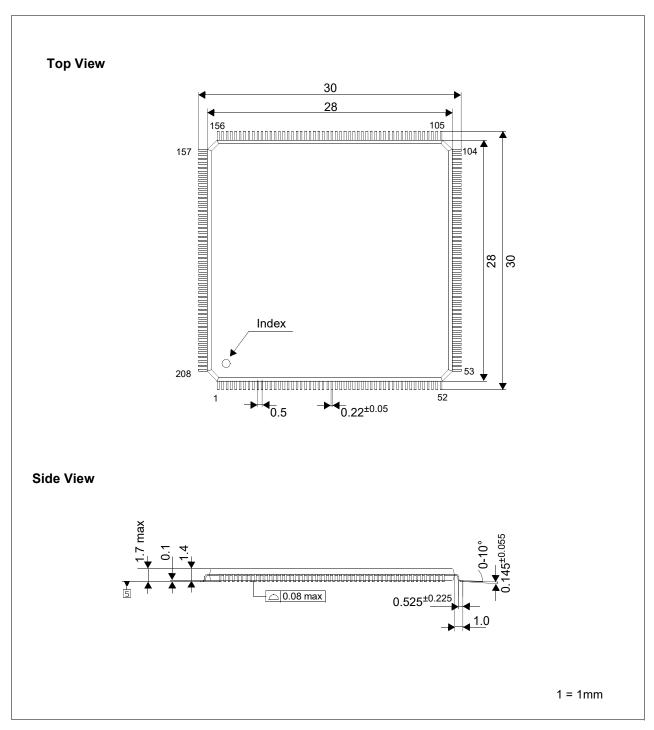

- Package Type:

- QFP22 208-pin package (28 x 28 x 1.4 mm, Pin pitch: 0.5 mm)

## **Chapter 3 System Diagram**

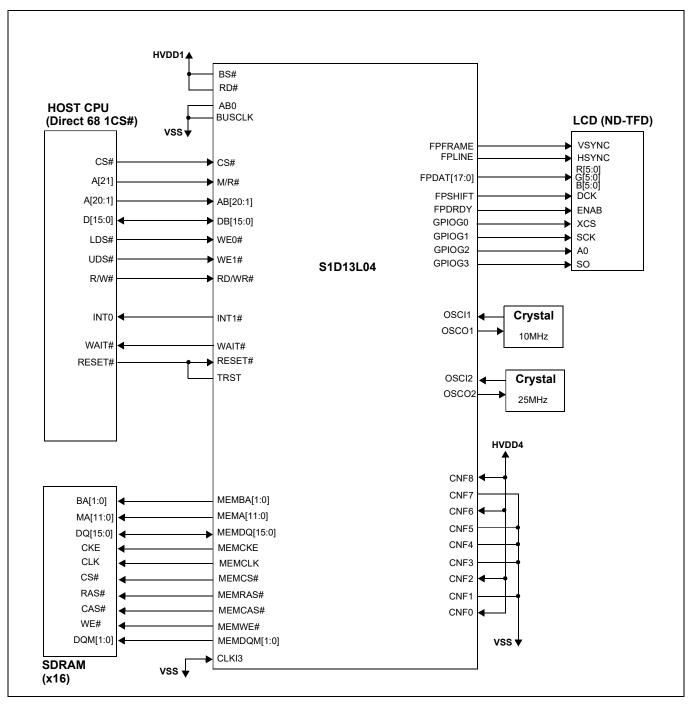

The following diagram is an example of a typical system implementation. For detailed pin descriptions and pin mapping, refer to Section Chapter 5, "Pins" on page 14.

Figure 3-1: Example System Diagram

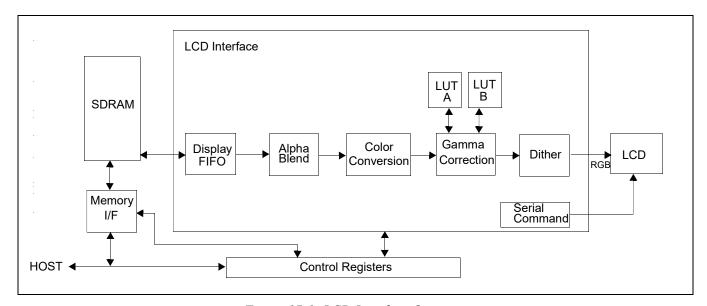

## **Chapter 4 Block Diagram**

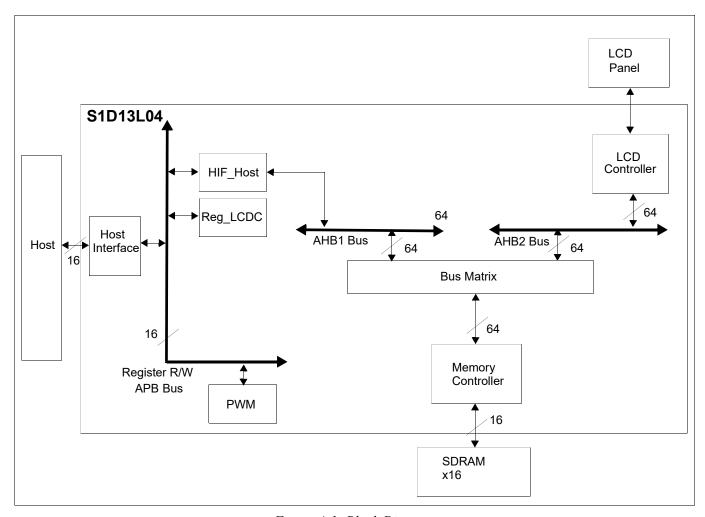

Figure 4-1: Block Diagram

## **Chapter 5 Pins**

The S1D13L04 is available in following package format:

• QFP22 208-pin

#### 5.1 S1D13L04 Pinout Diagrams

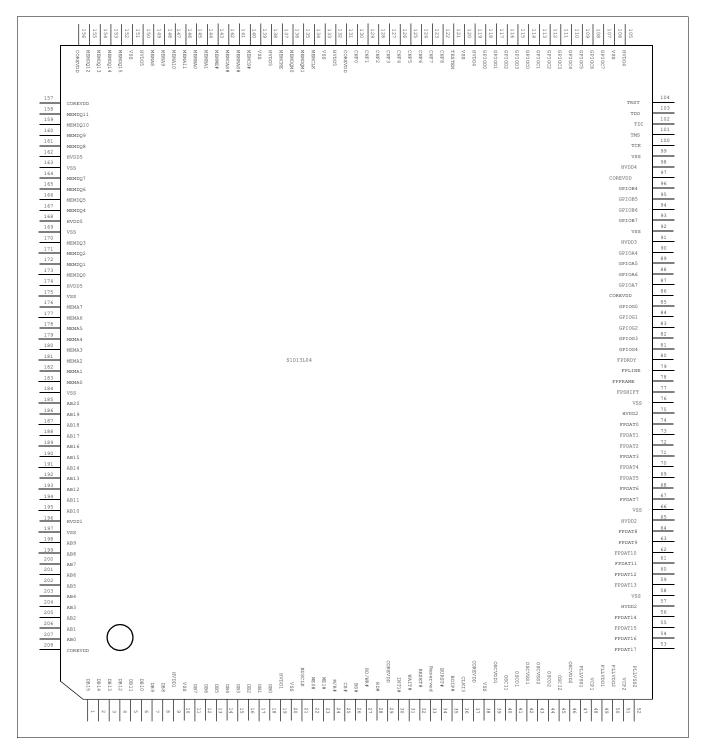

#### 5.1.1 QFP22 208-pin Pinout

Figure 5-1: QFP22-208 Pinout

## 5.2 Pin Description

#### Key:

#### Pin Types

I = Input O = Output

IO = Bi-Directional (Input/Output)

P = Power pin

#### **RESET# States**

H = High level output

L = Low level output

Z = High Impedance (Hi-Z)

1 = Pull-up resistor on input

0 = Pull-down resistor on input

# = Active low level

Table 5-1: Cell Descriptions

| Cell     | Description                                                                       |

|----------|-----------------------------------------------------------------------------------|

| ILTR     | Low voltage transparent input                                                     |

| OLTR     | Low voltage transparent output                                                    |

| IC       | LVCMOS input                                                                      |

| ICD1     | LVCMOS input with pull-down resistor (50kΩ@3.3V)                                  |

| ICD2     | LVCMOS input with pull-down resistor (100kΩ@3.3V)                                 |

| ICU1     | LVCMOS input with pull-up resistor (50kΩ@3.3V)                                    |

| ICS      | LVCMOS schmitt input                                                              |

| ICSD1    | LVCMOS schmitt input with pull-down resistor (50kΩ@3.3V)                          |

| ICSP1    | LVCMOS schmitt input with pull-up resistor (50kΩ@3.3V)                            |

| ICSP2    | LVCMOS schmitt input with pull-up resistor (100kΩ@3.3V)                           |

| OTLN4    | Low noise output buffer (4mA@3.3V, deltaV = 0.4V)                                 |

| OTLN8    | Low noise output buffer (8mA@3.3V, deltaV = 0.4V)                                 |

| BLNC4D1  | Low noise LVCMOS IO buffer (4mA@3.3V) with pull-down resistor (50kΩ@3.3V)         |

| BLNC4D2  | Low noise LVCMOS IO buffer (4mA@3.3V) with pull-down resistor (100kΩ@3.3V)        |

| BLNC4P1  | Low noise LVCMOS IO buffer (4mA@3.3V) with pull-up resistor (50kΩ@3.3V)           |

| BLNCS4D1 | Low noise LVCMOS schmitt IO buffer (4mA@3.3V) with pull-down resistor (50kΩ@3.3V) |

| Р        | Power                                                                             |

#### 5.2.1 Host Interface

Many of the host interface pins have different functions depending on the host bus interface that is selected using the CNF[6:0] pins (see Section 5.3, "Summary of Configuration Options" on page 29). To determine the pin mapping and pin functions for each host bus interface, refer to Table 5-9:, "Host Bus Interface Pin Mapping (Direct Interfaces)," on page 31, and Table 5-10:, "Host Bus Interface Pin Mapping (Indirect Interfaces)," on page 32.

Table 5-2: Host Interface Pin Descriptions

| Pin Name | Туре | QFP<br>Pin#         | Cell    | Power | RESET#<br>State | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|------|---------------------|---------|-------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AB[20:0] | ı    | 185-195,<br>198-207 | ICD1    | HVDD1 | Z               | These input pins are System Address pins 20-0.  For detailed pin functions for each host bus interface, see Section 5.4, "Host Bus Interface Pin Mapping" on page 31.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DB[15:0] | Ю    | 1-8,11-18           | BLNC4D1 | HVDD1 | Z               | These input/output pins are System Data Bus pins 15-0.  For detailed pin functions for each host bus interface, see Section 5.4, "Host Bus Interface Pin Mapping" on page 31.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CS#      | -    | 25                  | ICU1    | HVDD1 | Z               | <ul> <li>This input pin is Chip Select and has multiple functions configured according to the Host Bus Interface selected using CNF[4:0].</li> <li>For 1 CS# mode, this pin inputs the chip select signal (CS#).</li> <li>For 2 CS# mode, this pin inputs the memory chip select signal (CSM#).</li> <li>When the Serial Host Interface is selected, this pin is the Serial Host Chip Select (SCS#).</li> <li>For detailed pin functions for each host bus interface, see Section 5.4, "Host Bus Interface Pin Mapping" on page 31.</li> </ul>                                                                                                                                                                                                                          |

| M/R#     |      | 24                  | ICU1    | HVDD1 | Z               | <ul> <li>This input pin has multiple functions.</li> <li>For 1 CS# mode, this pin selects between the display buffer and register address spaces. When M/R# is set high, the display buffer is accessed and when M/R# is set low the registers are accessed.</li> <li>For 2 CS# mode, this pin inputs the register chip select (CSR#).</li> <li>For Indirect Host Bus Interfaces and Serial Host Bus Interfaces, the internal pull-down resistor is enabled and this pin must be left unconnected.</li> <li>For Serial Host Bus Interfaces, the internal pull-down resistor is enabled and this pin must be left unconnected.</li> <li>For detailed pin functions for each host bus interface, see Section 5.4, "Host Bus Interface Pin Mapping" on page 31.</li> </ul> |

Table 5-2: Host Interface Pin Descriptions

| Pin Name | Туре     | QFP<br>Pin# | Cell | Power                                                                                                                 | RESET#<br>State | Description                                                                                                                    |

|----------|----------|-------------|------|-----------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------|

|          |          |             |      |                                                                                                                       |                 | This input pin has multiple functions.                                                                                         |

|          |          |             |      |                                                                                                                       |                 | <ul> <li>For the Direct/Indirect 68 interface, this pin<br/>must be connected to VDD.</li> </ul>                               |

| RD#      |          | 28          | ICU1 | HVDD1                                                                                                                 | z               | <ul> <li>For the Direct/Indirect 80 Type 1 and Type 2<br/>interfaces, this pin is the read enable signal<br/>(RD#).</li> </ul> |

| KD#      | <b>'</b> | 20          | 1001 | HVDD1                                                                                                                 |                 | For detailed pin functions for all other interfaces, refer to the Specification for each Host.                                 |

|          |          |             |      |                                                                                                                       |                 | For detailed pin functions for each host bus interface, see Section 5.4, "Host Bus Interface Pin Mapping" on page 31.          |

|          |          |             |      |                                                                                                                       |                 | This input pin has multiple functions.                                                                                         |

|          |          | I 27        |      |                                                                                                                       |                 | For the Direct/Indirect 68 interface, this pin is<br>the read/write signal (R/W#).                                             |

|          |          |             | ICU1 |                                                                                                                       | Z               | For the Direct/Indirect 80 Type 1 interface, this pin is the write enable signal (WE#).                                        |

| RD/WR#   | ı        |             |      | HVDD1                                                                                                                 |                 | For the Direct/Indirect 80 Type 2 interface, this pin must be connected to VDD.                                                |

|          |          |             |      |                                                                                                                       |                 | For detailed pin functions for all other interfaces, refer to the Specification for each Host.                                 |

|          |          |             |      | For detailed pin functions for each host bus interface, see Section 5.4, "Host Bus Interface Pin Mapping" on page 31. |                 |                                                                                                                                |

|          |          |             |      |                                                                                                                       |                 | This input pin has multiple functions.                                                                                         |

|          |          |             |      |                                                                                                                       |                 | For the Direct/Indirect 68 interface, this pin is<br>the lower data strobe (LDS#).                                             |

|          |          | 22          | ICU1 |                                                                                                                       |                 | For the Direct/Indirect 80 Type 1 interface, this pin is the lower byte enable signal (LBE#).                                  |

| WE0#     | 1        |             |      | HVDD1                                                                                                                 | Z               | For the Direct/Indirect 80 Type 2 interface, this pin is the lower byte write enable signal (WEL#).                            |

|          |          |             |      |                                                                                                                       |                 | For detailed pin functions for all other interfaces, refer to the Specification for each Host.                                 |

|          |          |             |      |                                                                                                                       |                 | For detailed pin functions for each host bus interface, see Section 5.4, "Host Bus Interface Pin Mapping" on page 31.          |

Table 5-2: Host Interface Pin Descriptions

| Pin Name | Туре | QFP<br>Pin# | Cell    | Power | RESET#<br>State | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|------|-------------|---------|-------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |      |             |         |       |                 | <ul> <li>This input/output pin has multiple functions.</li> <li>For the Direct/Indirect 68 interface, this pin is the upper data strobe (UDS#).</li> <li>For the Direct/Indirect 80 Type 1 interface, this pin is the upper byte enable signal (UBE#).</li> </ul>                                                                                                                                                                                                                |

| WE1#     | Ю    | 23          | BLNC4P1 | HVDD1 | Z               | <ul> <li>For the Direct/Indirect 80 Type 2 interface, this pin is the upper byte write enable signal (WEU#).</li> <li>For detailed pin functions for all other interfaces, refer to the Specification for each Host.</li> </ul>                                                                                                                                                                                                                                                  |

|          |      |             |         |       |                 | For detailed pin functions for each host bus interface, see Section 5.4, "Host Bus Interface Pin Mapping" on page 31.                                                                                                                                                                                                                                                                                                                                                            |

| BS#      | ı    | 26          | ICU1    | HVDD1 | Z               | This input pin has multiple functions. For detailed pin functions for each host bus interface, see Section 5.4, "Host Bus Interface Pin Mapping" on page 31.                                                                                                                                                                                                                                                                                                                     |

| BURST#   | ı    | 34          | ICU1    | HVDD1 | Z               | This pin must be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| BDIP#    | ı    | 35          | ICU1    | HVDD1 | Z               | This pin must be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| WAIT#    | 0    | 31          | OTLN4   | HVDD1 | Z               | During a data transfer, this output pin is driven active to force the system to insert wait states. It is driven inactive to indicate the completion of a data transfer. WAIT# is released to the high impedance state after the data transfer is complete. The active polarity is configured according to the Host Bus Interface selected using CNF[4:0]. For detailed pin functions for each host bus interface, see Section 5.4, "Host Bus Interface Pin Mapping" on page 31. |

| RESET#   | ı    | 32          | ICS     | HVDD1 | 1               | This active low input sets all internal registers to their default state and to force all signals to their inactive states.                                                                                                                                                                                                                                                                                                                                                      |

|          |      |             |         |       |                 | <b>Note:</b> For details on RESET# timing, refer to Section 7.3, "RESET# Timing" on page 43 and Section 7.2, "Power Supply Sequence" on page 41.                                                                                                                                                                                                                                                                                                                                 |

| BUSCLK   | 1    | 21          | ICU1    | HVDD1 | Z               | This pin is typically used for clock input for serial host interface. Or it can be used for SDRAM or LCD.Clock input through PLL1 or PLL2. When it is not used, it should be connected to VSS.                                                                                                                                                                                                                                                                                   |

|          |      |             |         |       |                 | For details on the S1D13L04 clock structure, refer to Section Chapter 9, "Clocks" on page 69.                                                                                                                                                                                                                                                                                                                                                                                    |

| INT1#    | 0    | 30          | OTLN4   | HVDD1 | Z               | This output pin is the primary IRQ output from the S1D13L04. When enabled (REG[002Ah] bit 15 = 1b), it can output all internal IRQ requests to the Host. The output and polarity is configurable using REG[002Ah].                                                                                                                                                                                                                                                               |

#### 5.2.2 LCD Interface

For a pin mapping summary for each panel type, refer to Table 5-11:, "LCD Interface Pin Mapping for TFT Panels," on page 33.

Table 5-3: LCD Interface Pin Descriptions

| Pin Name    | Туре | QFP<br>Pin#           | Cell         | Power | RESET#<br>State | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|------|-----------------------|--------------|-------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FPDAT[17:0] | 0    | 53-56,<br>59-64,67-74 | OTLN4        | HVDD2 | L               | These output pins are Panel Data bits 17-0.  For a summary of pin usage for each panel type, see Section 5.5, "LCD Interface Pin Mapping" on page 33.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| FPFRAME     | 0    | 78                    | OTLN4        | HVDD2 | L               | This output pin is Frame Pulse for the LCD panel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| FPLINE      | 0    | 79                    | OTLN4        | HVDD2 | L               | This output pin is Line Pulse for the LCD panel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| FPSHIFT     | 0    | 77                    | OTLN4        | HVDD2 | L               | This output pin is Shift Clock for the LCD panel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| FPDRDY      | 0    | 80                    | OTLN4        | HVDD2 | L               | This output pin has the following function.  • Display Enable (DRDY) for TFT panels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| GPIOG4      | Ю    | 81                    | BLNCS4D<br>1 | HVDD2 | 0               | <ul> <li>This input/output pin has multiple functions.</li> <li>When REG[0C1Ah] bits 9-8 = 00b, this pin is configured as a general purpose input. (default)</li> <li>REG[0C1Ah] bits 9-8 = 01b is reserved and shouldn't be set to this value.</li> <li>When REG[0C1Ah] bits 9-8 = 10b, this pin is configured as a general purpose output.</li> <li>When REG[0C1Ah] bits 9-8 = 11b, this pin is used for TFT panels with a serial command interface (see Table 5-11:, "LCD Interface Pin Mapping for TFT Panels," on page 33).</li> <li>Note: This pin has an internal pull-down resistor that is controlled using REG[0468h] bit 4.</li> </ul> |

| GPIOG3      | Ю    | 82                    | BLNCS4D<br>1 | HVDD2 | 0               | <ul> <li>This input/output pin has multiple functions.</li> <li>When REG[0C1Ah] bits 7-6 = 00b, this pin is configured as a general purpose input. (default)</li> <li>REG[0C1Ah] bits 7-6 = 01b is reserved and shouldn't be set to this value.</li> <li>When REG[0C1Ah] bits 7-6 = 10b, this pin is configured as a general purpose output.</li> <li>When REG[0C1Ah] bits 7-6 = 11b, this pin is used for TFT panels with a serial command interface (see Table 5-11:, "LCD Interface Pin Mapping for TFT Panels," on page 33).</li> <li>Note: This pin has an internal pull-down resistor that is controlled using REG[0468h] bit 3.</li> </ul> |

Table 5-3: LCD Interface Pin Descriptions

| Pin Name | Туре | QFP<br>Pin# | Cell         | Power | RESET#<br>State | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|------|-------------|--------------|-------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOG2   | Ю    | 83          | BLNCS4D<br>1 | HVDD2 | 0               | <ul> <li>This input/output pin has multiple functions.</li> <li>When REG[0C1Ah] bits 5-4 = 00b, this pin is configured as a general purpose input. (default)</li> <li>REG[0C1Ah] bits 5-4 = 01b is reserved and shouldn't be set to this value.</li> <li>When REG[0C1Ah] bits 5-4 = 10b, this pin is configured as a general purpose output.</li> <li>When REG[0C1Ah] bits 5-4 = 11b, this pin is used for TFT panels with a serial command interface (see Table 5-11:, "LCD Interface Pin Mapping for TFT Panels," on page 33).</li> <li>Note: This pin has an internal pull-down resistor that is centralled using REC[0468h] bit 2.</li> </ul>                                                        |

| GPIOG1   | Ю    | 84          | BLNCS4D<br>1 | HVDD2 | 0               | <ul> <li>is controlled using REG[0468h] bit 2.</li> <li>This input/output pin has multiple functions.</li> <li>• When REG[0C1Ah] bits 3-2 = 00b, this pin is configured as a general purpose input. (default)</li> <li>• REG[0C1Ah] bits 3-2 = 01b is reserved and shouldn't be set to this value.</li> <li>• When REG[0C1Ah] bits 3-2 = 10b, this pin is configured as a general purpose output.</li> <li>• When REG[0C1Ah] bits 3-2 = 11b, this pin is used for TFT panels with a serial command interface (see Table 5-11:, "LCD Interface Pin Mapping for TFT Panels," on page 33).</li> <li>Note: This pin has an internal pull-down resistor that is controlled using REG[0468h] bit 1.</li> </ul> |

| GPIOG0   | Ю    | 85          | BLNCS4D<br>1 | HVDD2 | 0               | <ul> <li>This input/output pin has multiple functions.</li> <li>When REG[0C1Ah] bits 1-0 = 00b, this pin is configured as a general purpose input. (default)</li> <li>REG[0C1Ah] bits 1-0 = 01b is reserved and shouldn't be set to this value,.</li> <li>When REG[0C1Ah] bits 1-0 = 10b, this pin is configured as a general purpose output.</li> <li>When REG[0C1Ah] bits 1-0 = 11b, this pin is used for TFT panels with a serial command interface (see Table 5-11:, "LCD Interface Pin Mapping for TFT Panels," on page 33).</li> <li>Note: This pin has an internal pull-down resistor that is controlled using REG[0468h] bit 0.</li> </ul>                                                       |

#### 5.2.3 SDRAM Interface

Table 5-4: SDRAM Interface Pin Descriptions

| Pin Name    | Туре | QFP<br>Pin#                                 | Cell    | Power | RESET#<br>State | Description                                                                                           |

|-------------|------|---------------------------------------------|---------|-------|-----------------|-------------------------------------------------------------------------------------------------------|

| MEMA[11:0]  | 0    | 146-149,<br>176-183                         | OTLN4   | HVDD5 | L               | These output pins are used for SDRAM bank row/column address mapping.                                 |

| MEMBA[1:0]  | 0    | 144-145                                     | OTLN4   | HVDD5 | L               | These output pins are used to select the SDRAM Bank Address.                                          |

| MEMCS#      | 0    | 140                                         | OTLN4   | HVDD5 | Н               | This output pin is chip select for the SDRAM.                                                         |

| MEMRAS#     | 0    | 141                                         | OTLN4   | HVDD5 | Н               | This output pin is the RAS# for the SDRAM.                                                            |

| MEMCAS#     | 0    | 142                                         | OTLN4   | HVDD5 | Н               | This output pin is the CAS# for the SDRAM.                                                            |

| MEMWE#      | 0    | 143                                         | OTLN4   | HVDD5 | Н               | This output pin is write enable for the SDRAM.                                                        |

| MEMDQ[15:0] | Ю    | 152-155,<br>158-161,<br>164-167,<br>170-173 | BLNC4D2 | HVDD5 | 0               | These input/output pins are the data bus for the SDRAM. These pins have internal pull-down resistors. |

| MEMDQM[1:0] | 0    | 135-136                                     | OTLN4   | HVDD5 | L               | These output pins are the byte enables for the SDRAM.                                                 |

| MEMCLK      | 0    | 134                                         | OTLN8   | HVDD5 | Н               | This output pin is the clock for the SDRAM.                                                           |

| MEMCKE      | 0    | 137                                         | OTLN4   | HVDD5 | Н               | This output pin is the clock enable for the SDRAM.                                                    |

#### 5.2.4 GPIO / Multi Function Interface

The S1D13L04 supports many features using the general purpose IO pins. All GPIO pins can be configured, using REG[0C00h] ~ REG[0C1Ah], as an input, output, Non-GPIO function #1, or Non-GPIO function #2, if available. For summary of the functionality for all GPIO pins, see Section 5.6, "GPIO Pin Mapping" on page 34.

Table 5-5: GPIO / Multi Function Pin Descriptions

| Pin Name | Туре | QFP<br>Pin# | Cell         | Power | RESET#<br>State | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|------|-------------|--------------|-------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOA7   | Ю    | 87          | BLNCS4D<br>1 | HVDD3 | Z               | <ul> <li>This pin has multiple functions.</li> <li>When REG[0C02h] bits 15-14 = 00b, this pin is configured as a general purpose input. (default)</li> <li>When REG[0C02h] bits 15-14 = 01b, this pin is configured as the PWM Red output (PWMR).</li> <li>When REG[0C02h] bits 15-14 = 10b, this pin is configured as a general purpose output.</li> <li>REG[0C02h] bits 15-14 = 11b is reserved and shouldn't be set to this value.</li> <li>Note: The pull-down resistor on this pin is only active during test mode.</li> </ul>   |

| GPIOA6   | Ю    | 88          | BLNCS4D<br>1 | HVDD3 | Z               | <ul> <li>This pin has multiple functions.</li> <li>When REG[0C02h] bits 13-12 = 00b, this pin is configured as a general purpose input. (default)</li> <li>When REG[0C02h] bits 13-12 = 01b, this pin is configured as the PWM Green output (PWMG).</li> <li>When REG[0C02h] bits 13-12 = 10b, this pin is configured as a general purpose output.</li> <li>REG[0C02h] bits 13-12 = 11b is reserved and shouldn't be set to this value.</li> <li>Note: The pull-down resistor on this pin is only active during test mode.</li> </ul> |

| GPIOA5   | Ю    | 89          | BLNCS4D<br>1 | HVDD3 | Z               | <ul> <li>This pin has multiple functions.</li> <li>When REG[0C02h] bits 11-10 = 00b, this pin is configured as a general purpose input. (default)</li> <li>When REG[0C02h] bits 11-10 = 01b, this pin is configured as the PWM Blue output (PWMB).</li> <li>When REG[0C02h] bits 11-10 = 10b, this pin is configured as a general purpose output.</li> <li>REG[0C02h] bits 11-10 = 11b is reserved and shouldn't be set to this value.</li> <li>Note: The pull-down resistor on this pin is only active during test mode.</li> </ul>  |

Table 5-5: GPIO / Multi Function Pin Descriptions

| Pin Name | Туре | QFP<br>Pin# | Cell         | Power | RESET#<br>State | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|------|-------------|--------------|-------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOA4   | Ю    | 90          | BLNCS4D<br>1 | HVDD3 | Z               | <ul> <li>This pin has multiple functions.</li> <li>When REG[0C02h] bits 9-8 = 00b, this pin is configured as a general purpose input. (default)</li> <li>REG[0C02h] bits 9-8 = 01b is reserved and shouldn't be set to this value</li> <li>When REG[0C02h] bits 9-8 = 10b, this pin is configured as a general purpose output.</li> <li>REG[0C02h] bits 9-8 = 11b is reserved and shouldn't be set to this value.</li> <li>Note: The pull-down resistor on this pin is only active during test mode.</li> </ul>                       |

| GPIOB7   | Ю    | 93          | BLNCS4D<br>1 | HVDD3 | Z               | <ul> <li>This pin has multiple functions.</li> <li>When REG[0C06h] bits 15-14 = 00b, this pin is configured as a general purpose input. (default)</li> <li>When REG[0C06h] bits 15-14 = 01b, this pin is configured as the PWM White output (PWMW).</li> <li>When REG[0C06h] bits 15-14 = 10b, this pin is configured as a general purpose output.</li> <li>REG[0C06h] bits 15-14 = 11b is reserved and shouldn't be set to this value.</li> <li>Note: The pull-down resistor on this pin is only active during test mode.</li> </ul> |

| GPIOB6   | Ю    | 94          | BLNCS4D<br>1 | HVDD3 | Z               | <ul> <li>This pin has multiple functions.</li> <li>When REG[0C06h] bits 13-12 = 00b, this pin is configured as a general purpose input. (default)</li> <li>REG[0C06h] bits 13-12 = 01b is reserved and shouldn't be set to this value.</li> <li>When REG[0C06h] bits 13-12 = 10b, this pin is configured as a general purpose output.</li> <li>When REG[0C06h] bits 13-12 = 11b, this pin is reserved.</li> <li>Note: The pull-down resistor on this pin is only active during test mode.</li> </ul>                                  |

| GPIOB5   | Ю    | 95          | BLNCS4D<br>1 | HVDD3 | Z               | <ul> <li>This pin has multiple functions.</li> <li>When REG[0C06h] bits 11-10 = 00b, this pin is configured as a general purpose input. (default)</li> <li>REG[0C06h] bits 11-10 = 01b is reserved and shouldn't be set to this value.</li> <li>When REG[0C06h] bits 11-10 = 10b, this pin is configured as a general purpose output.</li> <li>When REG[0C06h] bits 11-10 = 11b, this pin is reserved.</li> <li>Note: The pull-down resistor on this pin is only active during test mode.</li> </ul>                                  |

Table 5-5: GPIO / Multi Function Pin Descriptions

| Pin Name   | Туре | QFP<br>Pin# | Cell         | Power | RESET#<br>State | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------|------|-------------|--------------|-------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOB4     | Ю    | 96          | BLNCS4D<br>1 | HVDD3 | Z               | <ul> <li>This pin has multiple functions.</li> <li>When REG[0C06h] bits 9-8 = 00b, this pin is configured as a general purpose input. (default)</li> <li>REG[0C06h] bits 9-8 = 01b is reserved and shouldn't be set to this value.</li> <li>When REG[0C06h] bits 9-8 = 10b, this pin is configured as a general purpose output.</li> <li>When REG[0C06h] bits 9-8 = 11b, this pin is reserved.</li> <li>Note: The pull-down resistor on this pin is only active during test mode.</li> </ul>                                                                                                                                                                                    |

| GPIOC[7:0] | Ю    | 107-114     | BLNCS4D<br>1 | HVDD4 | 0               | <ul> <li>These pins have multiple functions.</li> <li>When the appropriate bits from REG[0C0Ah] are set to 00b, the corresponding pins are configured as general purpose inputs. (default)</li> <li>Appropriate bits from REG[0C0Ah] bits 7-0 shouldn't be set to 01b because this setting is reserved.</li> <li>When the appropriate bits from REG[0C0Ah] are set to 10b, the corresponding pins are configured as general purpose outputs.</li> <li>Appropriate bits from REG[0C0Ah] bits 7-0 shouldn't be set to 11b because this setting is reserved.</li> <li>Note: These pins have internal pull-down resistors that are controlled using REG[046Ah] bits 7-0.</li> </ul> |

| GPIOD3     | Ю    | 115         | BLNCS4D<br>1 | HVDD4 | 0               | <ul> <li>This pin has multiple functions.</li> <li>When REG[0C0Eh] bits 7-6 = 00b, this pin is configured as a general purpose input. (default)</li> <li>REG[0C0Eh] bits 7-6 = 01b this pin is configured as the Digital audio input for PWM circuit (AUDIN).</li> <li>When REG[0C0Eh] bits 7-6 = 10b, this pin is configured as a general purpose output.</li> <li>REG[0C0Eh] bits 7-6 = 11b is reserved and shouldn't be set to this value.</li> <li>Note: This pin has an internal pull-down resistor that is controlled using REG[0464h] bit 11.</li> </ul>                                                                                                                 |

Table 5-5: GPIO / Multi Function Pin Descriptions

| Pin Name | Туре | QFP<br>Pin# | Cell         | Power | RESET#<br>State | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|------|-------------|--------------|-------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOD2   | Ю    | 116         | BLNCS4D<br>1 | HVDD4 | 0               | <ul> <li>This pin has multiple functions.</li> <li>When REG[0C0Eh] bits 5-4 = 00b, this pin is configured as a general purpose input. (default)</li> <li>REG[0C0Eh] bits 5-4 = 01b is reserved and shouldn't be set to this value.</li> <li>When REG[0C0Eh] bits 5-4 = 10b, this pin is configured as a general purpose output.</li> <li>REG[0C0Eh] bits 5-4 = 11b is reserved and shouldn't be set to this value.</li> <li>Note: This pin has an internal pull-down resistor that is controlled using REG[0464h] bit 10.</li> </ul> |

| GPIOD1   | Ю    | 117         | BLNCS4D<br>1 | HVDD4 | 0               | <ul> <li>This pin has multiple functions.</li> <li>When REG[0C0Eh] bits 3-2 = 00b, this pin is configured as a general purpose input. (default)</li> <li>REG[0C0Eh] bits 3-2 = 01b is reserved and shouldn't be set to this value.</li> <li>When REG[0C0Eh] bits 3-2 = 10b, this pin is configured as a general purpose output.</li> <li>REG[0C0Eh] bits 3-2 = 11b is reserved and shouldn't be set to this value.</li> <li>Note: This pin has an internal pull-down resistor that is controlled using REG[0464h] bit 9.</li> </ul>  |

| GPIOD0   | Ю    | 118         | BLNCS4D<br>1 | HVDD4 | 0               | <ul> <li>This pin has multiple functions.</li> <li>When REG[0C0Eh] bits 1-0 = 00b, this pin is configured as a general purpose input. (default)</li> <li>REG[0C0Eh] bits 1-0 = 01b is reserved and shouldn't be set to this value.</li> <li>When REG[0C0Eh] bits 1-0 = 10b, this pin is configured as a general purpose output.</li> <li>REG[0C0Eh] bits 1-0 = 11b is reserved and shouldn't be set to this value.</li> <li>Note: This pin has an internal pull-down resistor that is controlled using REG[0464h] bit 8.</li> </ul>  |

#### 5.2.5 Miscellaneous

Table 5-6: Miscellaneous Pin Descriptions

| Pin Name | Туре | QFP<br>Pin# | Cell  | Power       | RESET#<br>State | Description                                                                                                                                                                                                                                                                                                                               |

|----------|------|-------------|-------|-------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CNF[8:0] | ı    | 122-130     | ICD2  | HVDD4       | 0               | These inputs are used to configure the S1D13L04 and must be connected to IOVDD or VSS. The states of these pins are latched at RESET#. These pins have internal pull-down resistors which can be disabled by software after reset (see REG[046Eh]). For more information, see Section 5.3, "Summary of Configuration Options" on page 29. |

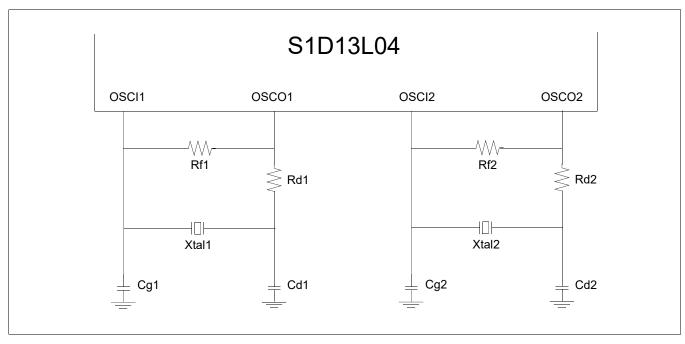

| OSCI1    | 1    | 40          | ILTR  | OSCVD<br>D1 | 0/1             | Crystal input. If an external Oscillator circuit or clock generator is used, connect it to this pin. For details on the clock structure, see Section Chapter 9, "Clocks" on page 69.                                                                                                                                                      |

| OSCO1    | 0    | 41          | OLTR  | OSCVD<br>D1 | Н               | Crystal output. If an external Oscillator is used, this pin should be left unconnected. For details on the clock structure, see Section Chapter 9, "Clocks" on page 69.                                                                                                                                                                   |

| OSCI2    | I    | 45          | ILTR  | OSCVD<br>D2 | 0/1             | Crystal input. If an external Oscillator circuit or clock generator is used, connect it to this pin. For details on the clock structure, see Section Chapter 9, "Clocks" on page 69.                                                                                                                                                      |

| OSCO2    | 0    | 44          | OLTR  | OSCVD<br>D2 | Н               | Crystal output. If an external Oscillator is used, this pin should be left unconnected. For details on the clock structure, see Section Chapter 9, "Clocks" on page 69.                                                                                                                                                                   |

| CLKI3    | I    | 36          | IC    | HVDD1       | 0/1             | Clock input. Typically, this input is used for the SDRAM clock through PLL1. When it is not used, it should be connected to VSS.                                                                                                                                                                                                          |

| TESTEN   | ı    | 121         | ICSD1 | HVDD4       | 0               | This input pin is for production test only and should be left unconnected for normal operation.                                                                                                                                                                                                                                           |

| VCP1     | 0    | 48          | OLTR  | PLLVDD<br>1 | Z               | This output is for production test only and should be left unconnected for normal operation.                                                                                                                                                                                                                                              |

| VCP2     | 0    | 51          | OLTR  | PLLVDD<br>2 | Z               | This output is for production test only and should be left unconnected for normal operation.                                                                                                                                                                                                                                              |

| TCK      | I    | 100         | ICSP1 | HVDD4       | 1               | JTAG Interface pin for Boundary Scan test.                                                                                                                                                                                                                                                                                                |

| TMS      | ı    | 101         | ICSP1 | HVDD4       | 1               | JTAG Interface pin for Boundary Scan test.                                                                                                                                                                                                                                                                                                |

| TDI      | I    | 102         | ICSP1 | HVDD4       | 1               | JTAG Interface pin for Boundary Scan test.                                                                                                                                                                                                                                                                                                |

| TDO      | 0    | 103         | OTLN4 | HVDD4       | L               | JTAG Interface pin for Boundary Scan test                                                                                                                                                                                                                                                                                                 |

| TRST     | I    | 104         | ICSP2 | HVDD4       | 1               | JTAG Interface pin for Boundary Scan test. For normal operations, this pin must be tied to VSS or connected to RESET#.                                                                                                                                                                                                                    |

#### 5.2.6 Power And Ground

Table 5-7: Power And Ground Pin Descriptions

| Pin Name | Туре | QFP<br>Pin#                                                                             | Cell | RESET#<br>State | Description                   |

|----------|------|-----------------------------------------------------------------------------------------|------|-----------------|-------------------------------|

| COREVDD  | Р    | 29,37,86,97,<br>131,156,<br>157,208                                                     | Р    | _               | Core VDD                      |

| HVDD1    | Р    | 9,19,196                                                                                | Р    | _               | IOVDD for HOST interface      |

| HVDD2    | Р    | 57,65,75                                                                                | Р    | _               | IOVDD for LCD Panel interface |

| HVDD3    | Р    | 91                                                                                      | Р    | _               | IOVDD for GPIO                |

| HVDD4    | Р    | 98,105,119                                                                              | Р    | _               | IOVDD for GPIO, etc.          |

| HVDD5    | Р    | 132,138,<br>150,162,<br>168,174                                                         | Р    | _               | IOVDD for SDRAM interface     |

| VSS      | Р    | 10,20,38,58,<br>66,76,92,99,<br>106,120,<br>133,139,<br>151,163,<br>169,175,<br>184,197 | Р    | _               | Common Ground                 |

| OSCVDD1  | Р    | 39                                                                                      | Р    | _               | VDD for OSC1                  |

| OSCVSS1  | Р    | 42                                                                                      | Р    | _               | GND for OSC1                  |

| OSCVDD2  | Р    | 46                                                                                      | Р    | _               | VDD for OSC2                  |

| OSCVSS2  | Р    | 43                                                                                      | Р    | _               | GND for OSC2                  |

| PLLVDD1  | Р    | 49                                                                                      | Р    | _               | Analog VDD for PLL1           |

| PLLVSS1  | Р    | 47                                                                                      | Р    | _               | Analog GND for PLL1           |

| PLLVDD2  | Р    | 50                                                                                      | Р    | _               | Analog VDD for PLL2           |

| PLLVSS2  | Р    | 52                                                                                      | Р    | _               | Analog GND for PLL2           |

#### 5.3 Summary of Configuration Options

These pins are used for configuration of the S1D13L04 and must be connected using an external pull-up resistor (1) or left open (0) where an internal pull-down resistor is used. The state of CNF[8:0] has an effect only at the rising edge of RESET#. Changing state at any other time has no effect. In order to stop the constant current when an external pull-up resistor is used, disable the corresponding pull-down resistor (see REG[046Eh]).

#### Note

The CNF pins select the host bus interface and determine whether the interface is Little or Big Endian.

When a Big Endian host interface is selected, the registers must be accessed using a method which "byte-swaps" the upper and lower data byte in each register. For details on this requirement, see Section 16.6, "Register Accesses for Big Endian Host Interfaces" on page 198.

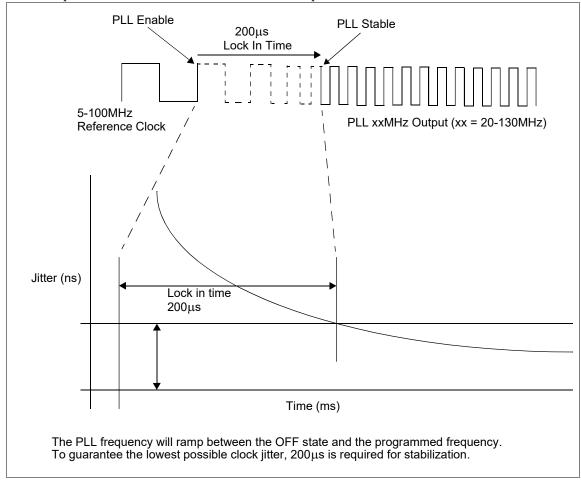

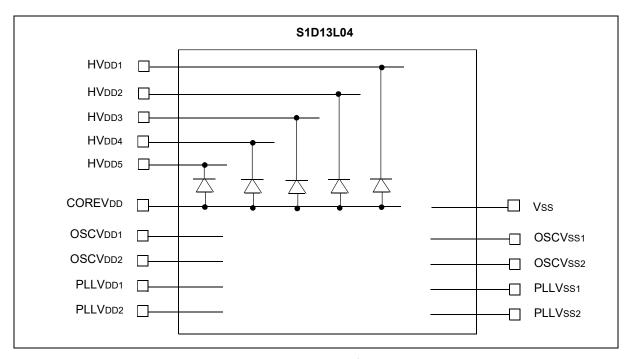

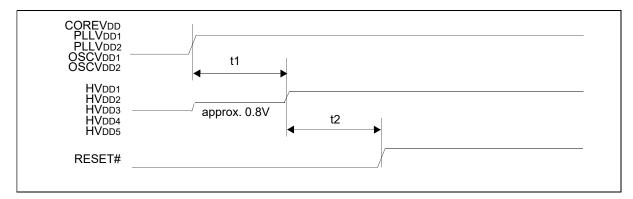

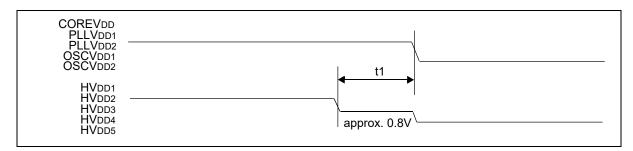

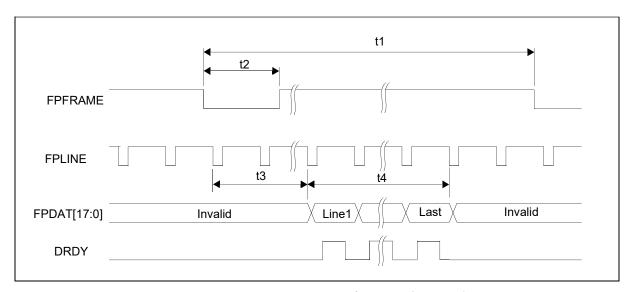

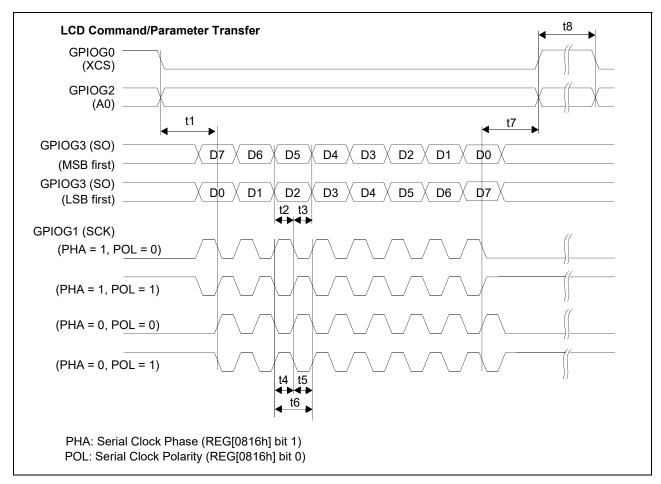

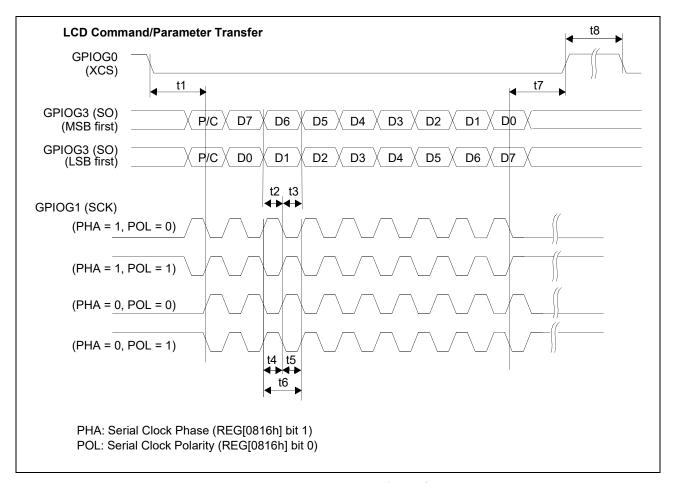

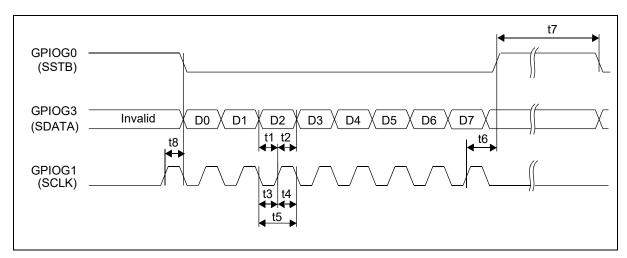

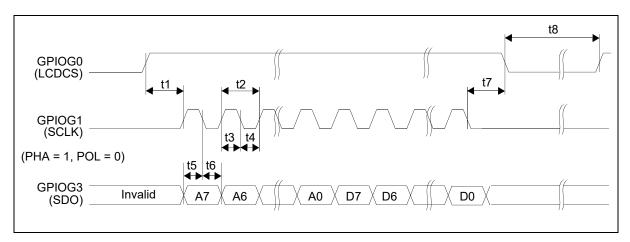

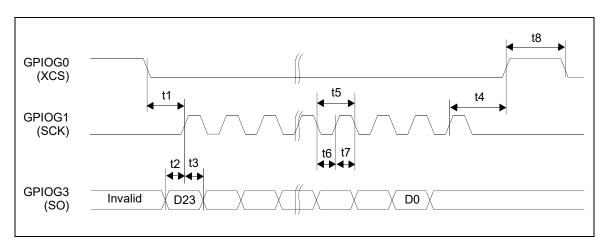

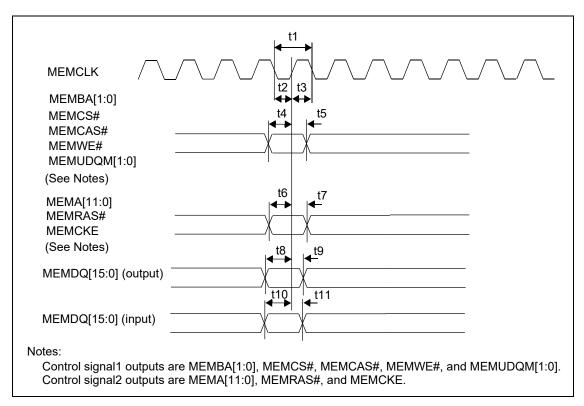

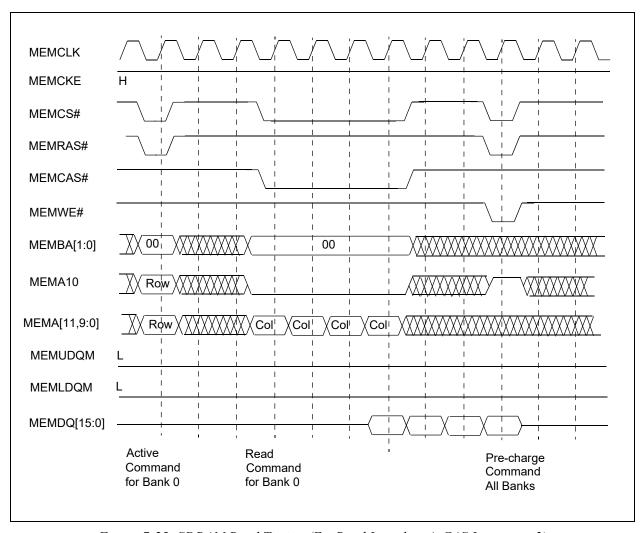

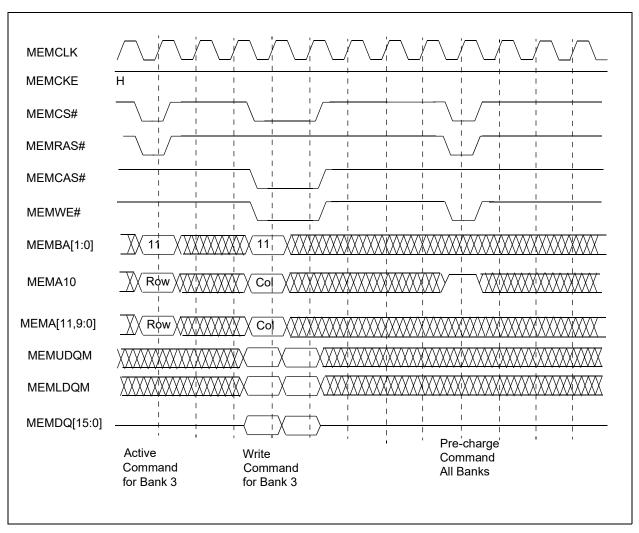

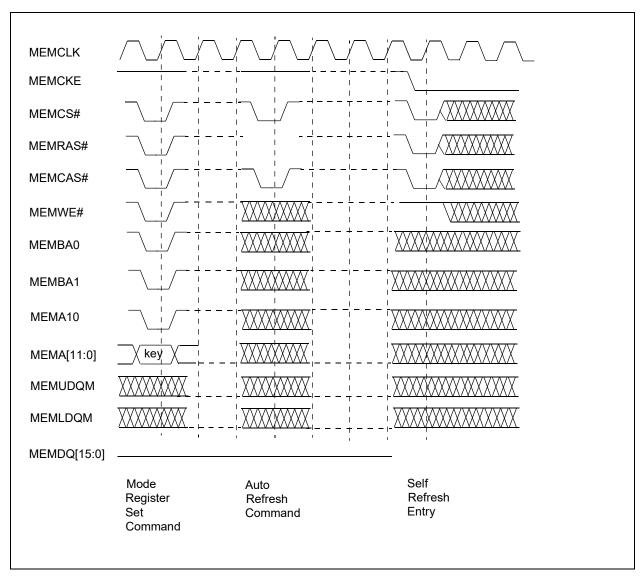

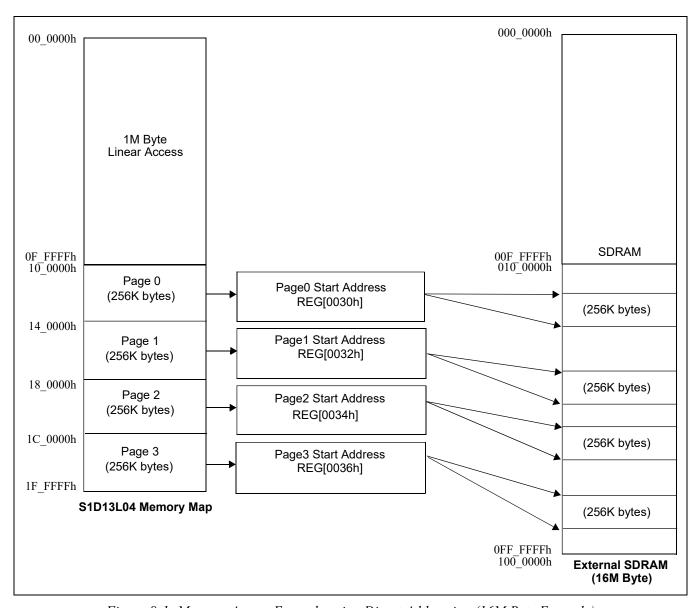

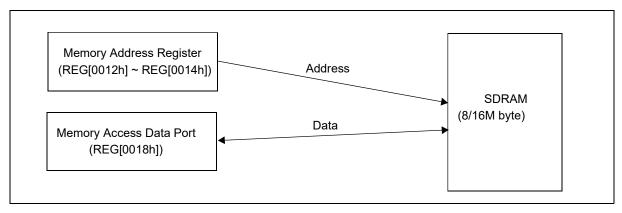

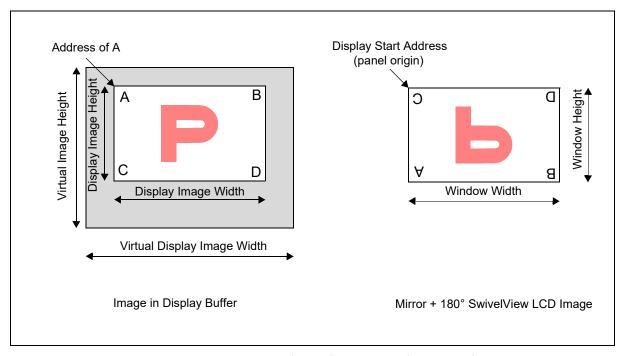

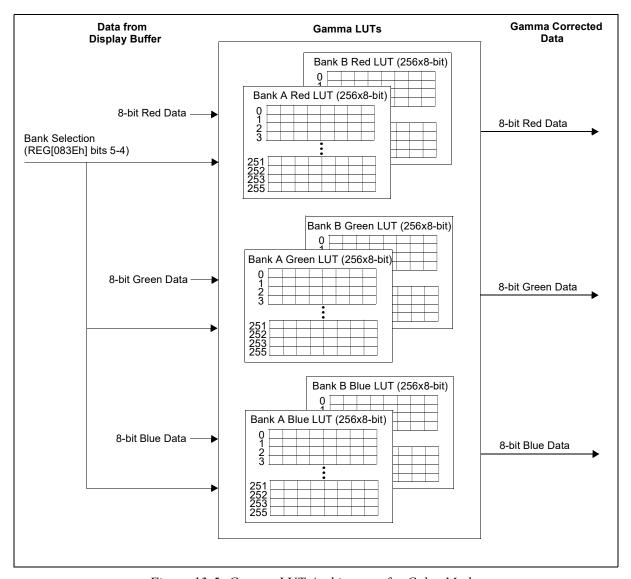

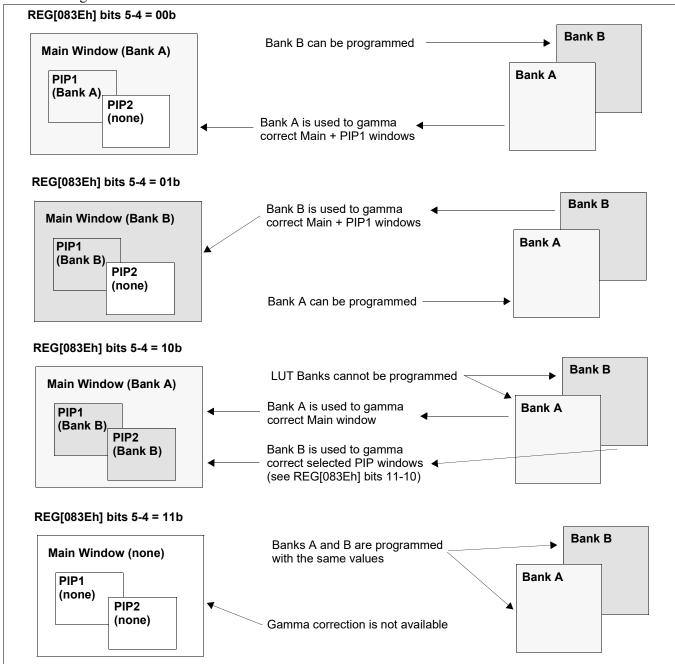

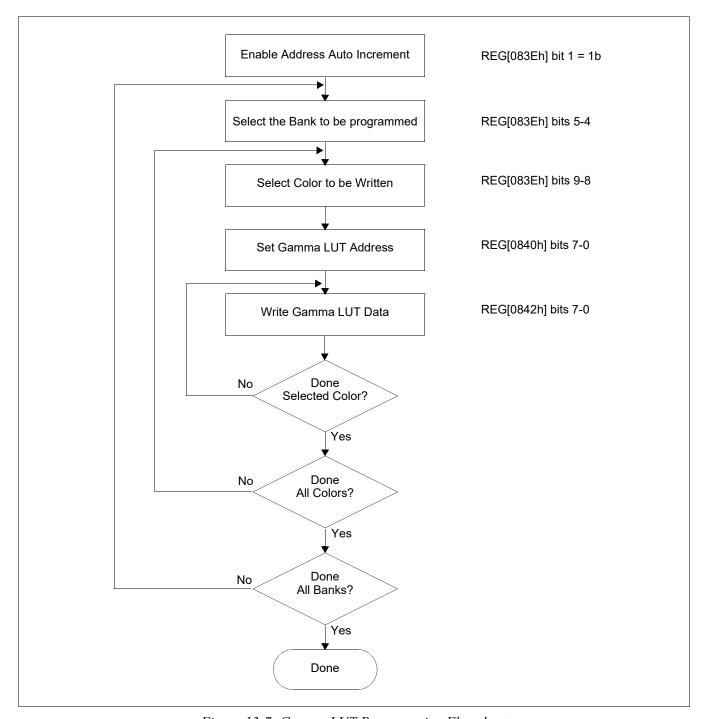

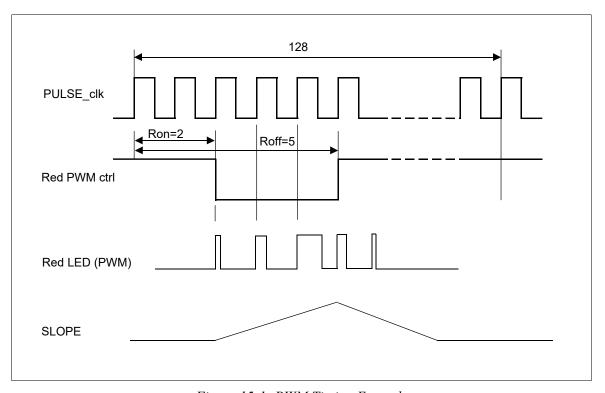

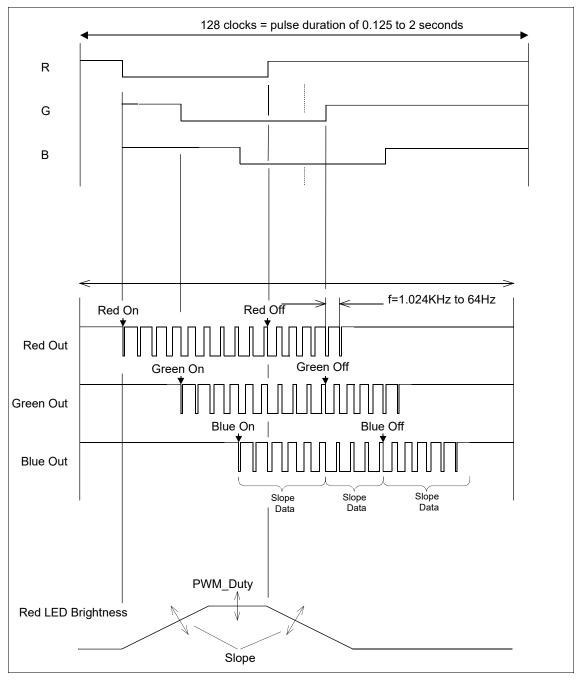

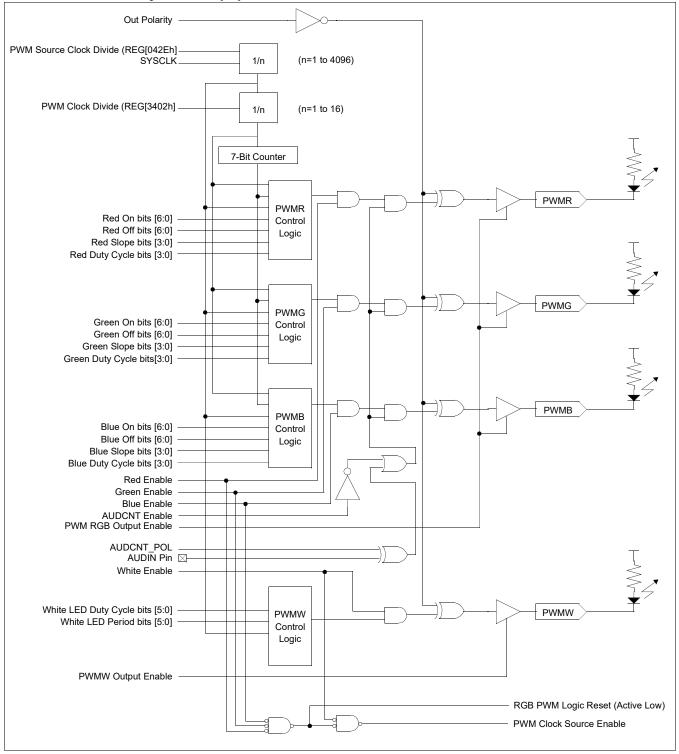

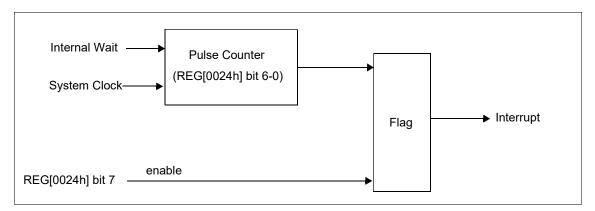

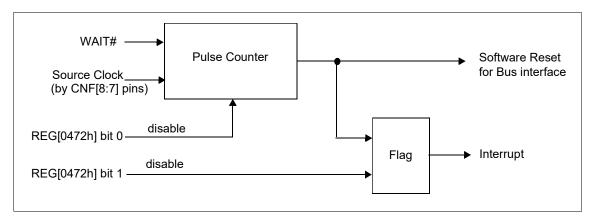

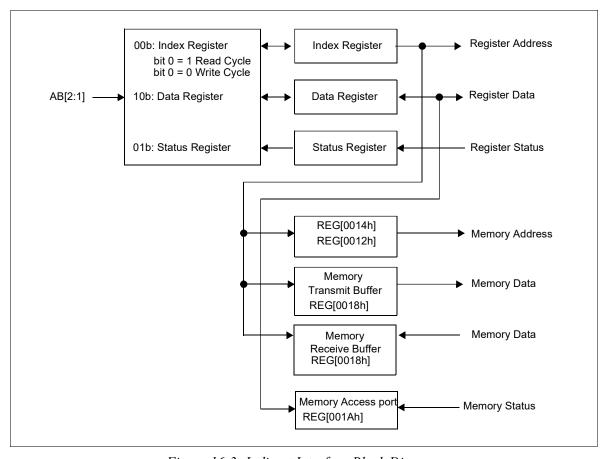

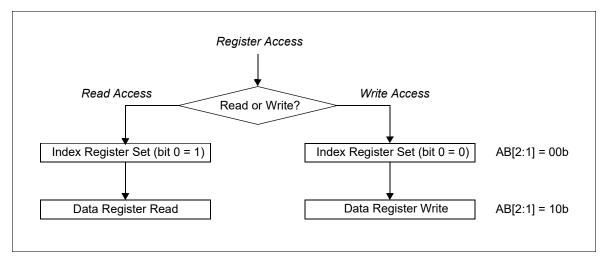

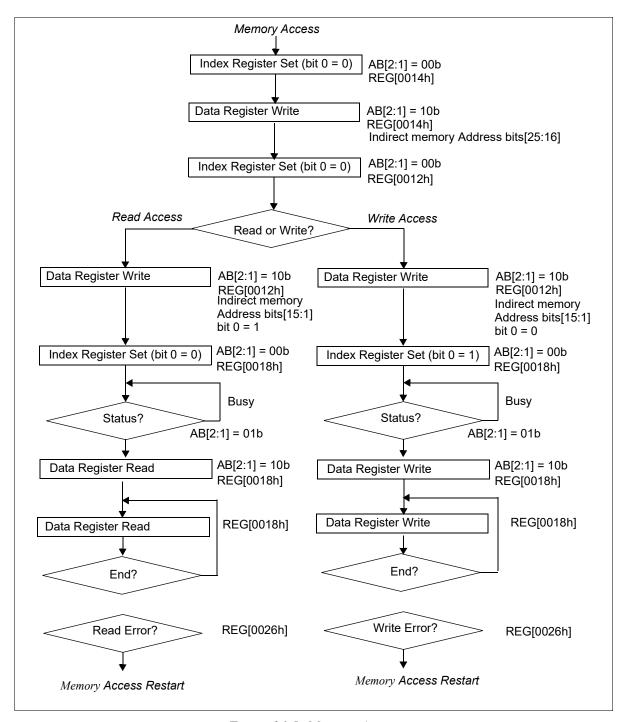

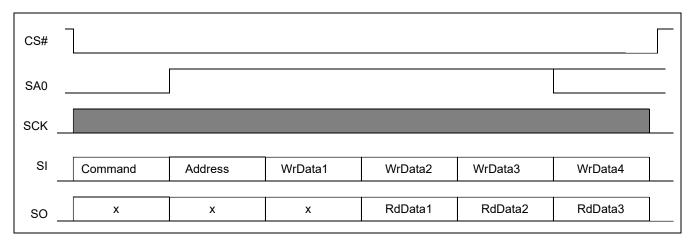

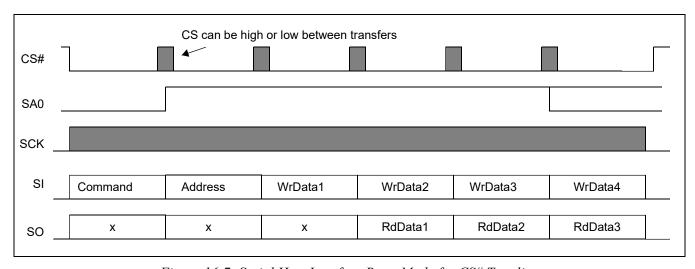

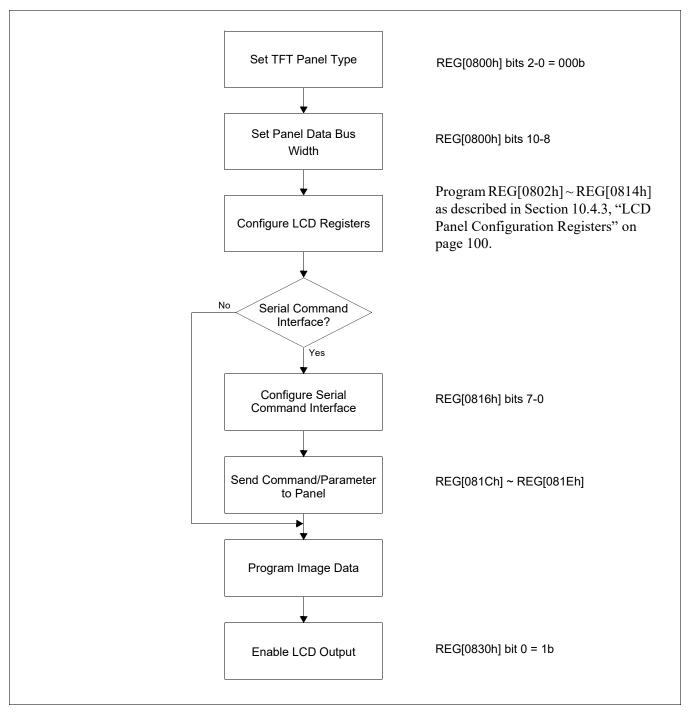

Table 5-8: Summary of Power-On/Reset Options for CNF6=1