RF Transmitter IC S1S77100 Data Sheet

SEIKO EPSON CORPORATION

# **Table of Contents**

| 1. | Ov                   | /erview                                        | 1  |  |  |  |

|----|----------------------|------------------------------------------------|----|--|--|--|

| 2. | Block Diagram2       |                                                |    |  |  |  |

| 3. | Pir                  | n Assignments                                  | 3  |  |  |  |

| 4. | Pir                  | n Descriptions                                 | 4  |  |  |  |

| 5. | Ele                  | ectrical Characteristics                       | 5  |  |  |  |

| 5  | 5.1.                 | Absolute Maximum Rating                        | .5 |  |  |  |

| 5  | 5.2.                 | DC Characteristics                             |    |  |  |  |

| 5  | 5.3.                 | AC Characteristics                             | .7 |  |  |  |

| 6. | Fu                   | nction Description                             | 11 |  |  |  |

| 6  | 5.1.                 | Outline                                        |    |  |  |  |

| 6  | 5.2.                 | SPI Interface                                  |    |  |  |  |

|    | 6.2.                 | 0                                              |    |  |  |  |

|    | 6.2.                 |                                                |    |  |  |  |

|    | 6.2.                 |                                                |    |  |  |  |

|    | 6.2.                 |                                                |    |  |  |  |

| 6  | 5.3.                 | 1 8                                            |    |  |  |  |

|    | 6.3.<br>6.3.         |                                                |    |  |  |  |

| 6  |                      |                                                |    |  |  |  |

| 0  | 5 <b>.4.</b><br>6.4. |                                                |    |  |  |  |

| 6  | 5.5.                 |                                                |    |  |  |  |

| 0  | . <b></b><br>6.5.    |                                                |    |  |  |  |

|    | 6.5.                 |                                                |    |  |  |  |

| 6  | 6.6.                 |                                                |    |  |  |  |

| U  | 6.6.                 | 1 8                                            |    |  |  |  |

|    | 6.6.                 |                                                |    |  |  |  |

|    | 6.6.                 | 3. Antenna tuning                              | 27 |  |  |  |

| 6  | 5.7.                 | Fail-safe Function                             | 28 |  |  |  |

|    | 6.7.                 | .1. PLL Loss of Lock detection                 | 28 |  |  |  |

|    | 6.7.                 |                                                |    |  |  |  |

|    | 6.7.                 | 6                                              |    |  |  |  |

| 6  |                      | Clock Output (CKOUT) Function                  |    |  |  |  |

|    | 6.8.                 |                                                |    |  |  |  |

|    | 6.8.<br>6.8.         |                                                |    |  |  |  |

|    |                      | 1                                              |    |  |  |  |

| 0  | 5 <b>.9.</b><br>6.9. | Status Monitor                                 |    |  |  |  |

|    | 6.9.                 |                                                |    |  |  |  |

| -  |                      |                                                |    |  |  |  |

| 7. |                      | R (Special Function Register)                  |    |  |  |  |

|    | .1.                  | SFR List                                       |    |  |  |  |

|    | .2.                  | PLL Fractional Setting: Frequency Channel 1    |    |  |  |  |

| 7  | .3.                  | PLL Fractional Setting: Frequency Channel 2    |    |  |  |  |

| 7  | .4.                  | PLL Integer Setting: Frequency Channel 1 and 2 | 34 |  |  |  |

| 7  | .5.                  | PLL Fractional Setting: Frequency Channel 3    | 35 |  |  |  |

| 7  | .6.                  | PLL Fractional Setting: Frequency Channel 4    | 35 |  |  |  |

# S1S77100 Data Sheet Rev1.0

# **EPSON**

| 7.7.  | PLL Integer Setting: Frequency Channel 3 and 4                                     | 35 |

|-------|------------------------------------------------------------------------------------|----|

| 7.8.  | FSK Deviation Setting, Output Divider Setting, and CKOUT Slew Rate Control Setting | 36 |

| 7.9.  | FSK Deviation Setting                                                              | 36 |

| 7.10. | ASK Modulation Control 0                                                           | 37 |

| 7.11. | ASK Modulation Control 1                                                           | 37 |

| 7.12. | ASK Modulation Control 2                                                           | 38 |

| 7.13. | Soft-ASK Modulation Setting                                                        | 38 |

|       | Soft-FSK Modulation Setting                                                        |    |

|       | CKOUT / Bitrate Signal Divider Setting 1                                           |    |

| 7.16. | CKOUT / Bitrate Signal Divider Setting 2                                           | 40 |

| 7.17. | Under Voltage Detection / Antenna Tuning Setting                                   | 41 |

|       | Error Detection Status                                                             |    |

| 7.19. | Transmitter Control                                                                | 43 |

| 7.20. | SPI Checksum                                                                       | 44 |

| 8. Di | mensions                                                                           | 45 |

|       | oplication Note                                                                    |    |

|       |                                                                                    |    |

# 1. Overview

RF transmitter IC S1S77100 is a wireless transmitter IC for the UHF range. This IC houses a PLL and a Power Amp in a 4 mm x 4 mm SQFN package. The S1S77100 can be configured in combination with an external crystal oscillator. So, it is suitable for small wireless devices.

- Output frequency range: 300 MHz to 465 MHz (0.25 kHz Step), 600 MHz to 930 MHz (0.49 kHz Step)

- $\Delta$ - $\Sigma$  fractional-N PLL

- Programmable power amplifier (PA) output power: -15 dBm to 1dBm, -5 dBm to 11 dBm for each 64 steps

- Modulation types: ASK/OOK/FSK with Soft-ASK and/or Soft FSK shaping.

- Multi-channel (up to 4 channels), channel hopping capability

- 3-wire/4-wire SPI interface for Special Function Register (SFR)

- SFR (Special Function Register)

- Fail-safe mechanism (PLL Loss of Lock: LOL, VCO auto-calibration error, Under Voltage Detection: UVD)

- External 32 MHz crystal oscillator by clipped sine input

- Synchronous transmission mode with input clock

- Dividing clock output via CKOUT

- Programmable voltage threshold of Under Voltage Detection (UVD): 4 step (1.8 V to 2.4 V)

- 24-pin 4 mm x 4 mm SQFN (Saw Quad Flat Non-leaded) package

- Supply voltage 1.8 V to 3.6 V

- Operating temperature:  $-40^{\circ}$ C to  $+85^{\circ}$ C

- Pb-free/RoHS-compliant

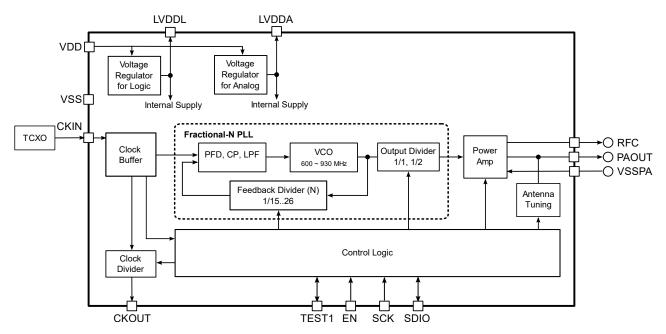

# 2. Block Diagram

Figure 2.1 S1S77100 Block Diagram

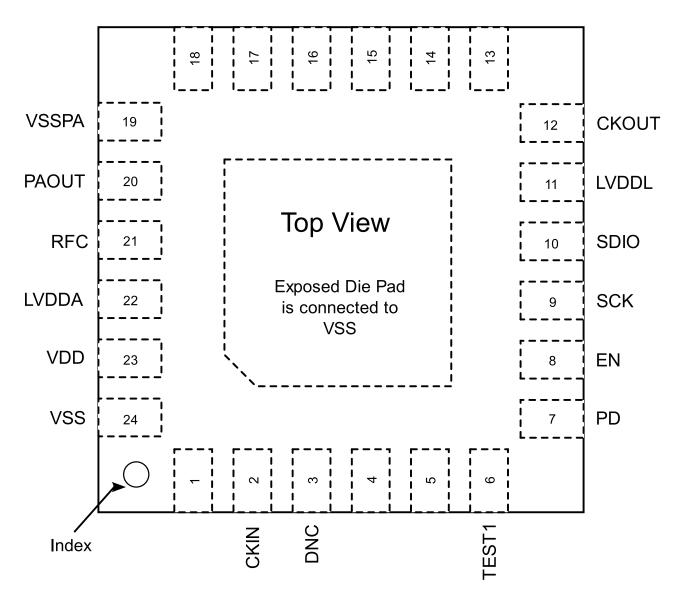

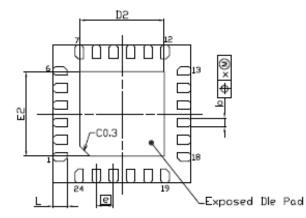

# 3. Pin Assignments

Package type: SQFN 4

\* Pins without names (1, 4, 5, 13 to 18) are NC (no wire connection to the built-in IC).

\* When soldering the EDP (Exposed Die Pad) to the mounting board, connect it to a wire with the same power as VSS.

# 4. Pin Descriptions

# Table 4.1 Pin Descriptions

| No. | Pin Name | Туре         |           | Function                                                           |

|-----|----------|--------------|-----------|--------------------------------------------------------------------|

| 1   | NC       |              |           | Unconnected pin, connected to VSS for power stabilization          |

| 2   | CKIN     | Input        | -         | Crystal oscillator input, direct connected to clipped sine output  |

| 3   | DNC      | Input/Output | -         | Our test pin, must be unconnected, prohibit VSS connection         |

| 4   | NC       | -            | -         | Unconnected pin, connected to VSS for power stabilization          |

| 5   | NC       | -            | -         | Unconnected pin, connected to VSS for power stabilization          |

| 6   | TEST1    | Input/Output | Pull-down | Test pin/ TxDATA input / SPI interface pin                         |

|     |          |              |           | Leave floating and make no external connections to this pin if the |

|     |          |              |           | function of this pin is unused.                                    |

| 7   | PD       | Input        | Pull-down | Our test pin, connected to VSS for noise countermeasures           |

| 8   | EN       | Input        | Pull-down | Enable input, SPI interface pin                                    |

| 9   | SCK      | Input        | Pull-down | SPI clock input                                                    |

| 10  | SDIO     | Input/Output | Pull-down | SPI data input/output                                              |

| 11  | LVDDL    | Output       | -         | Built-in power supply monitor pin for digital circuits             |

|     |          | -            |           | When connecting a bypass capacitor, it should be 1000pF or less    |

| 12  | CKOUT    | Output       | -         | Clock output                                                       |

| 13  | NC       | -            | -         | Unconnected pin, connected to VSS for power stabilization          |

| 14  | NC       | -            | -         | Unconnected pin, connected to VSS for power stabilization          |

| 15  | NC       | -            | -         | Unconnected pin, connected to VSS for power stabilization          |

| 16  | NC       | -            | -         | Unconnected pin, connected to VSS for power stabilization          |

| 17  | NC       | -            | -         | Unconnected pin, connected to VSS for power stabilization          |

| 18  | NC       | -            | -         | Unconnected pin, connected to VSS for power stabilization          |

| 19  | VSSPA    | Power        | -         | GND for PA                                                         |

| 20  | PAOUT    | Output       | -         | Power Amp output                                                   |

| 21  | RFC      | Output       | -         | RF choke coil                                                      |

| 22  | LVDDA    | Output       | -         | Built-in power supply monitor pin for analog circuits              |

|     |          | _            |           | When connecting a bypass capacitor, it should be 1000pF or less.   |

| 23  | VDD      | Power        | -         | Positive power supply                                              |

| 24  | VSS      | Power        | -         | GND                                                                |

| EDP | VSS      | Power        | -         | GND                                                                |

\*EDP: Exposed Die Pad

# 5. Electrical Characteristics

# 5.1. Absolute Maximum Rating

| Idama               | C11                                          |                            |         | Standard |           |      |  |

|---------------------|----------------------------------------------|----------------------------|---------|----------|-----------|------|--|

| Item                | Symbol                                       | Condition                  | Min.    | Тур.     | Max.      | Unit |  |

| Supply voltage      | VDD                                          | VSS = 0 V                  | -0.3    | -        | 4.0       | V    |  |

| Input voltage       | V <sub>in1</sub>                             | VSS = 0 V, except CKIN pin | VSS-0.3 | -        | VDD + 0.3 | V    |  |

|                     | V <sub>in2</sub>                             | VSS = 0 V, CKIN pin        | VSS-0.3 | -        | 1.8       | V    |  |

| Storage temperature | brage temperature Tstg Store as bare product |                            | -40     | -        | +125      | °C   |  |

# Table 5.1 Absolute Maximum Rating

# 5.2. DC Characteristics

# Table 5.2 Power Supply, Operating Temperature

|                                     |             |                                                                  | VSS           | = 0 V, Ta = | = -40°C to | +85°C |  |  |

|-------------------------------------|-------------|------------------------------------------------------------------|---------------|-------------|------------|-------|--|--|

| T4                                  | Symbol      | mbol Condition                                                   |               | Standard    |            |       |  |  |

|                                     |             | Condition                                                        | Min.          | Тур.        | Max.       | Unit  |  |  |

| Supply voltage                      | VDD         | -                                                                | 1.8           | 3.0         | 3.6        | V     |  |  |

| Supply current Powerdown            | Iddpd       | VDD = 3.0 V, Ta = 25°C                                           | -             | 20          | 100        | nA    |  |  |

| Mode                                |             | $VDD = 3.6 V, Ta = 85 °C^{*1}$                                   | -             | -           | 900        | -     |  |  |

| Supply current<br>CKBUF-Active Mode | Iddat       | -                                                                | -             | 860         | 1100       | μΑ    |  |  |

| Supply current PLL-Active           | Iddpll      | F <sub>TX</sub> = 315 MHz, F <sub>PLL</sub> = 630 MHz            | -             | 2.2         | 2.5        | mA    |  |  |

| Mode                                |             | $F_{TX} = 915 \text{ MHz}, F_{PLL} = 915 \text{ MHz}^{*1}$       | -             | 2.5         | 2.8        | mA    |  |  |

| Supply current                      | Iddtma      | $F_{TX} = 315$ MHz, HPWR = 1, PADUTY = 1                         | 0b            |             |            |       |  |  |

| Transmitter-Active Mode             |             | Pout = 5 dBm, $AM^* = 0x1A^{*1}$                                 | -             | 10.0        | 11.0       |       |  |  |

|                                     |             | Pout = 8 dBm, $AM^* = 0x29^{*1}$                                 | -             | 12.7        | 13.7       | mA    |  |  |

|                                     |             | Pout = $10 \text{ dBm}$ , AM* = $0x36$                           | -             | 15.0        | 16.0       |       |  |  |

|                                     |             | $F_{TX} = 433MHz$ , $HPWR = 1$ , $PADUTY = 10b$                  |               |             |            |       |  |  |

|                                     |             | Pout = 5 dBm, $AM^* = 0x16^{*1}$                                 | -             | 10          | 11         |       |  |  |

|                                     |             | Pout = 8 dBm, $AM^* = 0x24^{*1}$                                 | -             | 12.5        | 13.5       | mA    |  |  |

|                                     |             | Pout = 10 dBm, $AM^* = 0x30^{*1}$                                | -             | 14.5        | 15.5       |       |  |  |

|                                     |             | $F_{TX} = 868 \text{ MHz}, \text{HPWR} = 1, \text{PADUTY} = 01b$ |               |             |            |       |  |  |

|                                     |             | Pout = 5 dBm, $AM^* = 0x19^{*1}$                                 | -             | 11.7        | 12.7       |       |  |  |

|                                     |             | Pout = 8 dBm, $AM^* = 0x28^{*1}$                                 | -             | 14.4        | 15.4       | mA    |  |  |

|                                     |             | Pout = 10 dBm, $AM^* = 0x35^{*1}$                                | -             | 16.5        | 17.5       |       |  |  |

|                                     |             | $F_{TX} = 915$ MHz, HPWR = 1, PADUTY = 01b                       |               |             |            |       |  |  |

|                                     |             | Pout = 5 dBm, $AM^* = 0x19^{*1}$                                 | -             | 11.8        | 12.8       |       |  |  |

|                                     |             | Pout = 8 dBm, $AM^* = 0x27^{*1}$                                 | -             | 14.4        | 15.4       | mA    |  |  |

|                                     |             | Pout = 10 dBm, $AM^* = 0x34^{*1}$                                | -             | 16.5        | 17.5       |       |  |  |

| CKOUT clock output                  | IDDCK       | Load capacitance is 15 pF                                        |               |             |            |       |  |  |

| current                             |             | SR = 11b, $F_{CKOUT}$ = 32 MHz <sup>*1</sup>                     | -             | -           | 3.0        |       |  |  |

|                                     |             | SR = 00b, $F_{CKOUT}$ = 2 MHz <sup>*1</sup>                      | -             | -           | 0.3        | mA    |  |  |

| Operating temperature*1             | Та          | -                                                                | -40           | -           | +85        | °C    |  |  |

| *1 Guaranteed by design, ch         | naracteriza | tion, and/or simulation only and not by proc                     | luction test. |             |            |       |  |  |

# Table 5.3 Logic I/O, CLK input

|                                  |                  | VDD = 1.8 V  to  3.6 V                                                                                                                                                                                       | v, v bb v | Standard | -+0 C 10 + | 05 0 |

|----------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|------------|------|

| Item                             | Symbol           | Condition                                                                                                                                                                                                    | Min.      |          | Max.       | Unit |

| TT: -1- 11 : 14                  | V                | EN COV SDIO TESTI                                                                                                                                                                                            |           | Тур.     |            | V    |

| High level input voltage         | VIH              | EN, SCK, SDIO, TEST1                                                                                                                                                                                         | VDD x 0.8 | -        | VDD + 0.3  |      |

| Low level input voltage          | VIL              | EN, SCK, SDIO, TEST1                                                                                                                                                                                         | -0.3      | -        | VDD x 0.2  | V    |

| Input clock voltage<br>amplitude | V <sub>CLK</sub> | Peak-Peak voltage amplitude of the signal input to CKIN                                                                                                                                                      | 0.5       | -        | 1.5        | V    |

| *                                | V <sub>OH1</sub> | SDIO, TEST1, Io = -0.4 mA                                                                                                                                                                                    | VDD x 0.9 | -        | -          | V    |

| High level output voltage        | V <sub>OH2</sub> | CKOUT,<br>If the SR = 11b is set, Io = $-1 \text{ mA}$<br>If the SR = 10b is set, Io = $-0.7 \text{ mA}$<br>If the SR = 01b is set, Io = $-0.5 \text{ mA}$<br>If the SR = 00b is set, Io = $-0.2 \text{ mA}$ | VDD x 0.9 | -        | -          | V    |

|                                  | Vol1             | SDIO, TEST1 (4-wire SPI mode),<br>Io = 0.4 mA                                                                                                                                                                | -         | -        | VDD x 0.1  | V    |

| Low level output voltage         | V <sub>OL2</sub> | CKOUT,<br>If the SR = 11b is set, Io = 1 mA<br>If the SR = 10b is set, Io = $0.7 \text{ mA}$<br>If the SR = 01b is set, Io = $0.5 \text{ mA}$<br>If the SR = 00b is set, Io = $0.2 \text{ mA}$               | -         | -        | VDD x 0.1  | V    |

| Pull-down resistor*1             | Rdown            | EN, SCK, SDIO, TEST1                                                                                                                                                                                         | -         | 250      | -          | kΩ   |

| Input capacitance*1              | CIN              | EN, SCK, SDIO, TEST1 - 5 -                                                                                                                                                                                   |           |          | pF         |      |

| Table 5.4 Under Voltage Detector Characteristics |

|--------------------------------------------------|

|--------------------------------------------------|

|                            |               |             | 8          | VSS = ( | ) V, Ta = - | -40 °C to | +85 °C |

|----------------------------|---------------|-------------|------------|---------|-------------|-----------|--------|

| Τ4                         | Course la cal |             | Condition  |         | Standard    |           | Unit   |

| Item                       | Symbol        |             | Condition  | Min.    | Тур.        | Max.      | Unit   |

| Detector threshold         | VDECT         | VDD Falling | VDET = 00b | 1.75    | 1.80        | 1.85      | V      |

|                            |               |             | VDET = 01b | 1.95    | 2.00        | 2.05      | V      |

|                            |               |             | VDET = 10b | 2.15    | 2.20        | 2.25      | V      |

|                            |               |             | VDET = 11b | 2.35    | 2.40        | 2.45      | V      |

| Detector release threshold | VRELE         | VDD Rising  | VDET = 00b | 1.95    | 2.00        | 2.05      | V      |

|                            |               |             | VDET = 01b | 2.15    | 2.20        | 2.25      | V      |

|                            |               |             | VDET = 10b | 2.35    | 2.40        | 2.45      | V      |

|                            |               |             | VDET = 11b | 2.55    | 2.60        | 2.65      | V      |

# 5.3. AC Characteristics

# **Table 5.5 Transmitter Characteristics**

| Item Symbol                  |                   | a tri                                                          |         | <b>T</b> T <b>1</b> |          |      |

|------------------------------|-------------------|----------------------------------------------------------------|---------|---------------------|----------|------|

| Item                         | Symbol            | Condition                                                      | Min.    | Тур.                | Max.     | Unit |

| Carrier frequency bands      | Ftx               |                                                                | 300     | -                   | 465      | MHz  |

|                              |                   | 32MHz clock signal input                                       | 600     | -                   | 930      |      |

| Modulation types             | -                 | -                                                              |         | ASK / OC            | OK / FSK |      |

| ASK bit rate*1               | R <sub>ASK</sub>  | NRZ                                                            | -       | -                   | 100      | kbps |

| FSK bit rate*1               | R <sub>FSK</sub>  | NRZ                                                            | -       | -                   | 50       | kbps |

| Carrier frequency resolution | FSTEP             | Carrier frequency = 300 MHz to 465 MHz                         | -       | -                   | 244      | Hz   |

|                              |                   | Carrier frequency = 600 MHz to 930 MHz                         | -       | -                   | 488      | Hz   |

| FSK deviation                | F <sub>DEV</sub>  | -                                                              | ±0.49   | -                   | ±996.1   | kHz  |

| ASK modulation index*1       | Adev              | In OOK setting<br>Ratio between ON and OFF                     | 90      | -                   | -        | %    |

| Internal crystal frequency   | Fosc              | -                                                              | -       | 32                  | -        | MHz  |

| CKOUT output frequency       | FCKOUT            | See Figure 6.20                                                | 0.00049 | -                   | 32       | MHz  |

| CKOUT                        | tr / tf           | Load capacitance15 pF, 20 to 80% VDD                           |         |                     |          |      |

| rise/fall time*1             |                   | SR = 11b                                                       | -       | -                   | 5        | ns   |

|                              |                   | SR = 10b                                                       | -       | -                   | 7        | ns   |

|                              |                   | SR = 01b                                                       | -       | -                   | 10       | ns   |

|                              |                   | SR = 00b                                                       | -       | -                   | 20       | ns   |

| CKOUT symmetry*1             | SYM               | SR = 11b, load capacitance 15 pF<br>F <sub>CKOUT</sub> = 32MHz | 45      | -                   | 55       | %    |

| PLL settling time*1          | t <sub>FSTE</sub> | See Figure 6.9 and Figure 6.10.                                | -       | -                   | 100      | μs   |

| SSB phase noise*1 *3         | F <sub>CN</sub>   | $F_{TX} = 315 \text{ MHz}$                                     |         |                     | 1        |      |

|                              |                   | 1 kHz offset                                                   | -       | -106                | -        |      |

|                              |                   | 10 kHz offset                                                  | -       | -110                | -        |      |

|                              |                   | 100 kHz offset                                                 | -       | -106                | -        |      |

|                              |                   | 1 MHz offset                                                   | -       | -96                 | -        |      |

|                              |                   | 10 MHz offset                                                  | -       | -104                | -        |      |

|                              |                   | $F_{TX} = 915 \text{ MHz}$                                     |         |                     |          |      |

|                              |                   | 1 kHz offset                                                   | -       | -97                 | -        |      |

|                              |                   | 10 kHz offset                                                  | -       | -103                | -        | 1    |

|                              |                   | 100 kHz offset                                                 | -       | -96                 | -        | ]    |

|                              |                   | 1 MHz offset                                                   | -       | -88                 | -        | 1    |

|                              |                   | 10 MHz offset                                                  | -       | -99                 | -        |      |

### **Table 5.6 PA Characteristics**

|                                                      |                  | Table 5.0 FA Characteristi                                | ()           |                 | VSS          | = 0 V |

|------------------------------------------------------|------------------|-----------------------------------------------------------|--------------|-----------------|--------------|-------|

|                                                      |                  |                                                           |              | Standard        | v 35         | - 0 v |

| Item                                                 | Symbol           | Condition                                                 | Min.         | Тур.            | Max.         | Unit  |

| Nominal output power*1, 2, 3                         | Pout             | /Hz, HPWR =                                               |              | = 10b           |              |       |

|                                                      |                  | $AM^* = 0x3F$                                             | 10.0         | 11.0            | 12.0         | dBm   |

|                                                      |                  | $AM^* = 0x01$                                             | -6.5         | -5.5            | -4.5         |       |

|                                                      |                  | $Ta = 25^{\circ}C$ , $VDD = 3.0 V$ , $F_{TX} = 433 N$     | /Hz, HPWR =  | 1, PADUTY       | = 10b        | 1     |

|                                                      |                  | $AM^* = 0x3F$                                             | 10.5         | 11.5            | 12.5         | ID    |

|                                                      |                  | $AM^* = 0x01$                                             | -6.0         | -5.0            | -4.0         | dBm   |

|                                                      |                  | $Ta = 25^{\circ}C, VDD = 3.0 V, F_{TX} = 868 M$           | Hz, HPWR =   | 1, PADUTY       | =01b         |       |

|                                                      |                  | $AM^* = 0x3F$                                             | 9.5          | 11              | 12.5         | dBm   |

|                                                      |                  | $AM^* = 0x01$                                             | -7.0         | -5.5            | -4.0         | uБШ   |

|                                                      |                  | $Ta = 25^{\circ}C$ , $VDD = 3.0 V$ , $F_{TX} = 915 N$     | =01b         |                 |              |       |

|                                                      |                  | $AM^* = 0x3F$                                             | 9.5          | 11              | 12.5         | dBm   |

|                                                      |                  | $AM^* = 0x01$                                             | -7.0         | -5.5            | -4.0         | ubiii |

|                                                      |                  | $Ta = 25^{\circ}C, VDD = 3.0 V, F_{TX} = 315 M$           | /Hz, HPWR =  | 0, PADUTY       | = 10b        |       |

|                                                      |                  | $AM^* = 0x3F$                                             | 1.0          | 2.0             | 3.0          | dBm   |

|                                                      |                  | $AM^* = 0x01$                                             | -16.0        | -15.0           | -14.0        | dDill |

| Output power temperature dependence <sup>*1, 2</sup> | P <sub>TMP</sub> | Ta = $-40^{\circ}$ C to $+85^{\circ}$ C,<br>VDD = $3.0$ V | -1           | -               | 1            | dB    |

| Output power supply voltage                          | Pvdd             | $Ta = 25^{\circ}C$ , $VDD = 1.8 V$ to 3.6 V, VD           | DD = 3.0V    |                 |              |       |

| dependence*1,2                                       |                  | AM* > 0x20                                                | -4           | -               | 1            | dB    |

|                                                      |                  | $AM^* \leq 0x20$                                          | -1           | -               | 1            | dB    |

| Harmonics level <sup>*1, 2</sup>                     | PdBc             | $Ta = 25^{\circ}C, VDD = 3.0 V, AM^* = 0x1$               | F, HPWR = Ra | atio of the 1st | and 2nd harm | onics |

|                                                      |                  | $F_{TX} = 315 / 433 \text{ MHz},$<br>PADUTY = 10b         | -            | -34             | -            | dBc   |

|                                                      |                  | $F_{TX} = 868 / 915 \text{ MHz}$<br>PADUTY = 01b          | -            | -40             | -            | dBc   |

\*1 Guaranteed by design, characterization, and/or simulation only and not by production test.

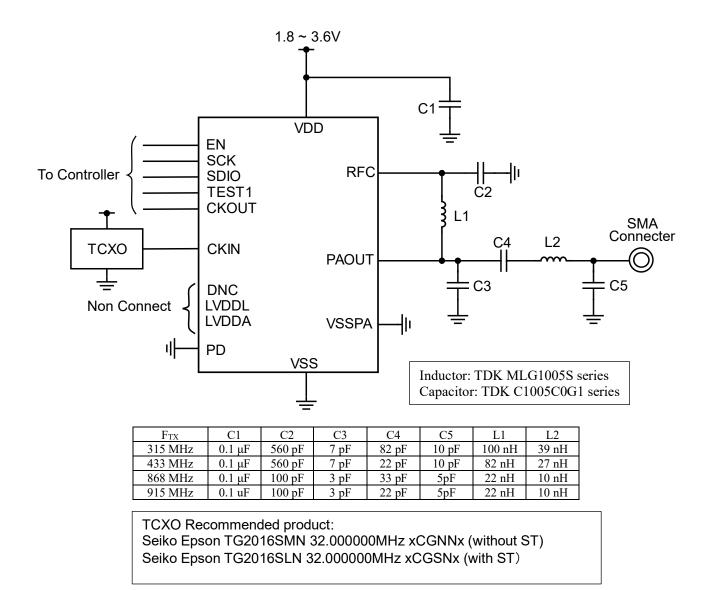

\*2 Test circuit is shown in Figure 5.1.

\*3 Without aging.

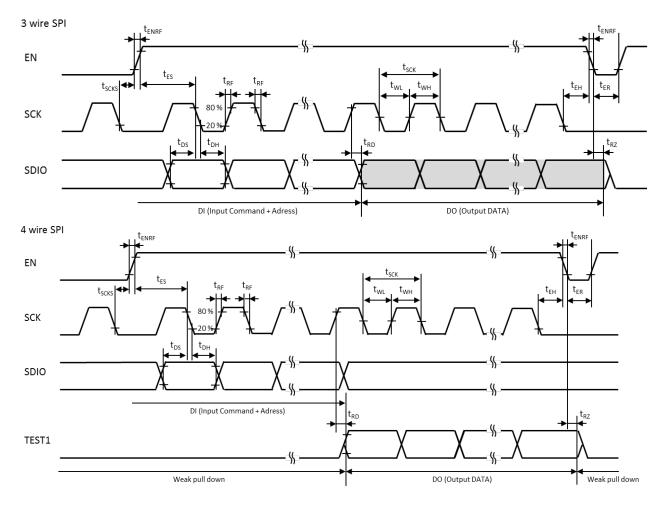

# **Table 5.7 SPI Interface Characteristics**

|                          |        | VDD = 1.8   | 8 V to 3.6 V | VSS = 0 V | /, Ta = −40°C | to +85°C |

|--------------------------|--------|-------------|--------------|-----------|---------------|----------|

| Item                     | Symbol | Condition   |              |           | Unit          |          |

|                          | Symbol | Condition   | Min.         | Тур.      | Max.          | Onit     |

| SCK clock cycle          | tSCK   | -           | 330          | -         | -             | ns       |

| SCK H pulse width        | tWH    | -           | 150          | -         | -             | ns       |

| SCK L pulse width        | tWL    | -           | 150          | -         | -             | ns       |

| SCK rise and fall time   | tRF    | -           | -            | -         | 20            | ns       |

| SCK setup time           | tSCKS  | -           | 100          | -         | -             | ns       |

| EN setup time            | tES    | -           | 150          | -         | -             | ns       |

| EN hold time             | tEH    | -           | 100          | -         | -             | ns       |

| EN recovery time         | tER    | -           | 100          | -         | -             | ns       |

| EN rise and fall time    | tENRF  | -           | -            | -         | 30            | ns       |

| Write data setup time    | tDS    | -           | 20           | -         | -             | ns       |

| Write data hold time     | tDH    | -           | 20           | -         | -             | ns       |

| Read data delay time     | tRD    | CL = 50 pF  | 0            | -         | 100           | ns       |

| SDIO output disable time | tRZ    | CL = 50  pF | 0            | -         | 100           | ns       |

# 6. Function Description

# 6.1. Outline

RF transmitter IC S1S77100 is a wireless transmitter IC for the UHF range. This IC houses a PLL and a Power Amp in a 4 mm x 4 mm SQFN package. The S1S77100 can be configured in combination with an external crystal oscillator. So, it is suitable for small wireless devices.

As you can control the wireless transmitter settings via the SPI interface, the S1S77100 supports carrier frequency of 300-465 MHz, 600-930 MHz. You can select ASK, OOK, or FSK modulation. Soft-ASK and Soft-FSK are provided to reduce modulation bandwidth.

This module has a fail-safe function. If a failure is detected, it shuts down the power supply to PA.

The signals of the dividing clock are outputted from the CKOUT pin. They can be used as clock source and interrupt signal for an MCU.

# 6.2. SPI Interface

The S1S77100 has a 3-wire/4-wire SPI interface. It is used to access SFR, which controls operations, and to transmit modulated signals using transmit commands.

# EN

The EN pin is used to input SPI enable signal, control SPI communications, and input the timing to latch transmission data.

When the EN pin rises, the mode of the S1S77100 is transited from Powerdown mode to CKBUF-Active mode, and 2 MHz (32 MHz divided by 16) is outputted from the CKOUT pin by inputting the clock from an external crystal oscillator. When the EN pin falls, the SPI interface is initialized. If the EN pin is kept low at least 8.2 ms (2<sup>18</sup> input clocks), the state transits to Powerdown mode.

After sending the transmit command (if bit "B" = 1), the EN pin additional function is available. The SDIO signal is latched as transmission data at the falling edge of the EN signals.

# SCK

The SCK pin is the clock input for SPI. This pin is used for loading SDIO data, synchronized with the SCK falling edge.

# SDIO

The SDIO pin is the bi-directional data input/output pin for 3-wire SPI mode. It also works as data input pin for 4-wire SPI mode.

The SDIO pin is used for RF transmission data input during RF data transfer. If you select RF transmission data input through the TEST1 pin, the SDIO signals do not affect RF data transmission. See section 6.2.4 for details.

# TEST1

The TEST1 pin is used for data output in 4-wire SPI mode.

If you select this pin to data input for RF data transmission, this TEST1 pin becomes the data input pin. See section 6.2.4 for details.

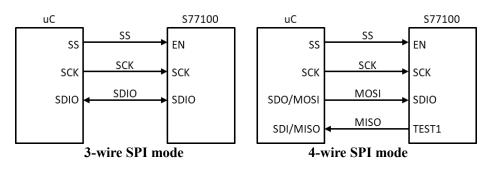

# 6.2.1. SPI interface mode change

The SPI interface mode is changed by setting IFSEL[1:0], which is assigned to SFR address 0x15. (See Table 6.1 and Figure 6.1.)

When connecting the S1S77100 with MCU in 4-wire SPI mode, you can write data without setting IFSEL[1:0]. To read data, set IFSEL[1:0].

| IFSEL[1:0] | SPI mode                  | Transmission data |

|------------|---------------------------|-------------------|

|            |                           | input pin         |

| 00b        | 3-wire SPI mode (default) | SDIO              |

| 01b        | 4-wire SPI mode           | SDIO              |

| 10b        | 3-wire SPI mode           | TEST1             |

| 11b        | Invalid                   |                   |

# Table 6.1 Interface Mode Setting

Figure 6.1 HOST Interface Example

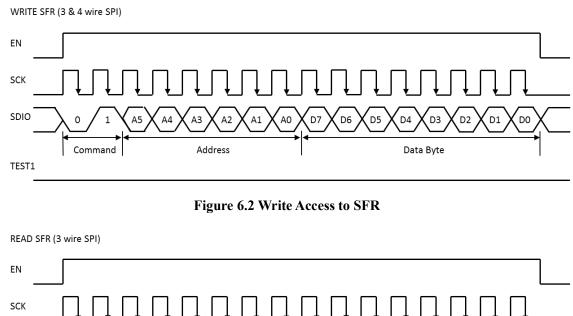

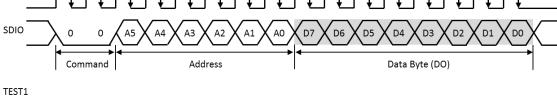

### 6.2.2. SFR access command

You can access SFR using 3-wire and 4-wire SPI mode.

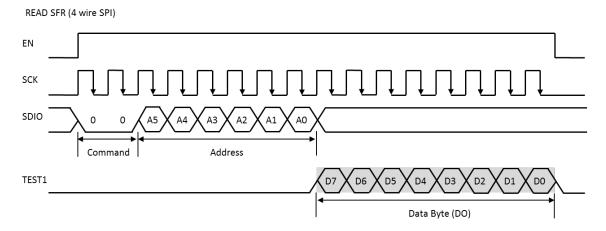

Figure 6.2 depicts the timing for writing access in 3-wire and 4-wire SPI modes, Figure 6.3 shows the timing for read access in 3-wire SPI mode, and Figure 6.4 shows the timing for read access in 4-wire SPI mode.

Figure 6.3 3-wire SPI Read Access to SFR

Figure 6.4 4-wire SPI Read Access to SFR

As the loading of data is synchronized with SCK falling, the output data is updated with the SCK rising edge. After the rising of the EN pin, write the 2 bits of the command bit shown in **Table 6.2** and the 6 bits of the address. If the command is SFR writing, the host may continue sending data to be written on SFR. If the command is SFR reading, this device shifts out the data of SFR.

| Command bit | Function         |

|-------------|------------------|

| 00b         | SFR reading      |

| 01b         | SFR writing      |

| 10b         | Not available    |

| 11b         | Transmit command |

#### Table 6.2 Command Bit

The S1S77100 supports burst write and read. **Figure 6.5** depicts the timing for burst write access in 3-wire and 4-wire SPI modes, **Figure 6.6** shows the timing for burst read access in 3-wire SPI mode, and **Figure 6.7** shows the timing for burst read access in 4-wire SPI mode. While burst writing & reading, the SFR address is incremented automatically from any address sent by the command address bit.

It is recommended to reset the SFR communication by setting EN pin low after SFR access is finished. If the EN pin is not set to low, external noise may cause unintentional write access.

BURST WRITE SFR (3 & 4 wire SPI) EN ſſſſſſſ  $\prod |\downarrow$ D6 D4 D3 Data Byte 0 Data Byte 1 TEST1 Figure 6.5 Burst Write Access to SFR BURST READ SFR (3 wire SPI) EN SCH SDIC X d4 X d3 > D4 X D3 X D6 Command Addres Data Byte 0 (DO) Data Byte 1 (DO Data Byte N (DO TEST1 Figure 6.6 3-wire SPI Burst Read Access to SFR BURST READ SFR (4 wire SPI) EN  $1\Pi\Pi\Gamma$ SDIC A4 A3 X A2 X A1 X A0 TEST1 D5 X D4 X D3 ( d6 X d5 X d4 X d3 ) (D5 X D4 X D3 X D2 ) DO C D2 Data Byte (DO) Data Byte 1 (DO) Data Byte N (DO)

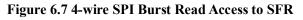

# 6.2.3. SPI checksum

### SPI checksum is available (**Figure 6.8**).

The XOR arithmetic calculation of command + address 8 bits and data 8 bits is operated during SFR write access. The checksum result is stored in 0x16 SFR address. The checksum is reset by transiting to Powerdown mode or writing any data to checksum register (address 0x16).

Figure 6.8 SPI Checksum Process Block Diagram

**Table 6.3** shows SPI checksum example. If you write 0x02 in address 0x04 and 0x01 in address 0x05, the value 0x02 is stored in checksum register.

# Table 6.3 SPI Checksum Calculation Example

| Transmission byte by SPI    | Checksum result |

|-----------------------------|-----------------|

| 0100 0100 (Write + Address) | 0100 0100       |

| 0000 0010 (Data)            | 0100 0110       |

| 0100 0101 (Write + Address) | 0000 0011       |

| 0000 0001 (Data)            | 0000 0010       |

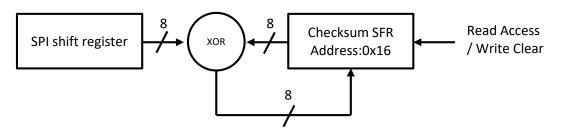

# 6.2.4. Transmit command

The Transmit command is activated when the SPI command bit is set to 11b. The six bits (A to F) that follow the command bit specify the transmit function structure. (See **Table 6.4**) The Transmit command is available only in PLL-Standby mode described in section 6.3.1.

| Bit  | Function                                    | Value, description                                                                                                                      |

|------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| А    | Data Sync                                   | 0: Asynchronous Transmission<br>1: Synchronous Transmission                                                                             |

| В    | Power Amp mode                              | 0: PA is turned off with the falling edge of EN pin<br>1: The SDIO signal is latched as transmission data at the falling edge of EN pin |

| С    | Encoding                                    | 0: NRZ<br>1: Manchester code (Bit "A" must be set to 1.)                                                                                |

| D    | ASK Modulation Control<br>Setting Selection | 0: ASKMC0<br>1: ASKMC1                                                                                                                  |

| E, F | Frequency Channel selection                 | 00: Frequency channel 1<br>01: Frequency channel 2<br>10: Frequency channel 3<br>11: Frequency channel 4                                |

#### Table 6.4 Details on Transmit Function

After sending transmit command, wait for PLL settling time ( $t_{FSTE}$ ), rise SCK. PA is activated, and RF data transmission starts. If you rise SCK before PLL is settled ( $t_{FSTE}$ ), an unexpected frequency RF signal may be outputted.

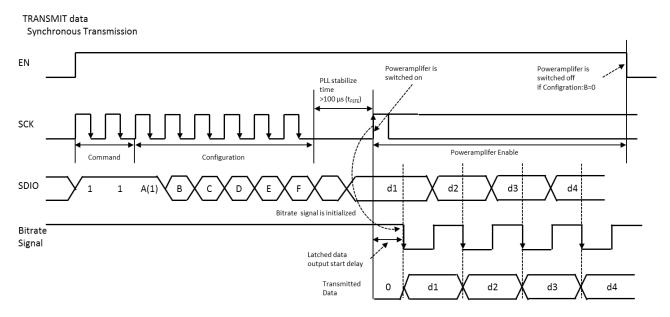

Wireless transmission has both an asynchronous transmission mode and synchronous transmission mode. The mode can be selected by bit "A" of the transmission command.

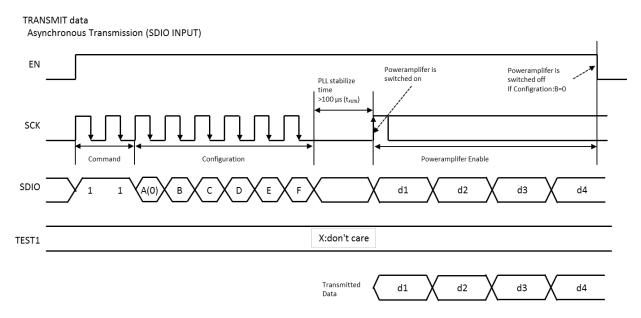

### Asynchronous transmission

**Figure 6.9** shows asynchronous transmission. In asynchronous transmission mode, the SDIO signals are directly input into the modulator, and the carrier is modulated into ASK/OOK/FSK by transmitting signal.

TRANSMIT data Asynchronous Transmission

Figure 6.9 Asynchronous Transmission Timing

# Synchronous transmission mode

Synchronous transmission timing is shown in **Figure 6.10**. In synchronous transmission mode, SDIO signals are latched by the bitrate signals, and the latched signals are transmitted. The bitrate signal for latch is formed by dividing the frequency for the external crystal oscillator, thus the bitrate signal has same accuracy as the input clock.

Users can output divide clock synchronized with the bitrate signal from CKOUT pin.

If divided clock are supplied to MCU as system clock, please note that clock pulse width may be changed by divider initialization with PA start-up. There may be 1 prescaler clock delay in bitrate signal initialization. See section 6.8 for more details of CKOUT function.

Figure 6.10 Synchronous Transmission Timing

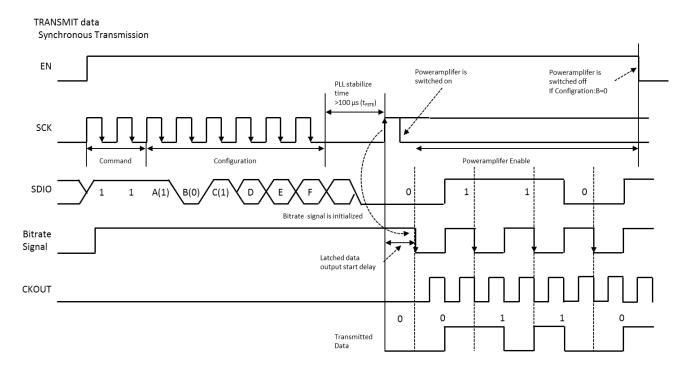

**Figure 6.11** shows synchronous transmission example in the following settings: Synchronous transmission (bit "A" = 1), PA is OFF (bit "B" = 0) when EN falls, transmission sign is Manchester code (bit "C" = 1), CKSRC [2:0] = 010b, ASC [2:0] = 1. See section 6.8 for CKOUT settings and details.

Figure 6.11 Synchronous Transmission Example

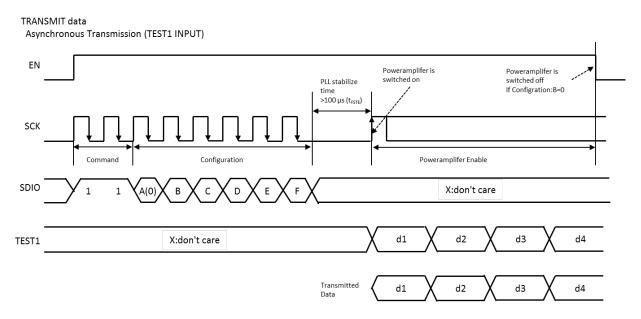

#### Transmission data input process

Transmission signal input method is selected by IFSEL[1:0] setting. Both pins are available in both the synchronous transmission mode and the asynchronous transmission mode. See **Figure 6.12** for transmission signal input timing details through the SDIO pin and **Figure 6.13** for transmission signal input timing details through the TEST1 pin.

Figure 6.12 Transmission Signal Input Timing Details through SDIO Pin

Figure 6.13 Transmission Signal Input Timing Details through TEST1 Pin

# 6.3. Operating Modes

# 6.3.1. State transition

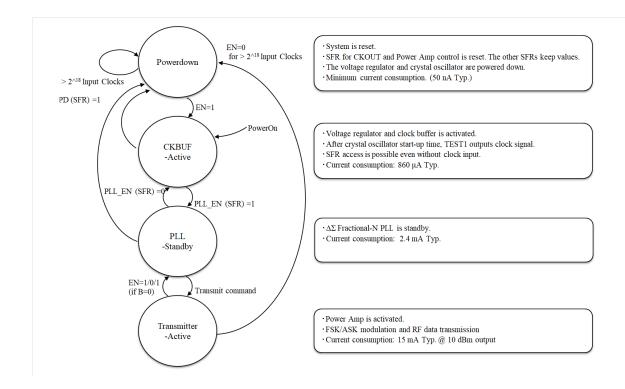

The S1S77100 has 4 modes, and you can control state transition using pins or SPI command. The state diagram is shown in **Figure 6.14**. See the section below for details of each mode.

# Powerdown mode

In Powerdown mode, minimum required circuits are powered on, and the current consumption is lowest. If the EN pin is kept low for at least 8.2 ms (2<sup>18</sup> crystal clocks), the mode is transited from any mode to Powerdown mode, and the S1S77100 is reset.

If you want to enter Powerdown mode immediately after the EN pin is set low, write "1" in the bit "PD" in SFR address 0x15.

SFR values related to control are reset, and other SFR values are retained. However, their retention is not guaranteed because the under voltage detection is disabled in Powerdown mode. It is strongly recommended to reprogram all SFR values after exiting from Powerdown mode.

Please note that in states other than the Powerdown state, a clock input to the CKIN pin is required for state transition.

# **CKBUF-Active mode**

In CKBUF-Active mode, the internal voltage regulator, the input clock buffer, and the under voltage detection circuit are activated. With rising edge of the EN pin, the S1S77100 transits from Powerdown mode to CKBUF-Active mode, it takes 100 µs for the clock signal input from the crystal oscillator. After transition to CKBUF-Active mode, 2 MHz (32 MHz divided by 16) is outputted from CKOUT. Users can set other dividing frequency and stop CKOUT with SFR settings. See section 6.8 for more details of CKOUT. SFR can be accessed through SPI interface even if the input clock.

The S1S77100 enters CKBUF-Active mode when it turns on. Therefore, even if the EN pin is set low before the S1S77100 is turned on, CKOUT outputs clock signals for 8.2 ms ( $2^{18}$  crystal oscillator clock) after the clock input.

# PLL-Standby mode

The internal voltage regulator, the input clock buffer, and the under voltage detect circuit are activated, and PLL circuit enters stand-by mode. The S1S77100 enters PLL-Standby mode by setting the bit "PLLEN" in SFR address 0x15 to 1.

# **Transmitter-Active mode**

The internal voltage regulator, the input clock buffer, the under voltage detect circuit, PLL circuit and PA are activated, and RF signals are outputted from the PAOUT pin. The S1S77100 enters Transmitter-Active mode by sending a transmit command in PLL-Standby mode. See section 6.2.4 for more details of transmit command. If the fail-safe function detects a fail while the PA is running in Transmitter-Active mode, the PA can be switched off. (See section 6.7 for details.)

In Transmitter-Active mode, SFR write access is not available. If you want to change SFR settings, change the mode to CKBUF-Active mode or PLL-Standby mode to write SFR values.

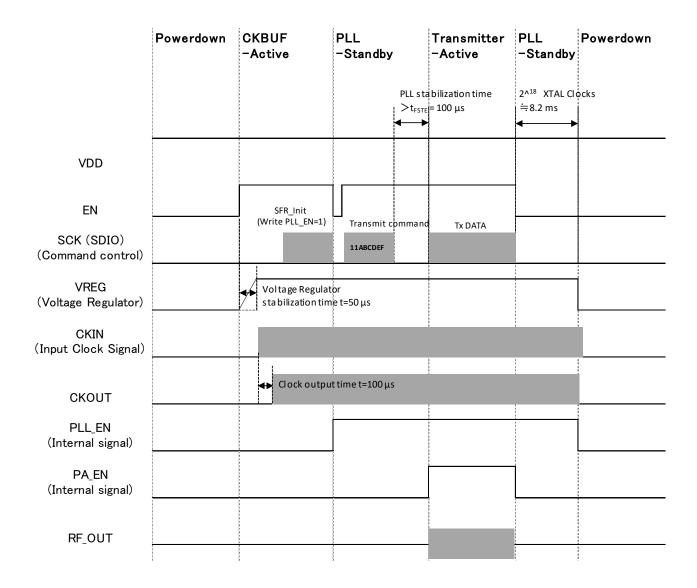

# 6.3.2. Control signal timing

An example of control signal timing is shown in **Figure 6.15**. Figure 6.15 shows a wireless transmission sequence that starts from and goes back to Powerdown mode.

First, the mode is changed from Powerdown mode to CKBUF-Active mode when the EN pin rises. After the EN pin is turned on, the built-in voltage regulator starts up. It is recommended to start clock input from the CKIN pin after 50us when the voltage regulator has stabilized. After inputting the clock, a maximum of 100us is required until the clock is output from CKOUT.

After the transition to CKBUF-Active mode, and transition to PLL-Standby mode becomes available. Since PLL\_EN is set to 1 in the SFR\_Init process in **Figure 6.15**, the mode is changed to PLL-Standby mode immediately.

The mode is changed to Transmitter-Active mode when a transmit command is sent and the PA is activated by having SCK rise after  $t_{FSTE}$  (PLL settling time) has elapsed. The PA stops 100 ns after the falling edge of the EN pin, and the mode is changed to PLL-Standby mode. If the EN pin is kept low for 8.2 ms (2<sup>18</sup> input clock), the mode is change to Powerdown mode.

If you want to enter Powerdown mode immediately after the EN pin is set low, write "1" in the bit "PD" in SFR address 0x15.

### Figure 6.15 Control Signal Timing

# 6.4. Output Frequency Setting

### 6.4.1. Calculation for the frequency setting value

Carrier frequency  $(F_{TX})$  is determined by the VCO frequency  $(F_{VCO})$  and the division ratio of output divider (ODIV) as shown in formula (1).

$$F_{TX} = \frac{F_{VCO}}{ODIV} \tag{1}$$

VCO frequency ( $F_{VCO}$ ) must be 600 MHz to 930 MHz. The output divider (ODIV) is determined by this rule and  $F_{TX}$  in formula (1). See **Table 6.5** for details.

#### Table 6.5 fo and FnODIV

| F <sub>TX</sub> [MHz] | ODIV | FnODIV (SFR address 0x0A) |

|-----------------------|------|---------------------------|

| 300 to 465            | 2    | 1                         |

| 600 to 930            | 1    | 0                         |

VCO frequency ( $F_{VCO}$ ) is determined by the reference frequency ( $F_{REF}$ ), which is supplied from input clock, and the division ratio of feedback divider (N). The division ratio of feedback divider is determined by the integral setting for 4 bits ( $N_{INT}$ ) and the fractional setting for 16 bits ( $N_{FRAC}$ ) that enable highly stable frequency settings. The VCO frequency ( $F_{VCO}$ ) is calculated by formula (2):

$$F_{VCO} = F_{REF} \times N = F_{REF} \times \left(N_{INT} + \frac{4 \times N_{FRAC} + 3}{2^{18}}\right)$$

(2)

Output frequency  $(F_{TX})$  is calculated by formula (3):

$$F_{TX} = \frac{F_{VCO}}{ODIV} = F_{REF} \frac{\left(N_{INT} + \frac{4 \times N_{FRAC} + 3}{2^{18}}\right)}{ODIV}$$

(3)

For example, if reference frequency ( $F_{REF}$ ) is 32 MHz and output frequency should be 315 MHz, ODIV is calculated to be "2" by **Table 6.5**. Then the division settings of feedback divider (N, N<sub>INT</sub>, and N<sub>FRAC</sub>) are calculated by formulas (4) to (6) based on formula (2).

$$N = N_{INT} + \frac{4 \times N_{FRAC} + 3}{2^{18}} = \frac{F_{OUT} \times ODIV}{F_{REF}} = \frac{315 \times 10^6 \times 2}{32 \times 10^6} = 19.6875$$

(4)

$$N_{INT} = floor(N) = floor(19.6875) = 19$$

(5)

$$N_{FRAC} = \frac{(N - N_{int}) \times 2^{18} - 3}{4} = \frac{(19.6875 - 19) \times 2^{18} - 3}{4} \cong 45055 = 0xAFFF$$

(6)

**Table 6.6** shows N<sub>INT</sub> and SFR parameters.

$N_{INT}$  is 4 bits and  $N_{FRAC}$  is 16 bits. You can set different  $N_{INT}$  values and  $N_{FRAC}$  values in each frequency channel of the SFR. (SFR address 0x00 to 0x09).

For example, if you want to set  $N_{INT}$  and  $N_{FRAC}$ , which are calculated by formula (6), to the channel 1, make the following settings:

SFR address 0x00, F1FRAC[15:8] = 0xAF

SFR address 0x01, F1FRAC[7:0] = 0xFFSFR address 0x04, F1INT[3:0] = 0x03

See chapter 7 for details.

#### Table 6.6 NINT and SFR Parameters

| Nint | FnINT[3:0] (SFR address 0x04, 0x09) |

|------|-------------------------------------|

| 16   | 0x0                                 |

| 17   | 0x1                                 |

| 18   | 0x2                                 |

| 19   | 0x3                                 |

| 20   | 0x4                                 |

| 21   | 0x5                                 |

| 22   | 0x6                                 |

| 23   | 0x7                                 |

| 24   | 0x8                                 |

| 25   | 0x9                                 |

| 26   | 0xA                                 |

| 27   | 0xB                                 |

| 28   | 0xC                                 |

| 29   | 0xD                                 |

| 30   | 0xE                                 |

| 31   | 0xF                                 |

### 6.5. FSK Modulator

#### 6.5.1. **FSK deviation setting**

You can set FSK deviation in SFR address 0x0B. FSK modulation ( $F_{DEV}$ ) is calculated by formula (7).  $F_{REF}$  is the reference frequency of crystal oscillator. FDEV, FDEV4X and FDEV2X are SFR setting values.

$$F_{DEV} = \pm \frac{F_{REF} \times FDEV}{2^{16}} \times 4^{FDEV4X} \times 2^{FDEV2X}$$

(7)

For example, if you set FDEV to 31, FDEV4X to 0, and FDEV2X to 0, FSK deviation ( $F_{DEV}$ ) is calculated by formula (8).

$$F_{DEV} = \pm \frac{F_{REF} \times FDEV}{2^{16}} \times 4^{FDEV4X} \times 2^{FDEV2X} = \pm \frac{32 \times 10^6 \times 31}{2^{16}} \times 4^0 \times 2^0 \cong \pm 15.136 \, kHz$$

(8)

Carrier frequency is modulated to  $F_{TX} + F_{DEV}$  in high level data transmission and to  $F_{TX}$  -  $F_{DEV}$  in low level data transmission.

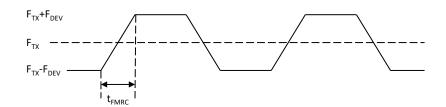

#### 6.5.2. **Soft-FSK**

Soft-FSK function is implemented to reduce FSK modulation bandwidth. In Soft-FSK, modulation is applied in ramp shape shown in **Figure 6.16**.

Figure 6.16 Soft-FSK Modulation Wave

$t_{FMRC}$  shown in **Figure 6.16** is calculated by formula (9). The FMRC in formula (9) determines the inclination of ramp shape and is assigned to SFR address 0x10.

$$t_{FMRC} = 0DIV \times 2 \times FDEV \times FMRC \times \frac{1}{F_{REF}}$$

(9)

# 6.6. Output Power Setting

#### 6.6.1. **ASK modulation**

You can make settings for PA output power and ASK modulation in SFR address 0x0C to 0x0E. See chapter 7 for details of SFR addresses. This section provides the details of each bit.

### ASKMC0/ASKMC1 selection

8 bits are assigned to SFR address 0x0C (ASKMC0) and 0x0D (ASKMC1). The ASKMC means ASK Modulation Control. The 8 bits consist of ASK/FSK modulation setting, output power range setting, and output power minor adjustment.

You can select ASKMC0 or ASKMC1 using the transmit command bit "D" just before transmission.

### ASKn

ASKn switches ASK modulation and FSK modulation (n = 0/1, ASK0 or ASK1). See Table 6.7 for details.

#### Table 6.7 ASKn Settings

| ASKn | Modulation method |

|------|-------------------|

| 0    | FSK               |

| 1    | ASK               |

# HPWRn

HPWRn switches output power range (n = 0/1, HPWR0 or HPWR1). See **Table 6.8** for details.

#### Table 6.8 HPWRn Settings

| HPWRn | Output power range |

|-------|--------------------|

| 0     | -15 dBm to 0 dBm   |

| 1     | -5 dBm to 11 dBm   |

#### AMHn[5:0]

AMHn[5:0] is output power setting in H level data transmission for ASK (n = 0/1, AMH0[5:0] or AMH1[5:0]). It is also output power setting for FSK.

# AML[5:0]

AML[5:0] is output power setting in L level data transmission for ASK modulation. If you set AML[5:0] = 000000b, the PAOUT pin goes OFF, which means OOK mode.

### PADUTY[1:0]

The function of changing duty cycle is implemented to improve the PA efficiency. See **Table 6.9** for setting values and nominal duty cycle. You may improve PA efficiency by making the shape duty small and the on-time in output transistor small. However, since harmonics spurious is also changed, check output power, current consumption, and harmonics spurious before use if you change recommended values.

Recommended values based on the test circuit shown in Figure 5.1: 10bfor  $F_{TX} = 300$  MHz to 465 MHz, 01b for  $F_{TX} = 600$  MHz to 930 MHz.

| PADUTY[1:0]  | Nominal duty cycle                    |                                       |

|--------------|---------------------------------------|---------------------------------------|

| FADUI I[1.0] | $F_{TX} = 300 \text{ MHz}$ to 465 MHz | $F_{TX} = 600 \text{ MHz}$ to 930 MHz |

| 00b          | 50%                                   | 50%                                   |

| 01b          | 45%                                   | 36%                                   |

| 10b          | 36%                                   | Not available                         |

| 11b          | 30%                                   | Not available                         |

#### Table 6.9 PADUTY[1:0] Setting

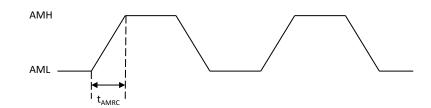

#### 6.6.2. Soft-ASK

Soft-ASK function is implemented to reduce the ASK modulation bandwidth. In Soft-ASK, modulation is applied in ramp shape shown in **Figure 6.17**.

Figure 6.17 Soft-ASK Modulation Wave

$t_{AMRC}$  shown in **Figure 6.17** is calculated by formula (10). The AMRC of formula (10) determines the inclination of ramp shape and is assigned to SFR address 0x0F.

$$t_{AMRC} = (AMH - AML) \times AMRC \times \frac{1}{F_{REF}}$$

(10)

The AMRC setting also works for FSK modulation. The load for power supply is reduced by applying ramp shape to start-up PA current consumption.

#### 6.6.3. Antenna tuning

The PA has a variable capacitor array for antenna tuning. It is connected between the PAOUT pin and the VSS pin. Its capacitance is controlled by ATT [4:0] in SFR address 0x13. See **Table 6.10** for setting values and capacitance.

| ATT [4:0] | Capacitance |

|-----------|-------------|

| 0         | 184 fF      |

| 1         | 223 fF      |

| 2         | 262 fF      |

| -         | -           |

| -         | -           |

| 31        | 1393 fF     |

Table 6.10 ATT [4:0] Settings

# 6.7. Fail-safe Function

The S1S77100 has three kinds of fail-safe functions. If a fail is detected, the PA is turned off according to fail-safe settings.

This function detects PLL loss of lock, VCO auto-calibration errors, and under voltage. Error results are stored in SFR address 0x14 and can be read out. Error results are reset by transition to Powerdown mode or writing any data to SFR address 0x14.

You can change PA control using the bit "FSOFF" in SFR address 0x15. If the FSOFF = 0, PA turns off when a fail is detected. If the FSOFF = 1, PA does not turn off when a fail is detected.

When FSOFF = 0 and a fail is detected, PA does not turn on after transition to Transmitter-Active mode if error flags are not reset.

# 6.7.1. PLL Loss of Lock detection

The Loss of Lock detector works in the Transmitter-Active mode. It always compares the reference signal frequency and the feedback signal frequency, which are input in the phase frequency detector in the PLL, using logic counter. If PLL locks, the frequencies of reference signals and feedback signals are the same. If the frequency difference between reference signals and feedback signals exceeds threshold, the detector judges it as an error. Error detection results are stored in the PLLDER in SFR address 0x14.

### 6.7.2. VCO auto-calibration error detection

After sending transmit command, VCO in the PLL is automatically calibrated during  $t_{FSTE}$  (100 µs). If the result of this calibration exceeds the threshold, it is determined that oscillation frequency is not correct, and an error is detected. Error detection results are stored in the VCOCER in SFR address 0x14.

### 6.7.3. Under voltage detection

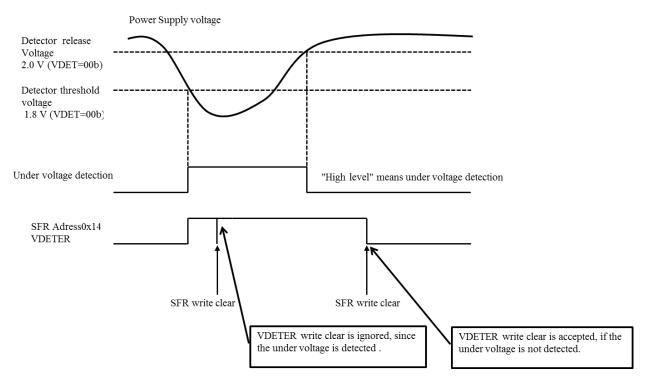

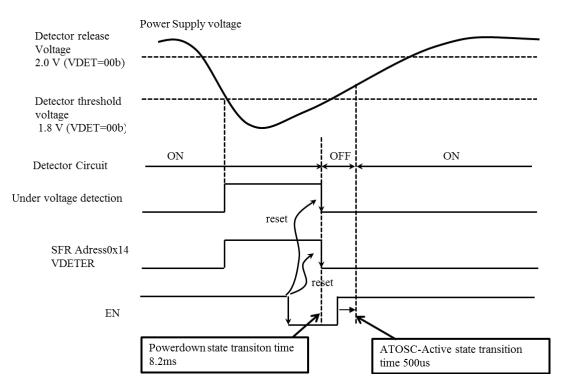

The supply voltage is always monitored in CKBUF-Active mode, PLL-Standby mode, and Transmitter-Active mode. If the supply voltage becomes lower than detecting threshold, an error is detected until the supply voltage exceeds release threshold. You can set the detecting threshold and release threshold using VDET [1:0] in SFR address 0x13.

See Table **5.3** for details.

Error detection results are stored in the VDETER in SFR address 0x14.

Figure 6.18 and Figure 6.19 show the details of under voltage and VDETER reset timing. Error results are reset by SFR write clear in Figure 6.18 and by transition to Powerdown mode in Figure 6.19.

Figure 6.18 Reset of Under Voltage Detection Results by SFR Write Clear

Figure 6.19 Reset of Under Voltage Detection Results by Transition to Powerdown Mode

# 6.8. Clock Output (CKOUT) Function

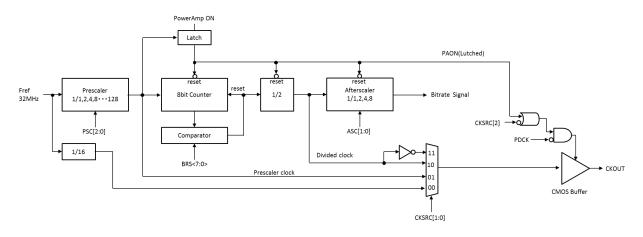

### 6.8.1. **Frequency divider**

The frequency divider structure for CKOUT/bitrate signal is shown in **Figure 6.20**. The frequency divider for CKOUT/bitrate signal consists of three programmable dividers and two fixed dividers. You can select signals output from the CKOUT using CKSRC[2:0] in SFR address 0x12h. The detail of CKSRC[2:0] is shown in **Table 6.11**. CKSRC[2:0] is reset to 000b when the mode is changed to Powerdown mode. Therefore, 2 MHz (Fref/16) is outputted from the CKOUT pin right after the mode is changed from Powerdown mode to CKBUF-Active mode.

The "Bitrate Signal" shown in **Figure 6.20** is a signal for latch of SDIO pin data in synchronous communication mode. It is same as the "Bitrate Signal" shown in **Figure 6.10** and **Figure 6.11**.

Figure 6.20 Frequency Divider Structure for CKOUT/Bitrate Signal

| CKSRC[2:0] | CKOUT                          |

|------------|--------------------------------|

| 000b       | Fref / 16                      |

| 001b       | Prescaler clock                |

| 010b       | PAON: 0 "Low"                  |

| 0100       | PAON: 1 Divided clock          |

| 011b       | PAON: 0 "High"                 |

| 0110       | PAON: 1 Inverted divided clock |

| 100b       | PAON: 0 High-Z                 |

| 1000       | PAON: 1 Fref / 16              |

| 101b       | PAON: 0 High-Z                 |

| 1010       | PAON: 1 Prescaler clock        |

| 110b       | PAON: 0 High-Z                 |

| 1100       | PAON: 1 Divided clock          |

| 111b       | PAON: 0 High-Z                 |

|            | PAON: 1 Inverted divided clock |

# Table 6.11 CKSRC[2:0] Setting

### 6.8.2. Frequency divider setting

The settings for "Prescaler" shown in **Figure 6.20** is made in PSC[2:0] in SFR address 0x12. See **Table 6.12** for details.

| PSC[2:0] | Division ratio |

|----------|----------------|

| 0        | 1/1            |

| 1        | 1/2            |

| 2        | 1/4            |

| 3        | 1/8            |

| 4        | 1/16           |

| 5        | 1/32           |

| 6        | 1/64           |

| 7        | 1/128          |

#### Table 6.12 PSC[2:0] Setting

The settings for "Comparator" shown in Figure 6.20 is made in BRS[7:0] in SFR address 0x11. See Table 6.13.

| BRS[7:0] | Division ratio |

|----------|----------------|

| 0        | 1/1            |

| 1        | 1/2            |

| 2        | 1/3            |

| 3        | 1/4            |

| 4        | 1/5            |

| -        | -              |

| -        | -              |

| 255      | 1/256          |

#### Table 6.13 BSC[7:0] Setting

The settings for "Afterscaler" shown in **Figure 6.20** is made in ASC[2:0] in SFR address 0x12. See **Table 6.14** for details.

### Table 6.14 ASC[2:0] Setting

| ASC[2:0] | Division ratio |  |  |  |  |  |

|----------|----------------|--|--|--|--|--|

| 0        | 1/1            |  |  |  |  |  |

| 1        | 1/2            |  |  |  |  |  |

| 2        | 1/4            |  |  |  |  |  |

| 3        | 1/8            |  |  |  |  |  |

# 6.8.3. Output CMOS driver

The slew rate of CMOS driver for CKOUT pin is selectable. Make settings in SR[1:0] in SFR address 0x0A. 00b is the minimum, and 11b is the maximum.

The SR[1:0] is reset to 00b when the mode is changed to Powerdown mode. 2 MHz (Fref/16) is outputted from the CKOUT pin when the mode is changed from Powerdown mode to CKBUF-Active mode. SR[1:0] = 00b is optimum for 2 MHz output. After that, if you want to output higher frequency signals from the CKOUT pin, make SR[1:0] settings for required rise/fall time.

Table 6.15 shows division ratio and recommended SR[1:0] values for respective frequencies.

Table 6.15 Recommended SR[1:0] Setting

| CKOUT frequency [MHz] | PSC[2:0] | Division ratio | SR[1:0] recommended setting* |  |  |  |

|-----------------------|----------|----------------|------------------------------|--|--|--|

| 32                    | 0        | 1/1            | 11b                          |  |  |  |

| 16                    | 1        | 1/2            | 10b                          |  |  |  |

| 8                     | 2        | 1/4            | 01b                          |  |  |  |

| 4                     | 3        | 1/8            | 00b                          |  |  |  |

| 2                     | 4        | 1/16           | 00b                          |  |  |  |

\* CKOUT pin load capacitance = 15 pF

# 6.9. Status Monitor

### 6.9.1. **Transition counter**

The TXCOUNT[3:0] in SFR address 0x14 stores the number of transition to Transmitter-Active mode. Users can check the number by reading SFR. The value is reset to zero when the counter overflows. It is reset by transition to Powerdown mode or by writing any data in the SFR address 0x14.

### 6.9.2. Oscillation status monitor

The S1S77100 has a circuit that detects crystal oscillator amplitude. Detection results are stored in the OSCDET in SFR address 0x14. This function enables stable output clock signals by controlling the start of output from the CKOUT pin based on the detection results.

# 7. SFR (Special Function Register)

# 7.1. SFR List

| Name     | Description                      | Address | Bit7                  | Bit6            | Bit5     | Bit4     | Bit3     | Bit2   | Bit1        | Bit0        | Reset Value |

|----------|----------------------------------|---------|-----------------------|-----------------|----------|----------|----------|--------|-------------|-------------|-------------|

| F1FRAC1  | Freq1 Fractional setting 1       | 0x00    |                       | F1FRAC[15:8]    |          |          |          |        |             |             |             |

| F1FRAC0  | Freq1 Fractional setting 0       | 0x01    |                       | F1FRAC [7:0]    |          |          |          |        |             |             | xxxx xxxx b |

| F2FRAC1  | Freq2 Fractional setting 1       | 0x02    |                       | F2FRAC [15:8]   |          |          |          |        |             |             |             |

| F2FRAC0  | Freq2 Fractional setting 0       | 0x03    | F2FRAC [7:0]          |                 |          |          |          |        |             |             | xxxx xxxx b |

| F1_2INT  | Freq1/Freq2 Integer setting      | 0x04    | F1INT[3:0] F2INT[3:0] |                 |          |          |          |        | xxxx xxxx b |             |             |

| F3FRAC1  | Freq3 Fractional setting 1       | 0x05    | F3FRAC [15:8]         |                 |          |          |          |        |             |             | xxxx xxxx b |

| F3FRAC0  | Freq3 Fractional setting 0       | 0x06    | F3FRAC [7:0]          |                 |          |          |          |        |             |             | xxxx xxxx b |

| F4FRAC1  | Freq4 Fractional setting 1       | 0x07    | F4FRAC [15:8]         |                 |          |          |          |        |             | xxxx xxxx b |             |

| F4FRAC0  | Freq4 Fractional setting 0       | 0x08    | F4FRAC [7:0]          |                 |          |          |          |        |             | xxxx xxxx b |             |

| F3_4INT  | Freq3/Freq4 Integer setting      | 0x09    | F3INT[3:0] F4INT[3:0] |                 |          |          |          |        | xxxx xxxx b |             |             |

| ODIV     | Output Divider Setting           | 0x0A    | FDEV4X                | FDEV2X          | SR1      | [1:0]    | F10DIV   | F2ODIV | F3ODIV      | F40DIV      | xx00 xxxx b |

| FDEV     | FSK Deviation                    | 0x0B    | FDEV[7:0]             |                 |          |          |          |        |             |             | xxxx xxxx b |

| ASKMC0   | ASK Modulation Control 0         | 0x0C    | ASK0 HPWR0 AMH0[5:0]  |                 |          |          |          |        |             | xxxx xxxx b |             |

| ASKMC1   | ASK Modulation Control 1         | 0x0D    | ASK1                  | HPWR1 AMH1[5:0] |          |          |          |        |             | xxxx xxxx b |             |

| ASKMC2   | ASK Modulation Control 2         | 0x0E    | PADUTY[1:0] AML[5:0]  |                 |          |          |          |        |             |             | xxxx xxxx b |

| PARAMP   | ASK Modulation Ramp<br>Control   | 0x0F    | AMRC[7:0]             |                 |          |          |          |        |             |             | xxxx xxxx b |

| FSKRAMP  | FSK Modulation Ramp<br>Control   | 0x10    | FMRC[7:0]             |                 |          |          |          |        |             | xxxx xxxx b |             |

| BRS1     | Bitrate Setting 1                | 0x11    | BRS[7:0]              |                 |          |          |          |        |             | xxxx xxxx b |             |

| BRS2     | Bitrate Setting 2                | 0x12    | CKSRC[2:0]            |                 |          |          | PSC[2:0] |        |             | ASC[1:0]    |             |

| ATUNE    | VDET setting / Antenna<br>Tuning | 0x13    | - VDET[1:0]           |                 |          | ATT[4:0] |          |        |             |             | xxxx xxxx b |

| TXSTAT   | Transmitter Status Register      | 0x14    |                       | TXCOU           | JNT[3:0] |          | OSCDET   | VDETER | VCOCER      | PLLDER      | 0000 x000 b |

| TXCON    | Transmitter Control              | 0x15    | PD                    | PDCK            | FSOFF    | IFSE     | L[1:0]   | -      | -           | PLLEN       | 0000 0xx0 b |

| SPICKSUM | SPI Checksum register            | 0x16    | SPICKSUM[7:0]         |                 |          |          |          |        |             | 0000 0000 b |             |

Note: Do not write values in the addresses not listed above.

Write zero to unidentified bits.

The "Reset Value" shows the values reset when the mode is changed to Powerdown mode. The "x" means that the values are retained and not reset). However, their retention is not guaranteed in Powerdown mode. Write desirable values again in all SFR addresses after exiting from Powerdown mode.

The register types described in the following sections:

- R/W: Read/Write

- R/O: Read only

- W/O: Write only

- R/C: Read only/Write clear

## 7.2. PLL Fractional Setting: Frequency Channel 1

| A .1.1  | Register |      | Bit          |      |      |      |      |      |      |  |  |

|---------|----------|------|--------------|------|------|------|------|------|------|--|--|

| Address | name     | Bit7 | Bit6         | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |  |  |

| 0x00    | F1FRAC1  |      | F1FRAC[15:8] |      |      |      |      |      |      |  |  |

| 0x01    | F1FRAC0  |      | F1FRAC[7:0]  |      |      |      |      |      |      |  |  |

|         | Туре     | R/W  |              |      |      |      |      |      |      |  |  |

| Default |          | 0    | 0            | 0    | 0    | 0    | 0    | 0    | 0    |  |  |

| Bit | Name                        | Function                                                                                                                                                                           |

|-----|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | F1FRAC[15:8]<br>F1FRAC[7:0] | Fractional portion of the feedback divider (N <sub>FRAC</sub> ) of frequency channel 1<br>e.g. If N <sub>FRAC</sub> is $0x1234$ :<br>F1FRAC[15:8] = $0x12$<br>F1FRAC[7:0] = $0x34$ |

# 7.3. PLL Fractional Setting: Frequency Channel 2

| A .1.1  | Register |      | Bit          |      |      |      |      |      |      |  |  |

|---------|----------|------|--------------|------|------|------|------|------|------|--|--|

| Address | name     | Bit7 | Bit6         | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |  |  |

| 0x02    | F2FRAC1  |      | F2FRAC[15:8] |      |      |      |      |      |      |  |  |

| 0x03    | F2FRAC0  |      | F2FRAC[7:0]  |      |      |      |      |      |      |  |  |

|         | Туре     |      | R/W          |      |      |      |      |      |      |  |  |

| Default |          | 0    | 0            | 0    | 0    | 0    | 0    | 0    | 0    |  |  |

| Bit | Name                        | Function                                                                                                                                                                                                                        |

|-----|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | F2FRAC[15:8]<br>F2FRAC[7:0] | $ \begin{array}{l} \mbox{Fractional portion of the feedback divider (N_{FRAC}) of frequency channel 2} \\ \mbox{e.g. If } N_{FRAC} \mbox{ is } 0x5678: \\ \mbox{F2FRAC}[15:8] = 0x56 \\ \mbox{F2FRAC}[7:0] = 0x78 \end{array} $ |

## 7.4. PLL Integer Setting: Frequency Channel 1 and 2

| A .1.1  | Register |      | Bit  |        |      |            |      |      |      |  |

|---------|----------|------|------|--------|------|------------|------|------|------|--|

| Address | name     | Bit7 | Bit6 | Bit5   | Bit4 | Bit3       | Bit2 | Bit1 | Bit0 |  |

| 0x04    | F1_2INT  |      | F1IN | Г[3:0] |      | F2INT[3:0] |      |      |      |  |

| ,       | Type R   |      |      |        | R/W  |            |      |      |      |  |

| Default |          | 0    | 0    | 0      | 0    | 0          | 0    | 0    | 0    |  |

| Bit     | Name                                                       | Function                                                                   |                                                                                   |         |  |  |  |  |  |  |  |

|---------|------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------|--|--|--|--|--|--|--|