| ITEM: Limitation of chang                     | ing RDWAIT sett                                                                                                                                                                                                                                                            | ings                                                                                      |       |  |  |  |  |  |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------|--|--|--|--|--|

| Object manuals                                | Document codes                                                                                                                                                                                                                                                             | Items                                                                                     | Pages |  |  |  |  |  |

| S1C31W65 Technical Manual                     | 414063300                                                                                                                                                                                                                                                                  | 4.8 Control Register                                                                      | 4-10  |  |  |  |  |  |

| S1C31W73 Technical Manual                     | 414076300                                                                                                                                                                                                                                                                  | 4.9 Control Register                                                                      | 4-11  |  |  |  |  |  |

| S1C31W74 Technical Manual                     | 413374500                                                                                                                                                                                                                                                                  | 4.9 Control Register                                                                      | 4-10  |  |  |  |  |  |

| S1C31D01 Technical Manual                     | 413520400                                                                                                                                                                                                                                                                  | 4.8 Control Register                                                                      | 4-12  |  |  |  |  |  |

| S1C31D50/D51                                  | 413699403                                                                                                                                                                                                                                                                  | 4.8 Control Register                                                                      | 4-10  |  |  |  |  |  |

| Technical Manual                              |                                                                                                                                                                                                                                                                            |                                                                                           |       |  |  |  |  |  |

| FLASHC Flash Read Cyc<br>Bits 1-0 RDWAIT[1:0] | Note: Be sure to set the FLASHCWAIT.RDWAIT[1:0] bits before the system clock is configured.<br>(Correct) Control Register<br>FLASHC Flash Read Cycle Register<br>Bits 1-0 RDWAIT[1:0]<br>These bits set the number of bus access cycles for reading from the Flash memory. |                                                                                           |       |  |  |  |  |  |

|                                               | etting of the FLAS<br>ctions immediately<br>DWAIT = 1;                                                                                                                                                                                                                     | AIT[1:0] bits before the system clock<br>HCWAIT.RDWAIT [1: 0] bits from 0:<br>after that. | •     |  |  |  |  |  |

| Document codes | Items                                            | Pages                                                                                                                                                                                                                                                       |

|----------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 414063300      | 10.4.2 Real-Time Clock Counter<br>Operations     | 10-4                                                                                                                                                                                                                                                        |

| 414076300      | 10.4.2 Real-Time Clock Counter<br>Operations     | 10-4                                                                                                                                                                                                                                                        |

| 413374500      | 10.4.2 Real-Time Clock Counter<br>Operations     | 10-4                                                                                                                                                                                                                                                        |

| 413520400      | 10.4.2 Real-Time Clock Counter<br>Operations     | 10-4                                                                                                                                                                                                                                                        |

| 413699403      | 10.4.2 Real-Time Clock Counter<br>Operations     | 10-4                                                                                                                                                                                                                                                        |

| -              | 414063300<br>414076300<br>413374500<br>413520400 | 41406330010.4.2 Real-Time Clock Counter<br>Operations41407630010.4.2 Real-Time Clock Counter<br>Operations41337450010.4.2 Real-Time Clock Counter<br>Operations41352040010.4.2 Real-Time Clock Counter<br>Operations41369940310.4.2 Real-Time Clock Counter |

### (Error)

### Corrective operation when a value out of the effective range is set

When a value out of the effective range is set to the year, day of the week, or hour (in 24H mode) counter, the counter will be cleared to 0 at the next count-up timing. When a such value is set to the month, day, or hour (in 12H mode) counter, the counter will be set to 1 at the next count-up timing.

### (Correct)

### Corrective operation when a value out of the effective range is set

When a value out of the effective range is set to the year, day of the week, or hour (in 24H mode) counter, the counter will be cleared to 0 at the next count-up timing <u>of the counter</u>. When a such value is set to the month, day, or hour (in 12H mode) counter, the counter will be set to 1 at the next count-up timing <u>of the counter</u>.

Note: <u>RTCMON.RTCMOH bits=0 & RTCMON.RTCMOL[3:0] bits=0x0 are prohibited.</u>

| ITEM: Real-Time Clock (RTCA) Theoretical Regulation Function |                |                    |             |            |       |  |

|--------------------------------------------------------------|----------------|--------------------|-------------|------------|-------|--|

| Object manuals                                               | Document codes | Items              |             |            | Pages |  |

| S1C31W74 Technical Manual                                    | 413374500      | 10.3.2<br>Function | Theoretical | Regulation | 10-2  |  |

| S1C31D01 Technical Manual                                    | 413520400      | 10.3.2<br>Function | Theoretical | Regulation | 10-2  |  |

|                                                              |                |                    |             |            |       |  |

|                                                              |                |                    |             |            |       |  |

|                                                              |                |                    |             |            |       |  |

(Error)

## **10.3.2 Theoretical Regulation Function**

The time-of-day clock loses accuracy if the OSC1 frequency fosc1 has a frequency tolerance from 32.768 kHz. To correct this error without changing any external part, RTCA provides a theoretical regulation function. Follow the procedure below to perform theoretical regulation.

1. Measure the frequency tolerance "m  $[\mbox{ppm}]$  " of fosc1.

2. Determine the theoretical regulation execution cycle time "n seconds."

3. Determine the value to be written to the RTCCTL.RTCTRM[6:0] bits from the results in Steps 1 and 2.

4. Write the value determined in Step 3 to the RTCCTL.RTCTRM[6:0] bits periodically in n-second cycles using an RTCA alarm or second interrupt.

5. Monitor the RTC1S signal to check that every n-second cycle has no error included.

The correction value for theoretical regulation can be specified within the range from -64 to +63 and it should be written to the RTCCTL.RTCTRM[6:0] bits as a two's-complement number. Use Eq. 9.1 to calculate the correction value.

n: Theoretical regulation execution cycle time [second] (time interval to write the correct value to the RTCCTL.

RTCTRM[6:0] bits periodically via software)

m: OSC1 frequency tolerance [ppm]

### (Correct)

### **10.3.2 Theoretical Regulation Function**

The time-of-day clock loses accuracy if the OSC1 frequency fosc1 has a frequency tolerance from 32.768 kHz. To correct this error without changing any external part, RTCA provides a theoretical regulation function. Follow the procedure below to perform theoretical regulation.

1. Determine the correction value of frequency tolerance "m [ppm] =- {(fOSC1-32768[Hz]) /

32768[Hz]}×10<sup>6</sup>" by measuring the fosc1.

2. Determine the theoretical regulation execution cycle time "n seconds."

3. Determine the value to be written to the RTCCTL.RTCTRM[6:0] bits from the results in Steps 1 and 2.

4. Write the value determined in Step 3 to the RTCCTL.RTCTRM[6:0] bits periodically in n-second cycles using an RTCA alarm or second interrupt.

5. Monitor the RTC1S signal to check that every n-second cycle has no error included.

The correction value for theoretical regulation can be specified within the range from -64 to +63 and it should be written to the RTCCTL.RTCTRM[6:0] bits as a two's-complement number. Use Eq. 9.1 to calculate the correction value.

n: Theoretical regulation execution cycle time [second] (time interval to write the correct value to the RTCCTL.

RTCTRM[6:0] bits periodically via software)

m: OSC1's correction value of frequency tolerance [ppm]

| ITEM: LCD Driver Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ons                                                               |                                                                                                                                                                    |                              |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--|--|--|--|

| Object manuals                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Document codes                                                    | Items                                                                                                                                                              | Pages                        |  |  |  |  |

| S1C31W74 Technical Manual                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 413374500                                                         | 20.5.2 Display On/Off                                                                                                                                              | 20-8                         |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                   |                                                                                                                                                                    |                              |  |  |  |  |

| (Error)                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                   |                                                                                                                                                                    |                              |  |  |  |  |

| all set to VSS level. Since "Al<br>LCD driver, data in the displa<br>drive for "All on" and to static                                                                                                                                                                                                                                                                                                                                                                         | II on" and "All off"<br>by data RAM is no<br>drive for "All off." | e supply stops and the LCD driver pin<br>directly control the driving waveform<br>t altered. The common pins are set to<br>flash on and off without altering the d | output by the<br>dynamic     |  |  |  |  |

| (Correct)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                   |                                                                                                                                                                    |                              |  |  |  |  |

| When "Display off" is selected, the drive voltage supply stops and the LCD driver pin outputs are<br>all set to VSS level. Since "All on" and "All off" directly control the driving waveform output by the<br>LCD driver, data in the display data RAM is not altered. The common pins are set to dynamic<br>drive for "All on" and to static drive for "All off."<br>This function can be used to make the display flash on and off without altering the display<br>memory. |                                                                   |                                                                                                                                                                    |                              |  |  |  |  |

| As a workaround, there is a terminal. Consider the load c                                                                                                                                                                                                                                                                                                                                                                                                                     | means to insert a<br>apacitance and op<br>er, if a resistor is    | fluctuation in LCD panel load at high<br>a resistor between the VC2 terminal<br>perating temperature of the LCD pane<br>inserted between the VC2 terminal          | and the VC1<br>el and decide |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                   |                                                                                                                                                                    |                              |  |  |  |  |

| ITEM: Fla                            | sh Memory F          | Pin |         |              |                                                                                         |            |  |  |

|--------------------------------------|----------------------|-----|---------|--------------|-----------------------------------------------------------------------------------------|------------|--|--|

| Object manuals D                     |                      |     | Docume  | nt codes     | Items                                                                                   | Pages      |  |  |

| S1C31W74 Technical Manual            |                      |     | 4133745 | 00           | 1.3.3 Pin Descriptions                                                                  | 1-8        |  |  |

|                                      |                      |     |         |              | 4.3.1 Flash Memory Pin                                                                  | 4-2        |  |  |

|                                      |                      |     |         |              | 24 Basic External Connection Diagram                                                    | 24-1       |  |  |

| (Error)                              |                      |     |         |              |                                                                                         |            |  |  |

| 1.3.3 Pin [                          | Descriptions         |     |         |              |                                                                                         |            |  |  |

| L                                    | , -                  |     | Т       | able 1.3.3   | 1 Pin Description                                                                       |            |  |  |

| P26                                  | P26                  | I/O | Hi-Z    | -            | I/O port                                                                                |            |  |  |

|                                      | EXOSC                |     |         |              | Clock generator external clock input                                                    |            |  |  |

| 4.3.1 Flasl                          | h Memory Pin         | Ì   | Tab     | 00/211       | Flash Memory Pin                                                                        |            |  |  |

| Pin na                               | ame                  | I/O |         | itial status | Flash Memory Pin<br>Function                                                            |            |  |  |

| VPP                                  |                      | P   |         | -            | Flash programming power supply                                                          |            |  |  |

| 24 Basic External Connection Diagram |                      |     |         |              |                                                                                         |            |  |  |

| (Correct)                            |                      |     |         |              |                                                                                         |            |  |  |

| 1.3.3 Pin [                          | Descriptions         |     | _       |              |                                                                                         |            |  |  |

| L                                    |                      |     |         | able 1.3.3   | 1 Pin Description                                                                       |            |  |  |

| P26                                  | P26 (ENVPP)<br>EXOSC | I/O | Hi-Z    | -            | I/O port (Flash programming control signal outp<br>Clock generator external clock input | <u>ut)</u> |  |  |

|                                      |                      |     |         |              |                                                                                         |            |  |  |

| .3.1 Flash Memo       | 2                  | Table 4.3.1.1 Fla | ash Memory Pin                                        |

|-----------------------|--------------------|-------------------|-------------------------------------------------------|

| Pin name              | I/O                | Initial status    | Function                                              |

| Vpp                   | Р                  | _                 | Flash programming power supply                        |

| (ENVPP)               | <u>O or Hi-Z</u>   | <u>Hi-Z</u>       | Flash programming control signal output               |

| trical Characteristic | s" chapter.        |                   | onditions, Flash programming voltage VPP" in the "Ele |

| 4 Basic External      | Connection Dia     | gram              |                                                       |

|                       | <u>EN\</u><br>#RES | WD<br>/PP         | VDD<br>RDBG2<br>Debugging<br>tool                     |

|                       |                    |                   |                                                       |

| ITEM Flash Programming    |               |                                       |        |  |  |  |

|---------------------------|---------------|---------------------------------------|--------|--|--|--|

| Object manual             | Document code | item                                  | Page   |  |  |  |

| S1C31W74 Technical Manual | 413374500     | 1.1 Features                          | 1-2    |  |  |  |

|                           |               | 4.3.3 Flash Programming               | 4-2    |  |  |  |

|                           |               | 23.2 Recommended Operating Conditions | 23-1   |  |  |  |

|                           |               | 24 Basic External Connection Diagram  | 24-1   |  |  |  |

|                           |               | Appendix C Mounting Precautions       | AP-C-1 |  |  |  |

(Error)

#### 1.1 Features

| Power supply voltage                          |                                                          |  |  |  |

|-----------------------------------------------|----------------------------------------------------------|--|--|--|

| VDD operating voltage                         | 1.8 to 3.6 V                                             |  |  |  |

| VDD operating voltage for Flash programming   | 2.7 to 3.6 V (when the internal voltage booster is used) |  |  |  |

| VDD operating voltage when LCD driver is used | 2.5 to 3.6 V                                             |  |  |  |

### 4.3.3 Flash Programming

The Flash memory supports on-board programming, so it can be programmed using a flash loader.

The VPP voltage can be supplied from either an external power supply or the internal voltage booster.

Choose the flash loader according to the VPP power supply to be used.

Notes: When the internal voltage booster is used, 2.7 V or more VDD voltage is required.

#### 23.2 Recommended Operating Conditions

| Item                          | Symbol | Condition                | Min. | Тур. | Max. | Unit |

|-------------------------------|--------|--------------------------|------|------|------|------|

| Power supply voltage          | VDD    | For normal operation     | 1.8  | -    | 3.6  | V    |

|                               |        | For Flash programming    | 2.7  | -    | 3.6  | V    |

|                               |        | For LCD driver operation | 2.5  | -    | 3.6  | V    |

| Capacitor between Vss and VPP | CVPP   | *5                       | -    | 0.1  | -    | μF   |

\*5 CVPP should be connected only when the VPP voltage is not stable.

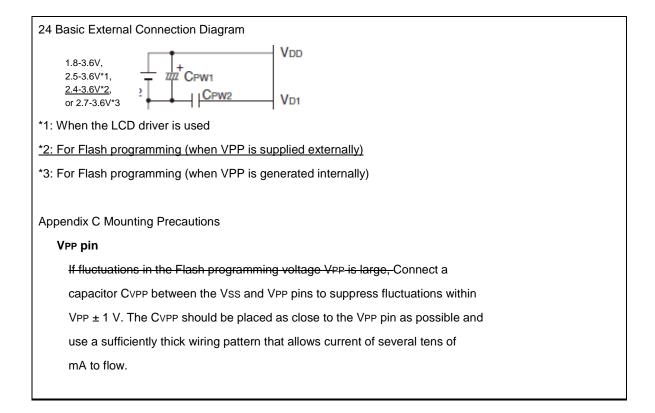

24 Basic External Connection Diagram

VDD 1.8–3.6 V, 2.5–3.6 V \*1, or 2.7–3.6 V \*2 1.8-3.6 V, V<sub>D1</sub>

\*1: When the LCD driver is used

\*2: For Flash programming (when VPP is generated internally)

Appendix C Mounting Precautions

#### VPP pin

If fluctuations in the Flash programming voltage VPP is large, connect a capacitor CVPP between the Vss and VPP pins to suppress fluctuations within VPP  $\pm$  1 V. The CVPP should be placed as close to the VPP pin as possible and use a sufficiently thick wiring pattern that allows current of several tens of mA to flow.

#### (Correct)

1.1 Features

| Power supply voltage                                                                       |                                                 |  |

|--------------------------------------------------------------------------------------------|-------------------------------------------------|--|

| VDD operating voltage                                                                      | 1.8 to 3.6 V                                    |  |

| VDD operating voltage for Flash programming 2.4 to 3.6 V (when VPP is supplied externally) |                                                 |  |

|                                                                                            | 2.7 to 3.6 V (when VPP is generated internally) |  |

| VDD operating voltage when LCD driver is used                                              | 2.5 to 3.6 V                                    |  |

#### 4.3.3 Flash Programming

The Flash memory supports on-board programming, so it can be programmed using a flash loader.

The VPP voltage can be supplied from either an external power supply or the internal voltage booster.

The VPP voltage can also be generated by the internal power supply for generating the Flash programming

voltage. Be sure to connect a capacitor CVPP between the Vss and VPP pins for stabilizing the voltage

when the VPP voltage is supplied externally or for generating the voltage when the internal power supply is used.

The VPP pin must be left open except when programming the Flash memory. However, it is not necessary

to disconnect the wire when using "Bridge Board (S5U1C31001L)" to supply the VPP voltage,

as Bridge Board controls the power supply so that it will be supplied during Flash programming only.

Notes: When the VPP voltage is supplied externally, 2.4 V or more VDD voltage is required.

· When the VPP voltage is generated internally, 2.7 V or more VDD voltage is required

• Be sure to avoid using the VPP pin output for driving external circuits when the VPP voltage is generated internally.

23.2 Recommended Operating Conditions

| ltem                          | Symbol |                      | Condition                        | Min. | Тур. | Max        | Unit |

|-------------------------------|--------|----------------------|----------------------------------|------|------|------------|------|

| Power supply voltage          | VDD    | For normal operation |                                  | 1.8  | -    | 3.6        | V    |

|                               |        | For Flash            | When VPP is supplied externally  | 2.4  | -    | <u>3.6</u> | V    |

|                               |        | programming          | When VPP is generated internally | 2.7  | -    | 3.6        | V    |

|                               |        | For LCD driver of    | operation                        | 2.5  | -    | 3.6        | V    |

| Capacitor between VSS and VPP | CVPP   | <u>*5</u>            |                                  | -    | 0.1  | -          | μF   |

\*5 CVPP should be connected only when the VPP voltage is not stable.